Bootstrap sampling switch circuit, sample hold circuit and analog-to-digital converter

A bootstrap sampling switch, circuit technology, applied in the direction of analog-to-digital converter, analog-to-digital conversion, code conversion, etc., can solve the problem of long rise and fall time of the output clock

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

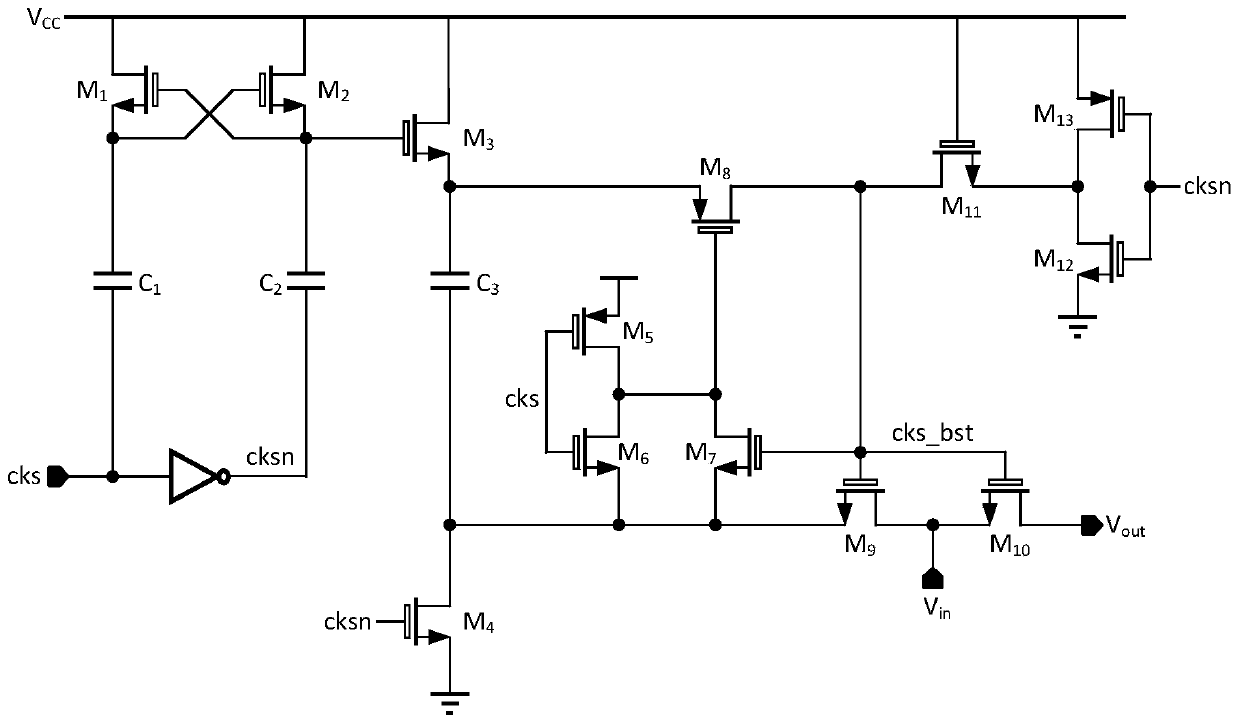

[0041] Figure 4 A bootstrap sampling switch circuit of this embodiment is shown. The bootstrap switch circuit includes: a voltage regulator 11 , a level shift circuit 12 and a bootstrap main circuit 13 .

[0042] The voltage regulator 11 is used to generate a first voltage Vdd_1p4 and a second voltage Vss_Op4, the first voltage Vdd_1p4 is equal to the common mode voltage VCM plus a third voltage, and the second voltage Vss_Op4 is equal to the common mode voltage VCM minus the third voltage , the third voltage is equal to half of the withstand voltage value of the low-voltage thin grid tube.

[0043] The level shift circuit 12 uses the first voltage Vdd_1p4 as a power supply voltage to generate a clock cks, the high level of the clock cks is equal to the first voltage Vdd_1p4, and the low level of the clock cks is equal to the the second voltage Vss_Op4.

[0044] The bootstrap main circuit 13 uses the first voltage Vdd_1p4 as the power supply voltage and the second voltage ...

Embodiment 2

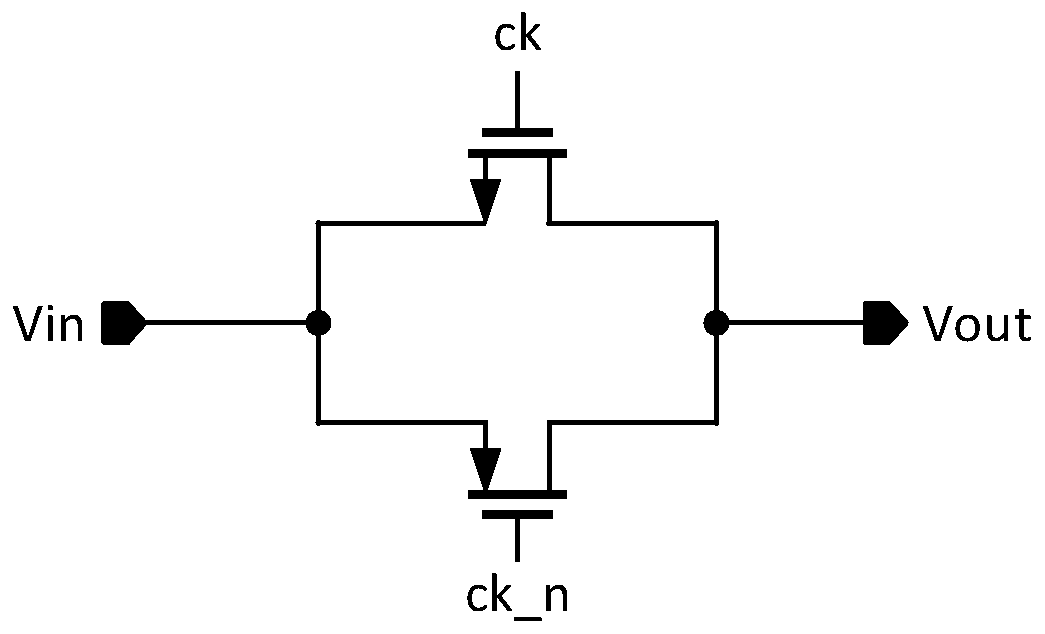

[0066] This embodiment provides a sample-and-hold circuit for an analog-to-digital converter. The sample-and-hold circuit includes a switch tube and the bootstrap sampling switch circuit in Embodiment 1. The clock cks generated by the bootstrap sampling switch circuit is used for control the switching tube. For example, the sample-and-hold circuit can use figure 1 In the circuit in the sampling process, the clock cks generated by the bootstrap sampling switching circuit controls the switch S2, and the switch S2 is realized by the switching tube Ms.

Embodiment 3

[0068] This embodiment provides an analog-to-digital converter, and the analog-to-digital converter includes the sample-and-hold circuit in Embodiment 2. Of course, in addition to the sample-and-hold circuit, the analog-to-digital converter may also include related circuits in other existing analog-to-digital converters.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More