High-speed high-efficiency high-voltage half-bridge gate drive circuit

A gate drive circuit and output drive circuit technology, which is applied in the field of high-speed, high-efficiency, high-voltage half-bridge gate drive circuits, can solve the problems of reducing the switching frequency of the system, increasing the damage of the switch, and increasing the driving delay.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0049] The present invention will be described in further detail below in conjunction with the accompanying drawings and examples.

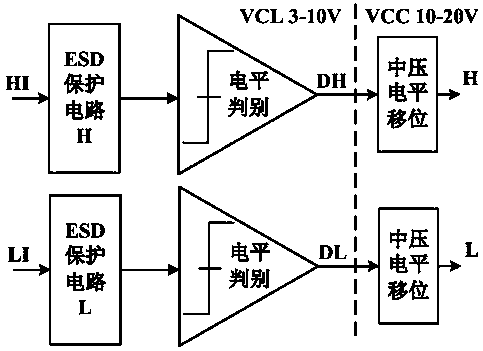

[0050] figure 1 It is a structural block diagram of a high-speed, high-efficiency, high-voltage half-bridge gate drive circuit of the present invention. The high-speed and high-efficiency high-voltage half-bridge gate drive circuit includes an input receiving circuit, a dead-time generating circuit, a low-voltage generating circuit, a low-side delay circuit, a low-side high-efficiency output drive circuit L, and a low-delay high-voltage level shift circuit And high-side high-efficiency output drive circuit H.

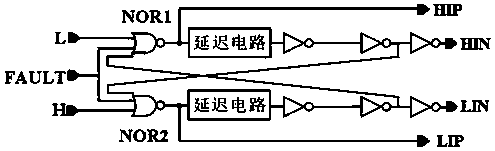

[0051] Among them, the low-voltage digital input signals HI and HI first enter the input receiving circuit, and perform signal level discrimination and logic level high-voltage conversion to obtain medium-voltage signals H and L; the dead-time generation circuit obtains high-side differential input according to the medium-voltage signal H...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More