Lateral device and preparation method for reducing influence of high-voltage interconnection

A lateral device, high-voltage technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of device breakdown and the difficulty of complete depletion of the drift region, so as to improve the breakdown voltage and enhance the depletion capability. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

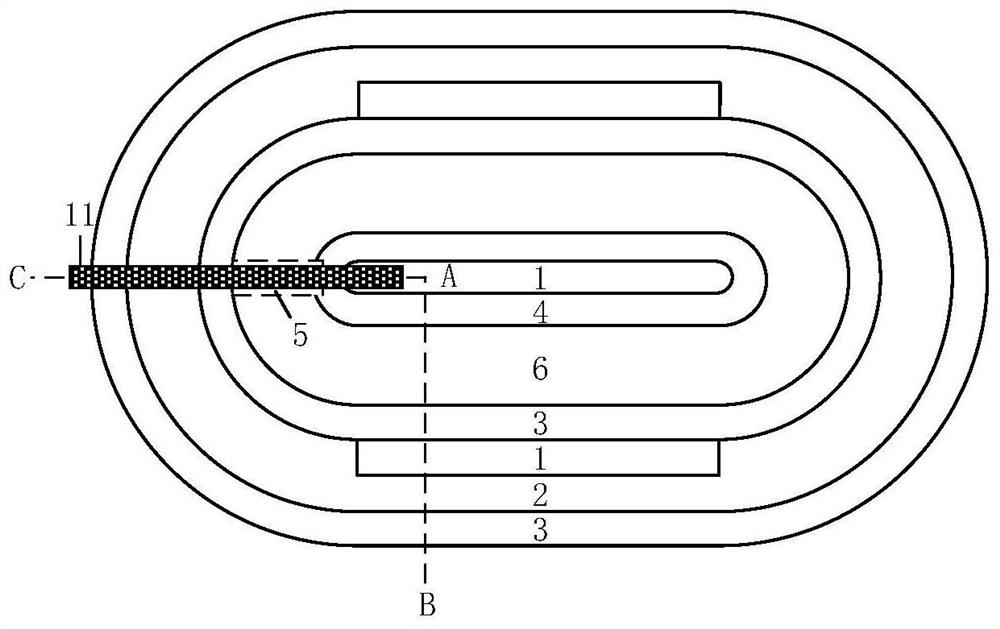

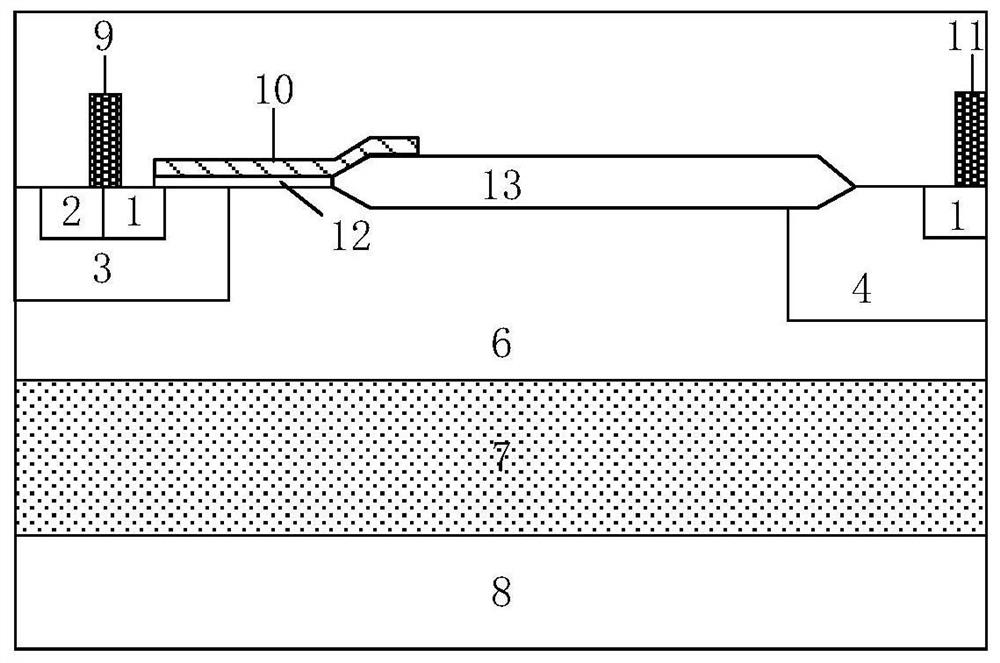

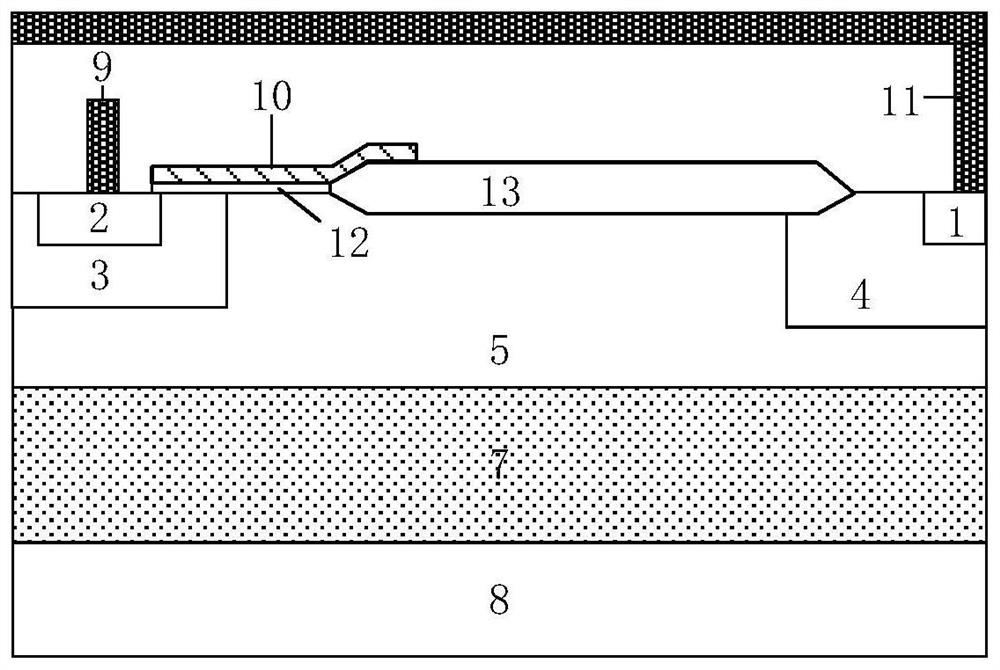

[0032] This embodiment provides a lateral device that reduces the influence of high-voltage interconnection, including a non-high-voltage interconnection structure and a high-voltage interconnection structure; the non-high-voltage interconnection structure is as follows figure 1 As shown in the cross-section of the AB line, the structure of the high-voltage interconnection area is as follows figure 1 The cross-section of the AC line in the center is shown;

[0033] The non-high-voltage interconnection region structure includes a second-type impurity-doped substrate 8, an insulating buried layer 7 formed on the second-type impurity-doped substrate 8, and a first-type impurity-doped epitaxial layer formed on the insulating buried layer 7. 6. On the left side of the first-type doped impurity epitaxial layer 6, a second-type doped impurity well region 3 is formed by ion implantation, and the first-type doped surface heavily doped inside the second-type doped impurity well region 3...

Embodiment 2

[0050] like Figure 4 As shown, the difference between this embodiment and Embodiment 1 is: when the first type doped impurity well region 4 is a first type doped impurity contact region 1, the lateral high voltage device is a lateral diffused metal oxide field When the effect transistor (LDMOS) is replaced by the second type doped impurity collector region 2, the lateral high voltage device is a lateral insulated gate bipolar transistor (LIGBT).

Embodiment 3

[0052] like Figure 5 As shown, the difference between this embodiment and Embodiment 1 is: the structure is an SOI structure, and this structure is a bulk silicon structure.

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More