Preparation method of solder micro-bump array

A technology of solder bumps and micro-bumps, which is applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc. simple effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

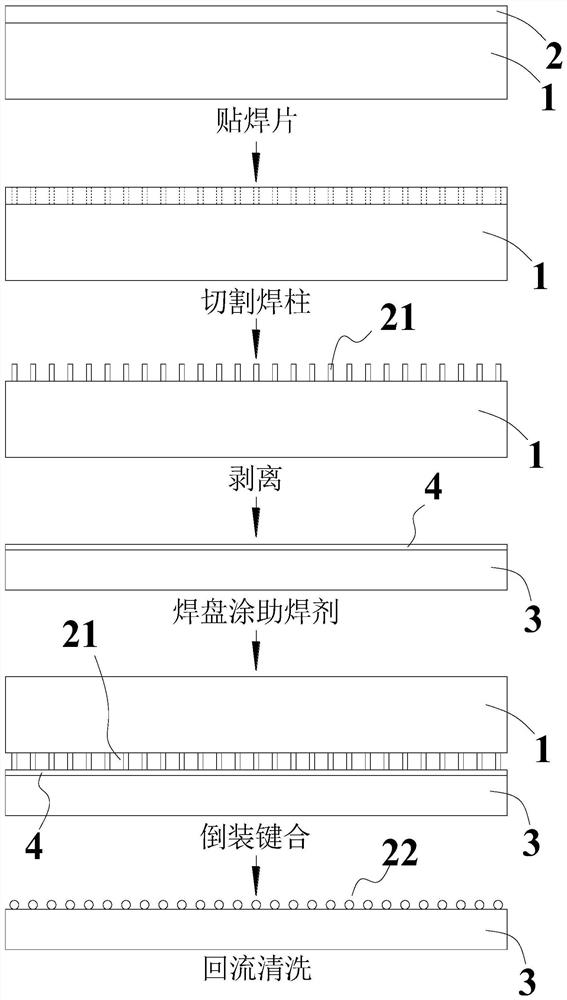

[0038] A method for preparing a solder micro-bump array, comprising the steps of:

[0039] Before step s1, the raw materials need to be processed, that is, the required model and thickness of the solder sheet 2 should be prepared, cut to the required size, to ensure that the solder sheet is flat, and if necessary, it can be leveled to prepare the required Carrier plate 1 of shape and size, cleaning the surface.

[0040] s1. Paste solder tabs:

[0041] Such as figure 1 As shown, attach the solder piece 2 to the carrier board 1; specifically, apply the adhesive on the clean carrier board 1, spread the glue fully and evenly by high-speed spinning or scraping, and place the flat solder piece 2 Attached to carrier board 1.

[0042] Solder piece 2 adopts commonly used Sn-based, Pb-based, In-based, AuSn solder pieces, such as Sn 50 In 50 , Sn 43 Pb 43 Bi 14 , Sn 62 Pb 36 Ag 2 , Sn 63 Pb 37 , SAC305, Sn 90 Sb 10 , Pb 90 sn 10 、Au 80 sn 20 Wait. According to the siz...

Embodiment 2

[0060] s1. Paste solder tabs:

[0061] Apply 502 glue adhesive on the clean glass carrier, spread the glue fully and evenly by spinning the glue at a high speed, the speed is 2000rpm, and the time is 30s. The thickness of the formed glue is 30-50μm, and the leveled Pb with a thickness of 100μm 63 sn 37 The solder tabs are attached to the glass carrier.

[0062] s2. Cutting:

[0063] Cut out a 10*10 array of solder columns on the solder sheet according to the design pattern with a UV laser processing equipment with a laser power of 10W. The laser power is set to 70%, the frequency is 35KHz, the marking speed is 300mm / s, and the diameter of the processed solder column is 100μm .

[0064] s3, stripping:

[0065] Use tweezers to tear off the excess solder sheet as a whole, leaving only the array of solder posts, and inspect the array of solder posts under a microscope.

[0066] s4. Flip-chip welding:

[0067] Brush a layer of flux on the surface of the chip pad, and use a f...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More