Patents

Literature

67results about How to "Strong process compatibility" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

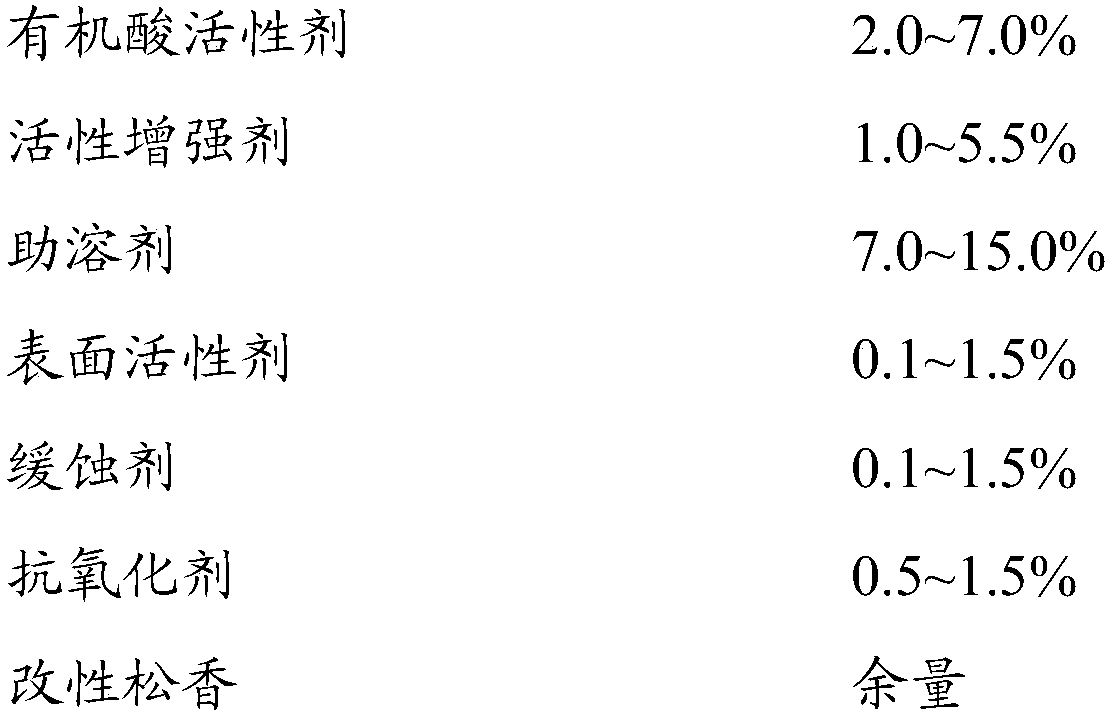

Scaling powder for nickel-plating alloy soft soldering tin wire core and preparation method of scaling powder

InactiveCN102728967AEasy to absorb moistureLower the resistance valueWelding/cutting media/materialsSoldering mediaOrganic acidActive agent

The invention discloses a scaling powder for a nickel-plating alloy soft soldering tin wire core and the preparation method of the scaling powder. The weight formula of the scaling powder comprises the following components by weight percent: 60-90% of resin, 0.1-20% of organic acid, 0.1-10% of organic amine, 0.1-20% of metal salt, 0.1-2.0% of active strengthening agent, 0.1-2.0% of surfactant, 0.1-1.0% of corrosion inhibitor and 0.1-1.0% of antioxidant. The scaling powder disclosed by the invention is suitable for producing lead-containing or non-lead solder tin wire containing scaling powder and can be used for automatically welding or manually welding nickel-plate alloy; and when in use, the welding time of the tin wire is short, the wettability is good and the welding residues are few, so that the scaling powder belongs to environment-friendly scaling powder, and the tensile strength of the welding point joint is high and the insulating resistance is large. The tin wire prepared by the invention is very suitable for soft soldering of nickel-plate alloy and is suitable for soft soldering of chromium plating, gold plating, copper and copper alloy.

Owner:SOUTH CHINA UNIV OF TECH +1

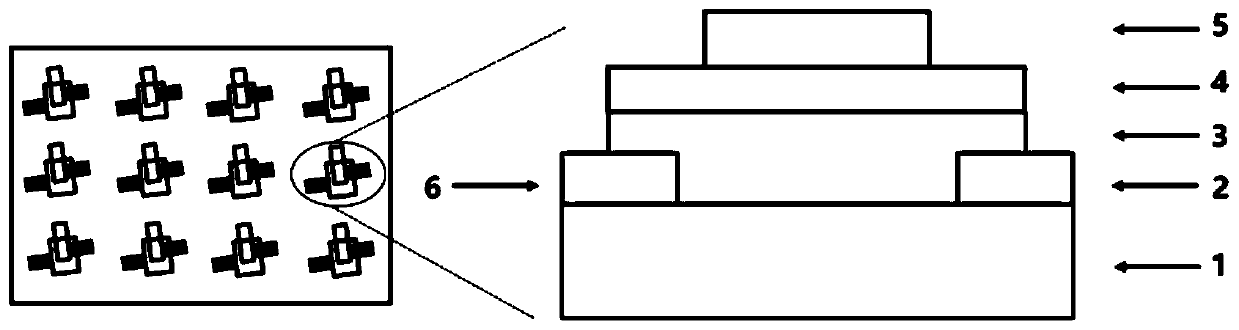

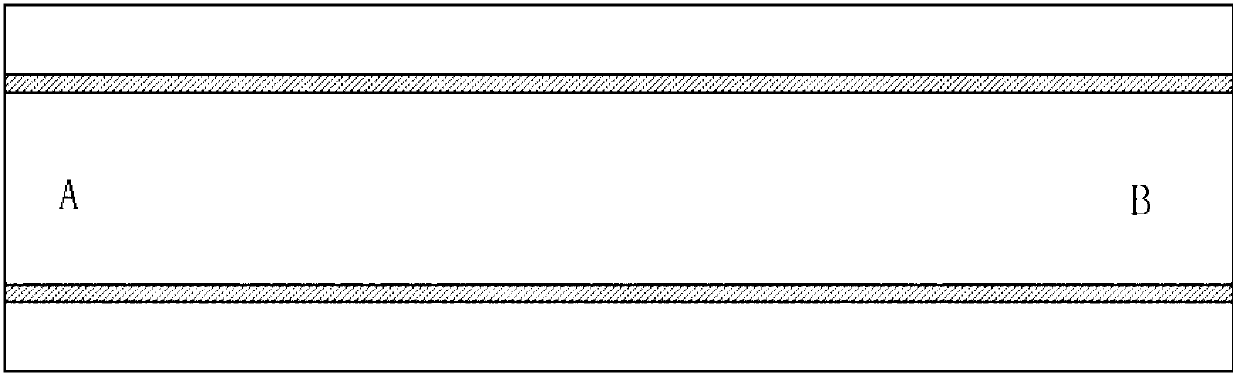

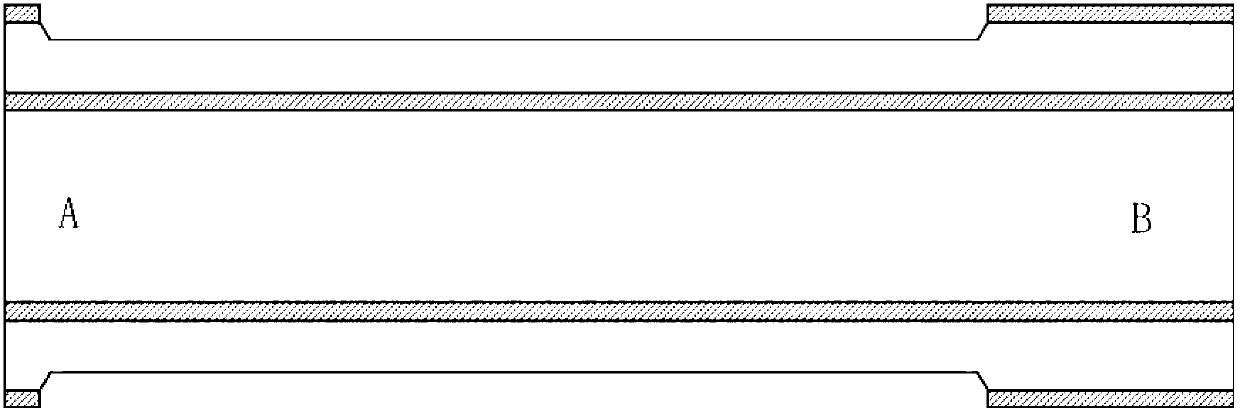

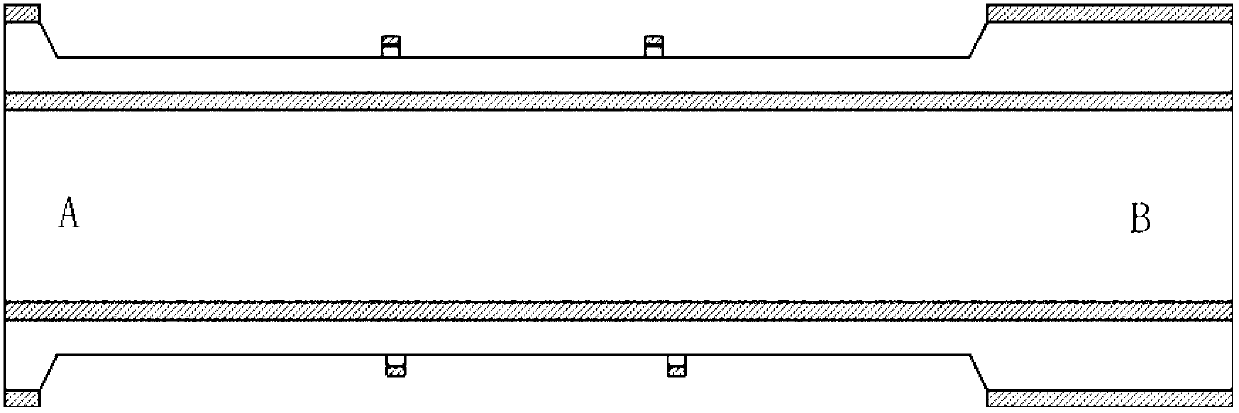

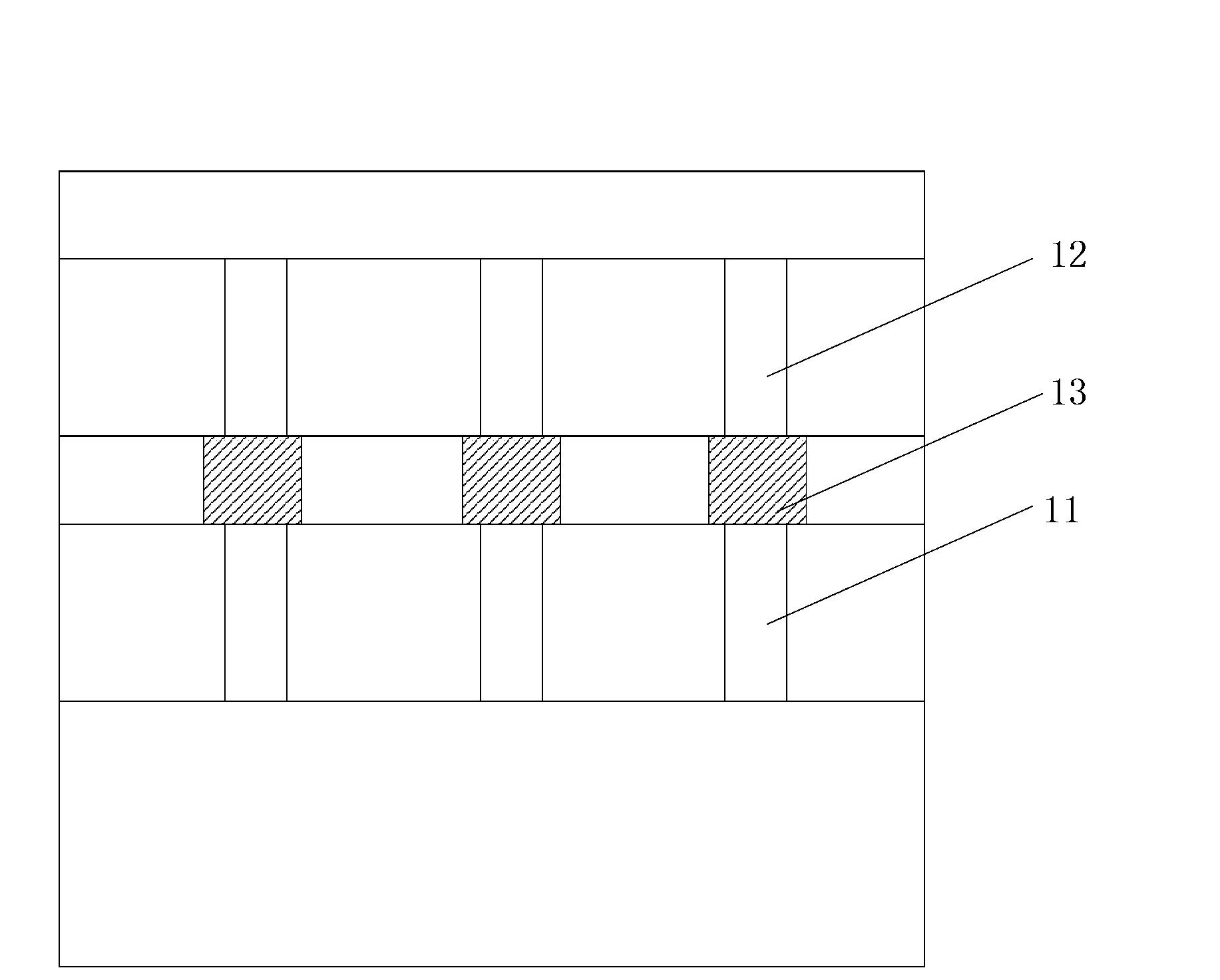

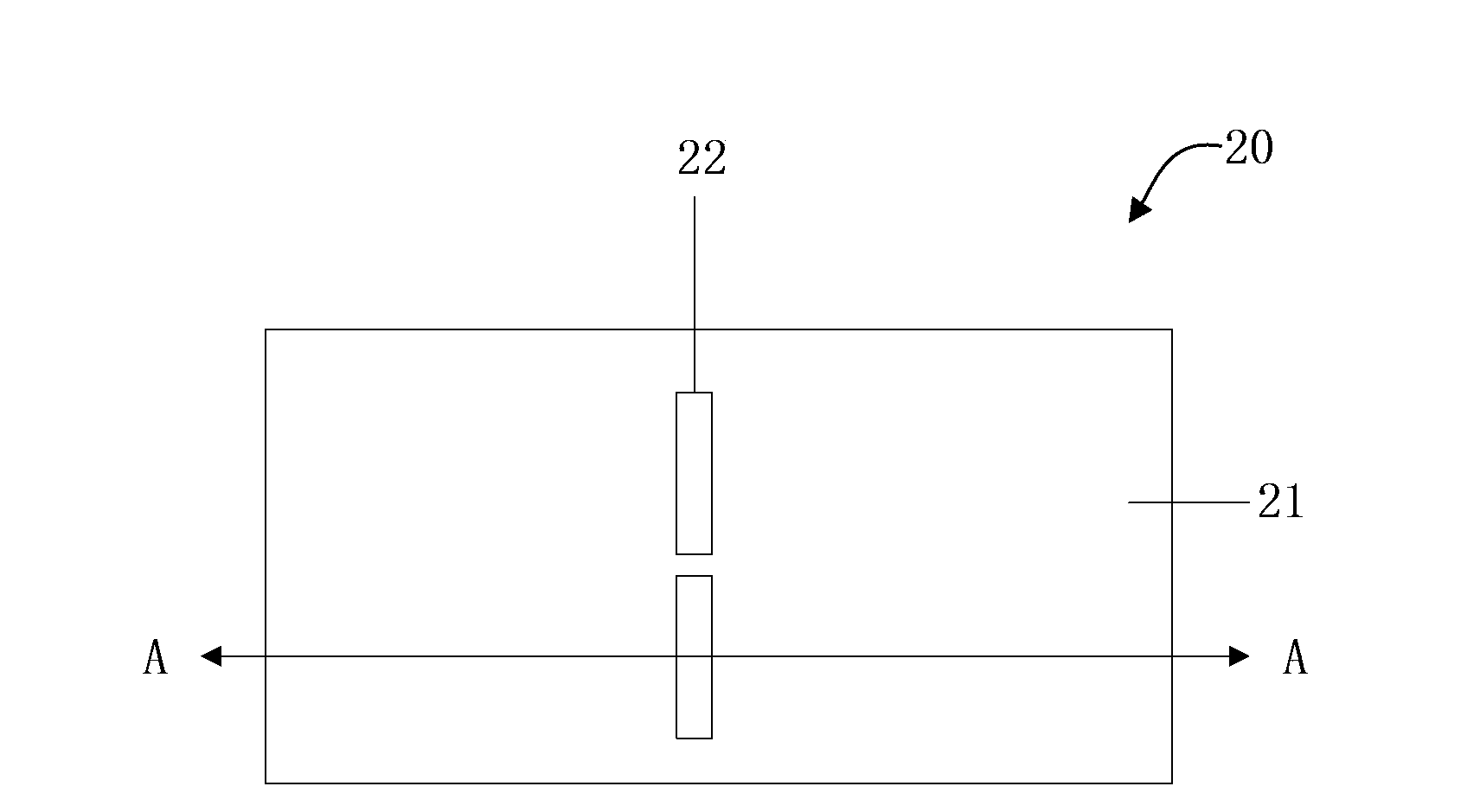

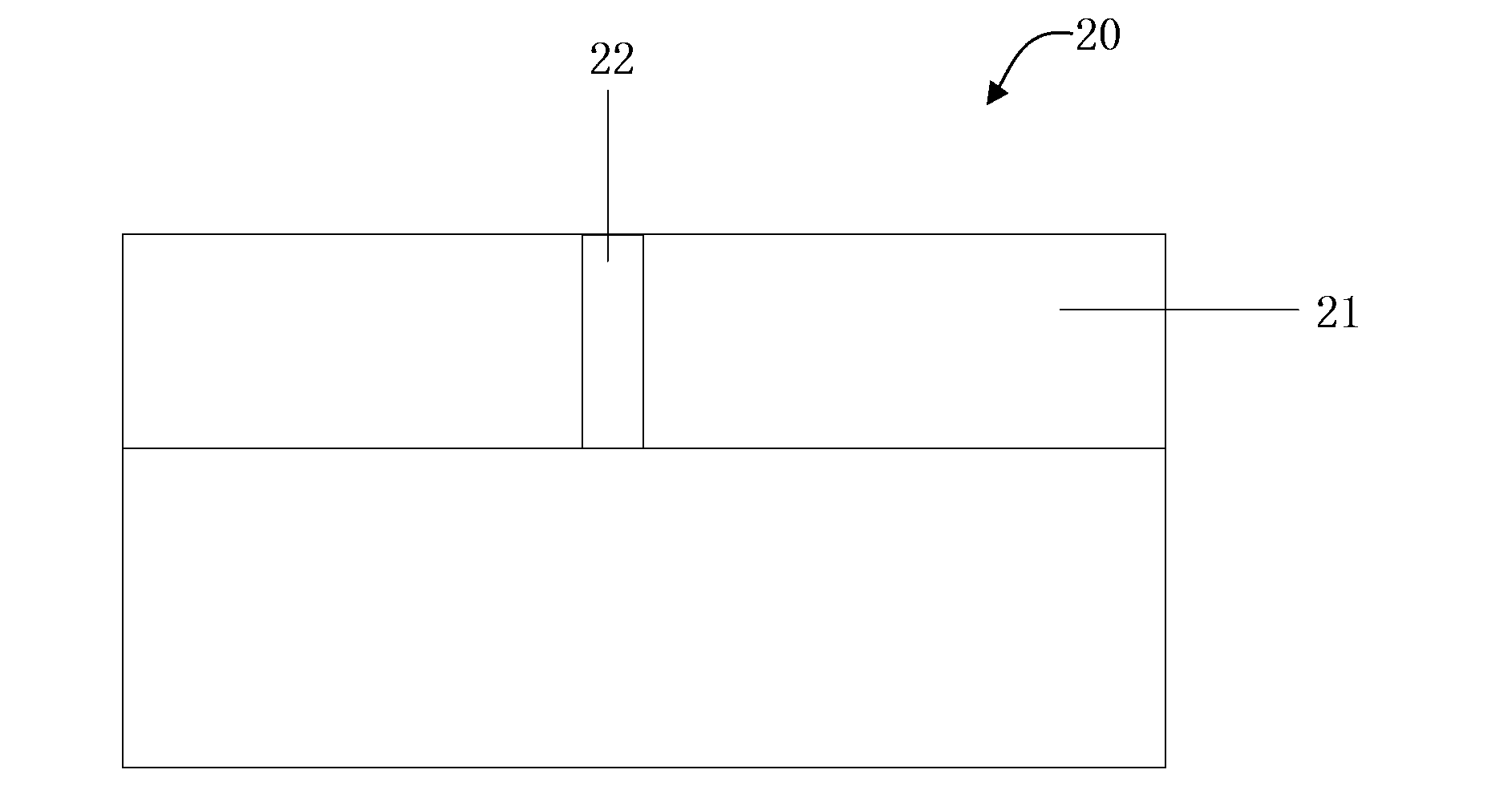

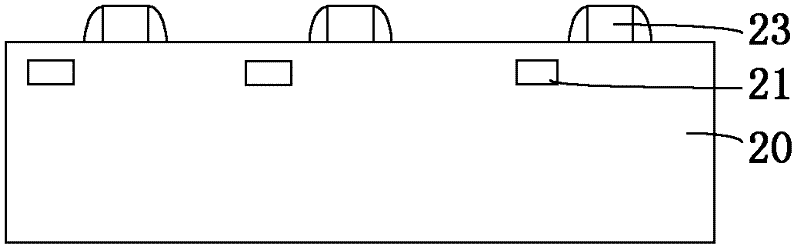

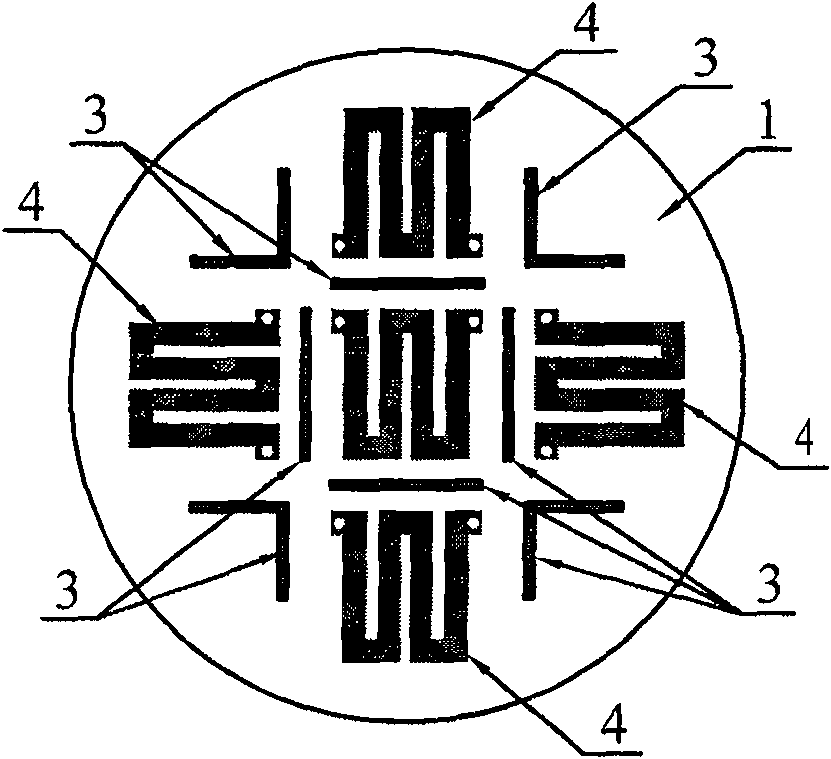

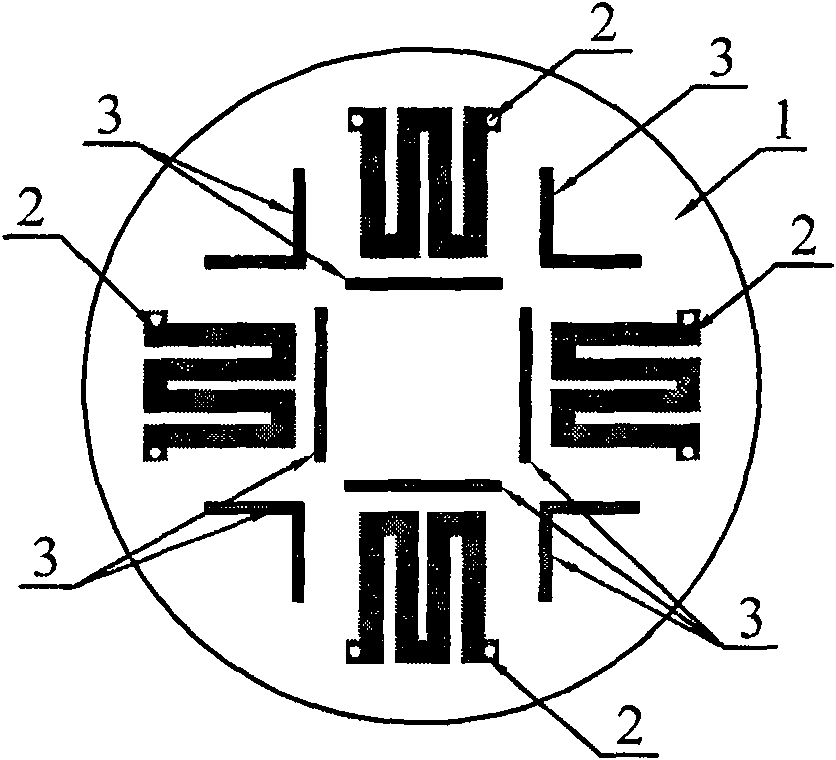

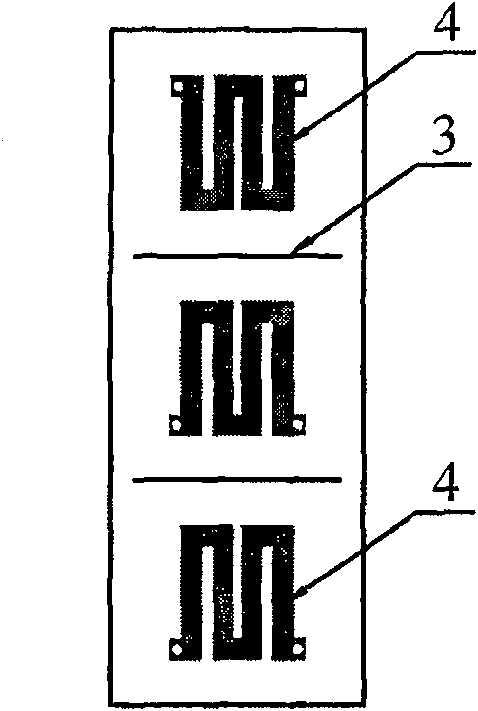

Array type multi-parameter wind sensor chip substrate and producing method thereof

InactiveCN101021571AThe production process is simpleStrong process compatibilityThermometers using electric/magnetic elementsVolume/mass flow by electric/magnetic effectsWind sensorEngineering

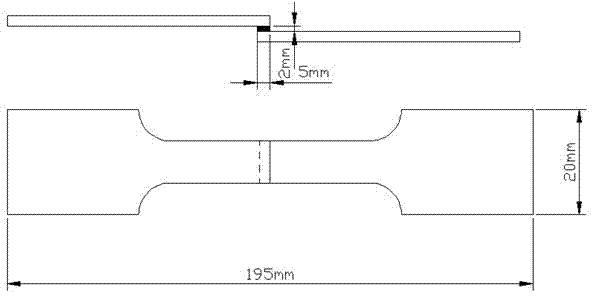

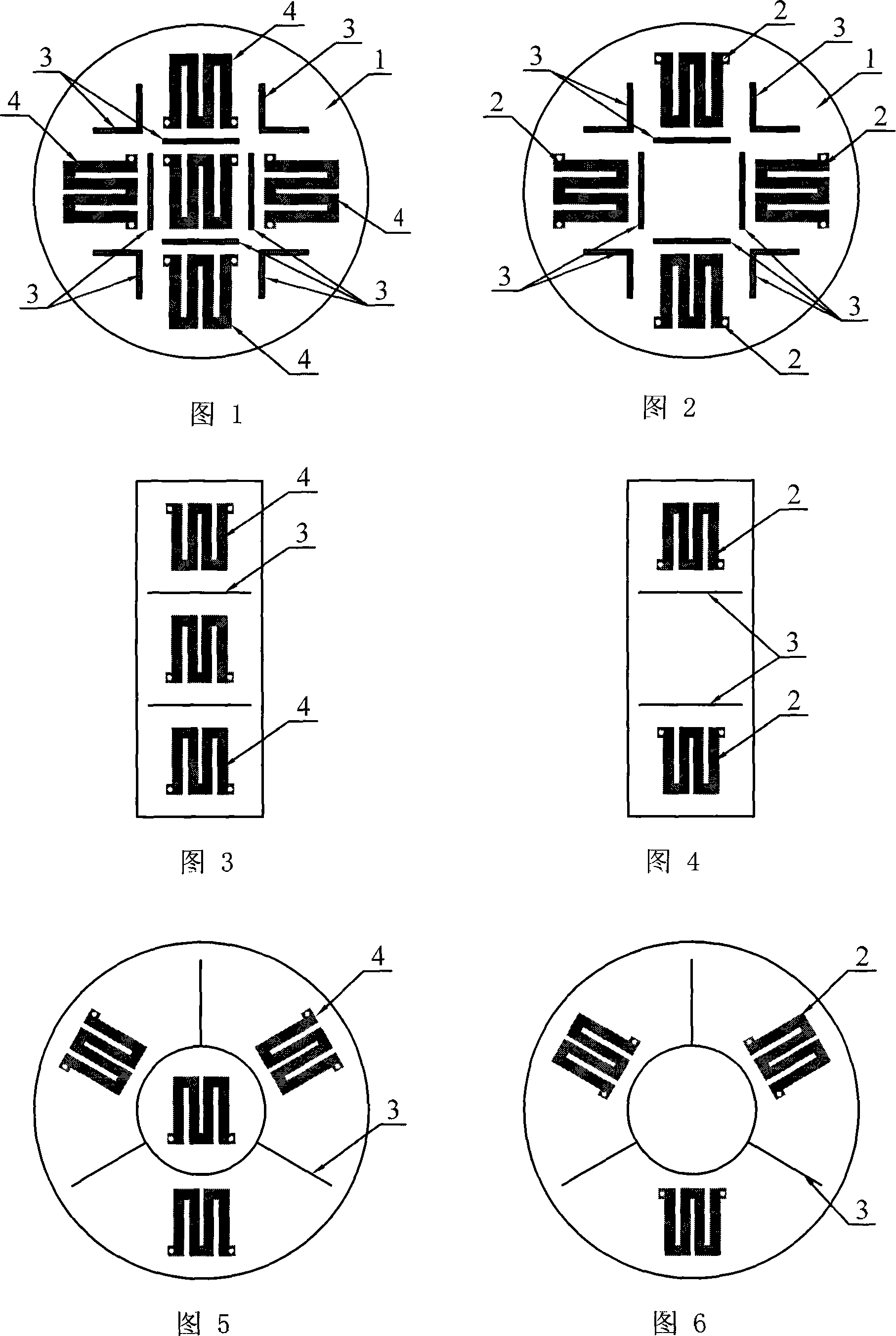

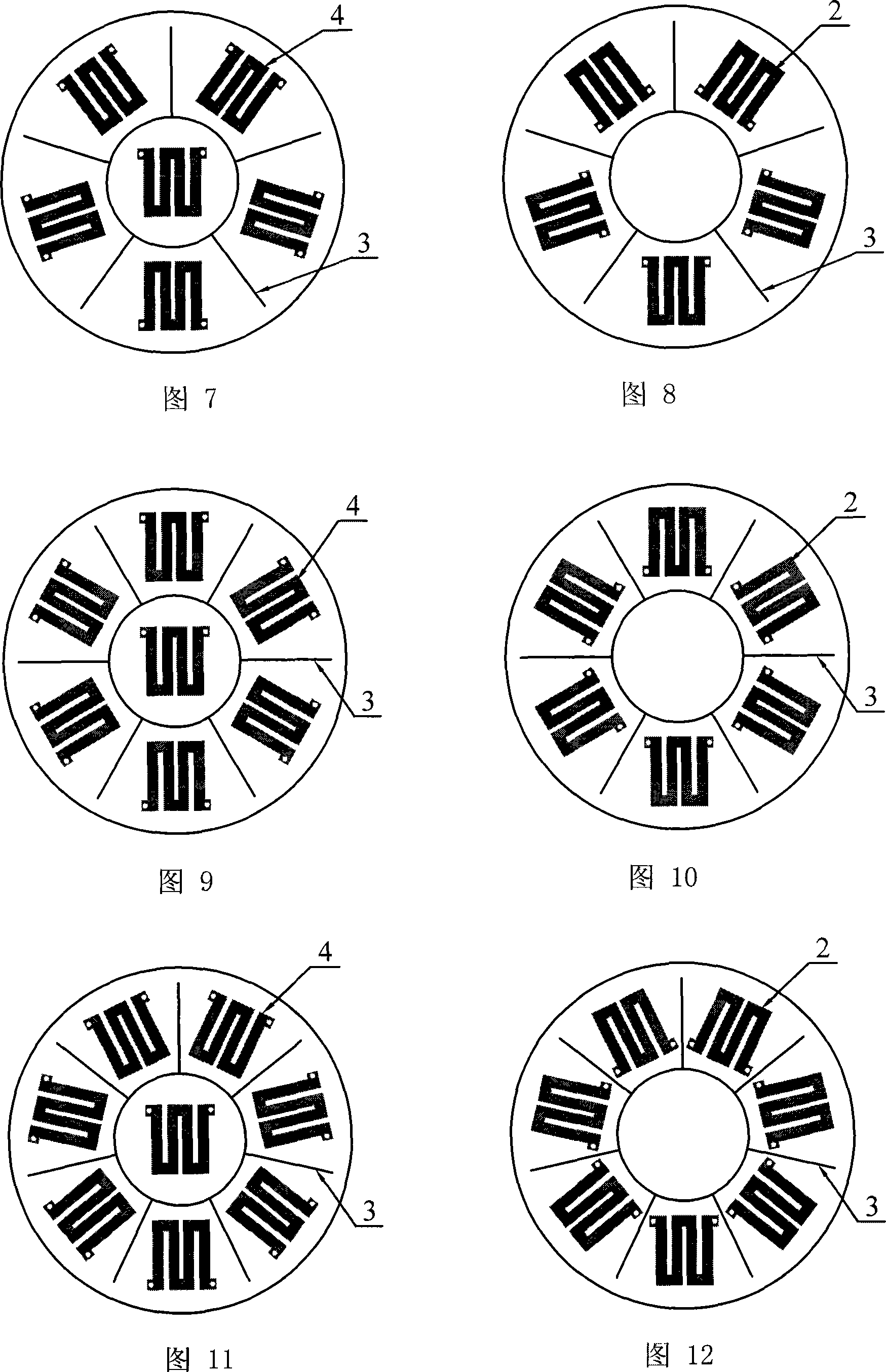

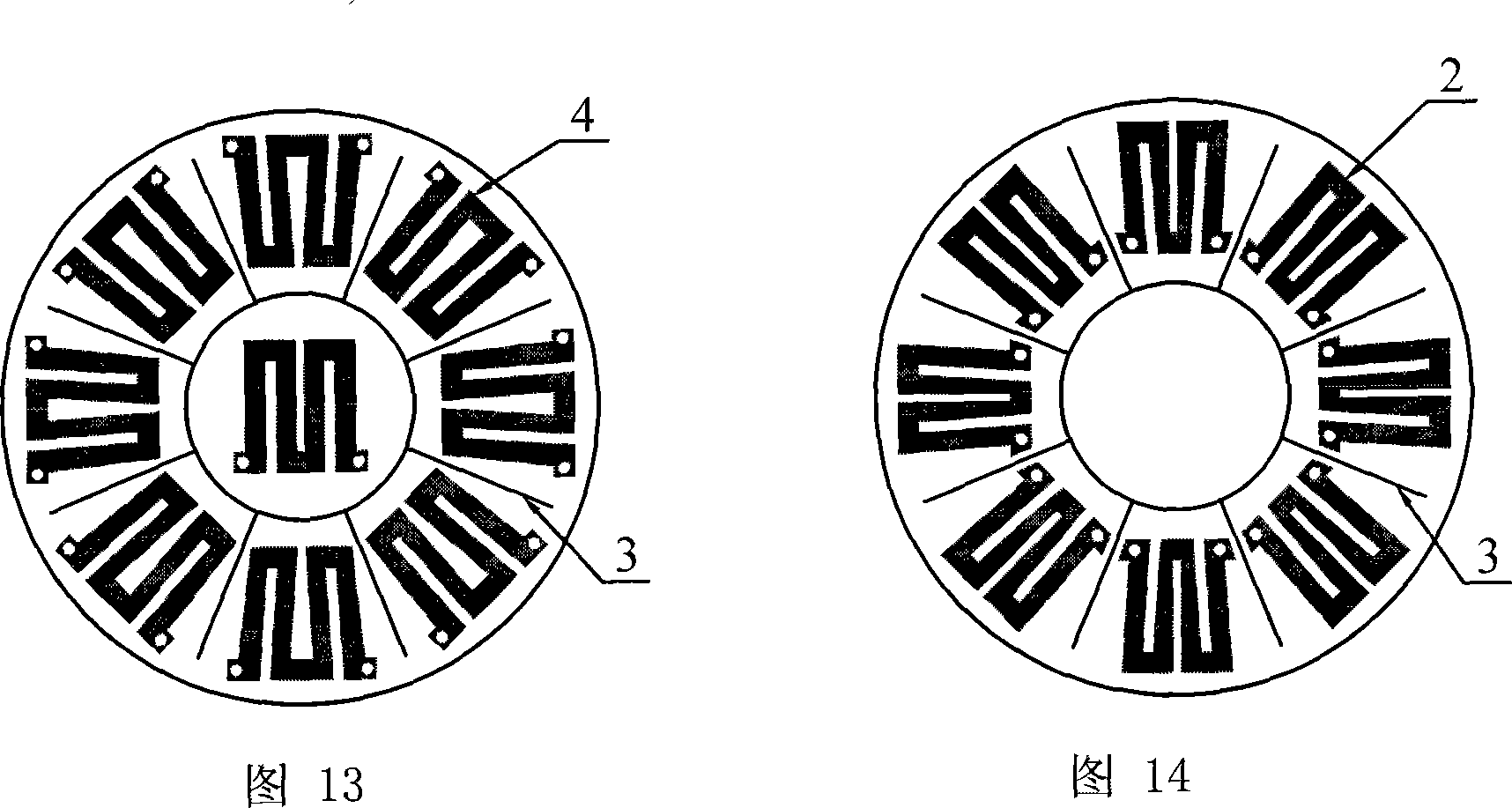

The invention relates to an array multiparameter wind sensor chip substrate and the making method thereof, relating to the wind sensor field. And it comprises a substrate, n heating components, m thermosensitive components and several heat insulation grooves, where n is natural number not less than 2, m=n+1, the substrate is a circular or regular polygonal nonconductive plate, n centrosymmetric heating components are fixed on the back of the substrate, a heat insulation groove is made between every two adjacent heating components, n thermosensitive components corresponding to the n heating components are fixed on the obverse side of the substrate, a thermosenstive component is fixed in the center of the obverse side of the substrate, and a heat insulation groove is made between every two adjacent thermosensitive components. And it can apply to wind sensors and wind parameter measuring systems.

Owner:HARBIN UNIV OF SCI & TECH

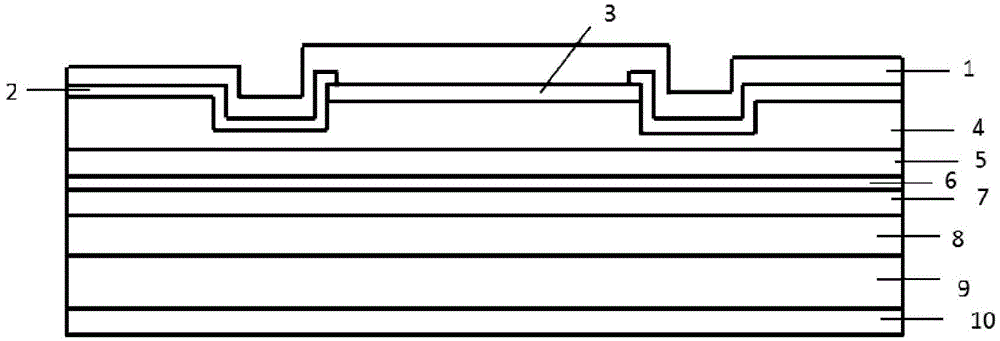

Preparation method of improving semiconductor laser reliability

ActiveCN105990790ARaise the COD thresholdImprove reliabilityLaser active region structureEtchingOhmic contact

A preparation method for improving the reliability of a semiconductor laser, which adopts one-time etching to simultaneously remove the ohmic contact layer other than the ridge-shaped mesa of the semiconductor laser, and introduces a non-implantation region window structure. The present invention is based on the Schottky contact principle between the P electrode and the epitaxial layer of the chip, and simultaneously removes the ohmic contact layer other than the ridge-shaped mesa and the ohmic contact layer at the cavity surface through a single etching process to introduce a non-implantation region window structure to form a Schottky The base contact layer achieves the purpose of preventing leakage on both sides of the double channel region in the laser, improving device reliability and increasing the COD threshold. The invention only adopts one-time photolithography process, has simple preparation process, wide application range and strong compatibility, and can be combined with other special processes to further improve the performance of semiconductor lasers.

Owner:Shandong Huaguang Optoelectronics Co. Ltd.

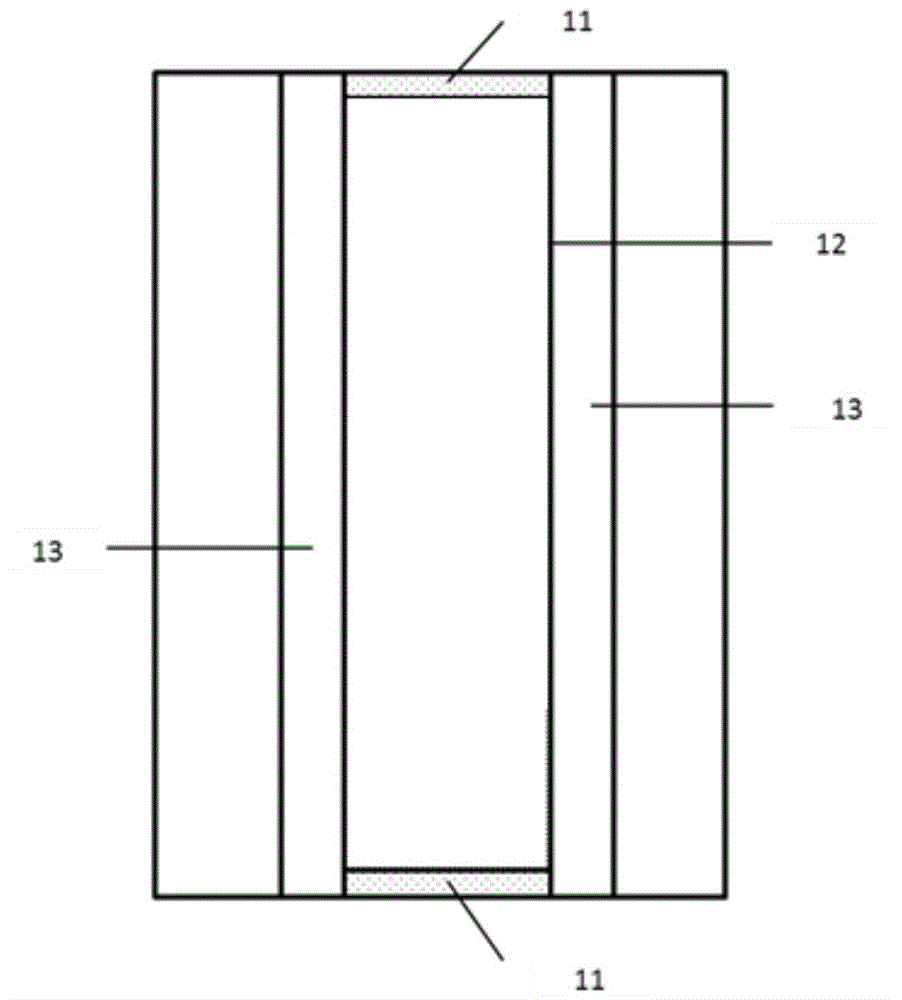

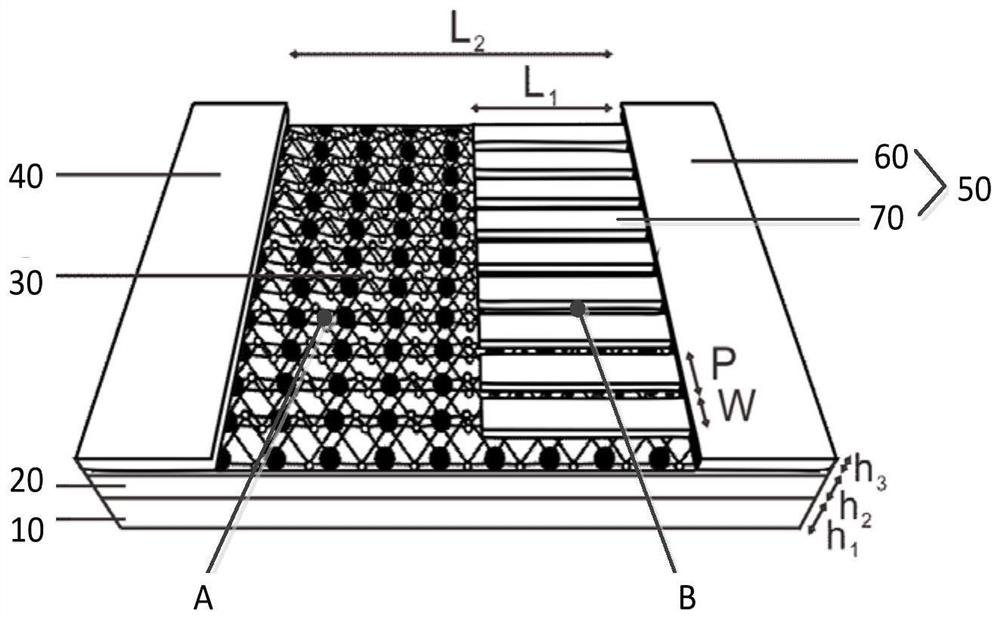

Field effect transistor gas sensor and array preparation method thereof

ActiveCN110579526AHigh sensitivityIncrease power consumptionMaterial analysis by electric/magnetic meansField-effect transistorQuantum gate

The invention discloses a field effect transistor gas sensor and an array preparation method thereof. The field effect transistor (FET) gas sensor is a gate-sensitive FET gas sensor with a gate electrode modified by quantum dots, and a gate-sensitive electrode layer (5) of the FET gas sensor is of a two-layer composite structure or of a single-layer structure made of a composite material. The two-layer composite structure comprises a metal film layer and a quantum dot layer deposited on the surface of the metal film layer. The single-layer structure made of a composite material is specificallya single-layer structure made of a composite material formed by combining quantum dots and a metal or metalloid material. According to the invention, improvement is made on the internal composition and structure of the gate-sensitive FET, the corresponding preparation method and the like, quantum dots are used as a gate electrode and a gas sensitive layer at the same time, and the bias voltage ofthe gate electrode and the channel modulation effect are regulated and controlled by utilizing the adsorption characteristic of a quantum dot gate-sensitive electrode to different gases. A room-temperature gas sensor with high sensitivity, low power consumption and high selectivity can be obtained, and low-concentration target gases (such as H2) can be detected.

Owner:HUAZHONG UNIV OF SCI & TECH

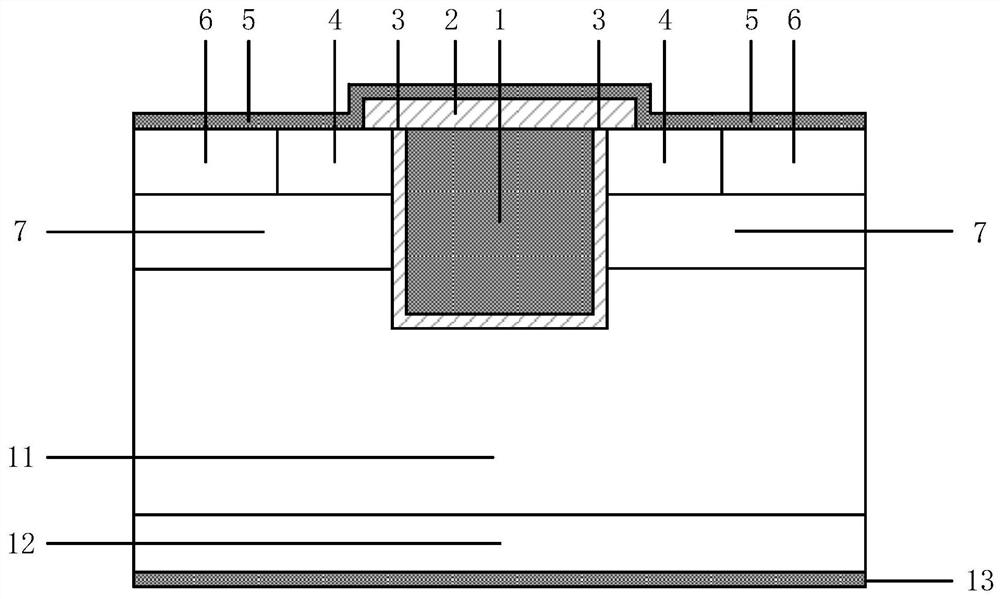

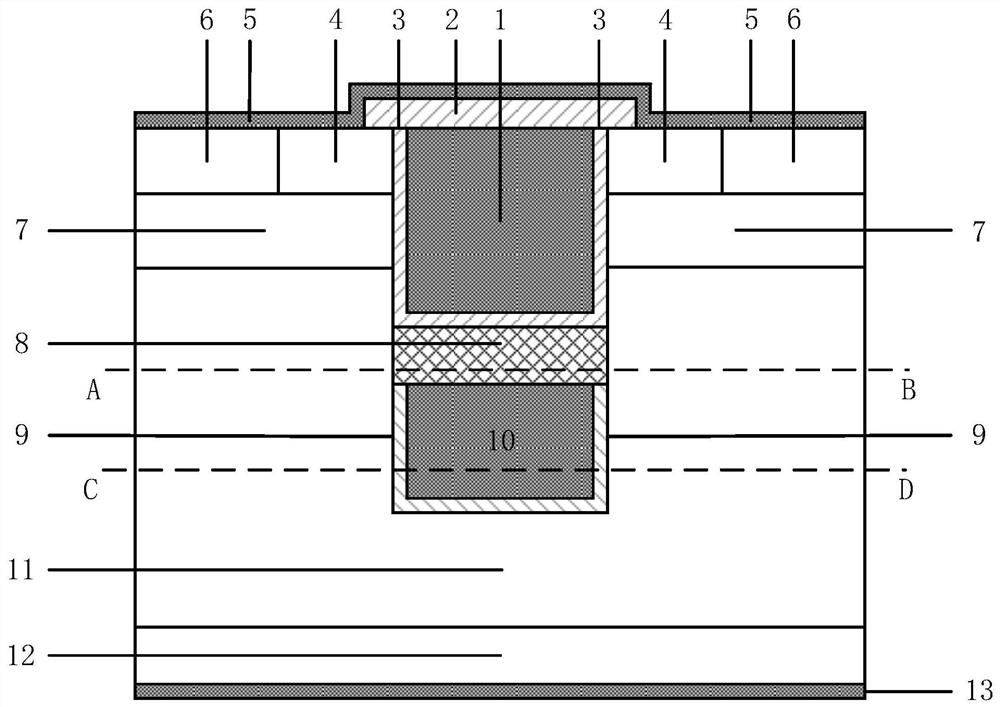

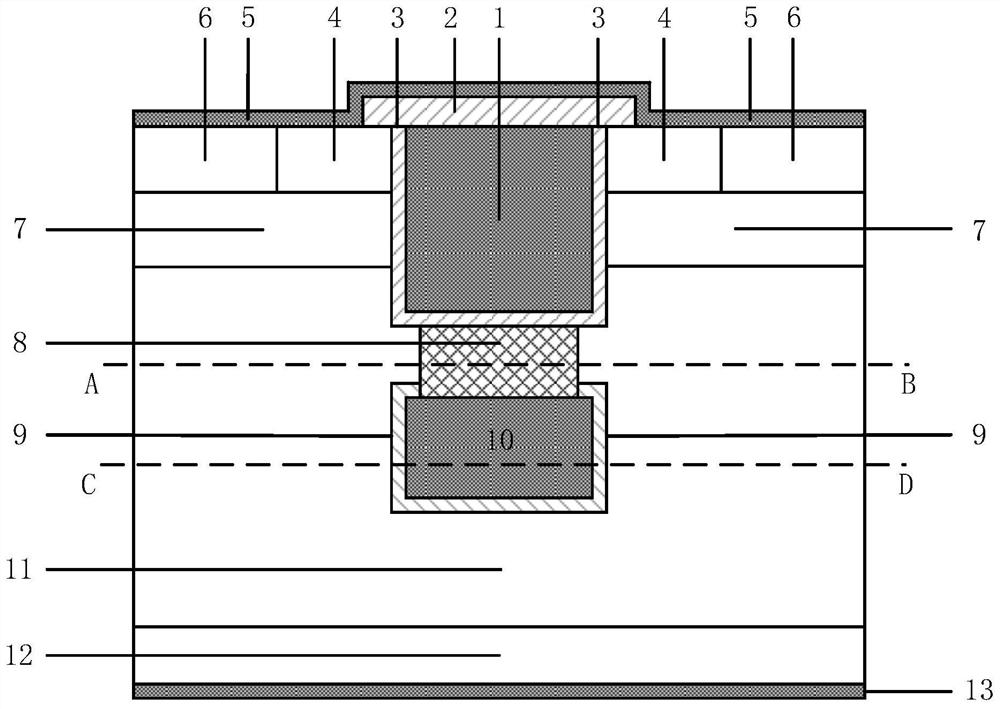

SiC trench gate power MOSFET device and preparation method thereof

ActiveCN111697077AReduce conduction voltage dropWill not increase the areaSemiconductor/solid-state device manufacturingDiodeCapacitanceDielectric

The invention relates to a SiC trench gate power MOSFET device, and belongs to the technical field of power semiconductors. The SiC trench gate power MOSFET device comprises a trench source structure,a P-type polycrystalline silicon and a trench gate structure which are manufactured in a trench. The trench source structure can reduce gate-drain capacitance (Cgd) and switching loss, when a sourcedielectric layer is made of a high-K dielectric material, the electric field intensity of a source dielectric can be effectively reduced, the P-type polycrystalline silicon realizes integration of anHJD in the N-channel SiC trench gate power MOSFET, the HJD has lower forward conduction voltage drop, conduction of a body diode is inhibited, a reliability problem caused by bipolar degradation is avoided, and the integrated HJD does not additionally increase the area of a chip. The integrated SiCHJD is a unipolar device, the reverse recovery characteristic is superior to that of a bipolar body diode, and stability is better due to the fact that parasitic parameters brought by an external diode lead are avoided, in addition, the device is simple and controllable in manufacturing process and high in compatibility with an existing process.

Owner:HANGZHOU SILICON-MAGIC SEMICON TECH CO LTD

Capacitive acceleration transducer for bending elastic beam and manufacturing method

ActiveCN102879608ASmall structure sizeStrong process compatibilityDecorative surface effectsAcceleration measurementClassical mechanicsTransducer

The invention provides a capacitive acceleration transducer for a bending elastic beam and a manufacturing method. The transducer at least comprises a first electrode structure layer, a middle structure layer and a second electrode structure layer, wherein the first electrode structure layer and the second electrode structure layer are respectively provided with electrode lead-out through holes; the middle structure layer comprises a frame formed by an oxygen-containing silicon chip comprising a dual-device layer, mass blocks of which two sides are symmetrical, and a bending elastic beam of which one side is connected with the frame and the other side is connected with the mass blocks; anti-overload convex points and damping adjusting grooves are symmetrically formed on the two sides of the two mass blocks; and the bending elastic beams positioned in different planes are distributed in a staggered mode and are not overlapped in space. Because the bending times, the total beam length and the total beam width of the bending elastic beams can be determined based on the needs, the capacitive acceleration transducer with different sensitivities can be prepared, and the flexibility is high.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Methods for manufacturing phase change memory

ActiveCN103840077AInhibit sheddingHigh degree of bindingElectrical apparatusPhase-change memoryDiffusion barrier

The invention provides two methods for manufacturing a phase change memory. According to the methods, a phase change material peeling phenomenon of the phase change memory is avoided. According to the first technical scheme, the method comprises the steps that a TiON bonding layer is arranged between a phase change material and a dielectric layer covering a lower electrode, the bonding degree between the dielectric layer and the phase change material is increased through the TiON bonding layer, so that the phase change material is prevented from falling off, and therefore the reliability of the phase change memory is improved. According to the second technical scheme, the bonding layer of a side-wall shape is formed to increase the bonding performance of the phase change material, a diffusion impervious layer of the side wall and the dielectric layer of the side wall; due to the fact that the size of the bottom of the side wall is larger than the size of the top of the side wall, the size of the bottom of a space where the phase change material is deposited is made to be smaller than the size of the top of the space, the contact area of the phase change material and the lower electrode is reduced, in other words, the bonding performance of the phase change material, the diffusion impervious layer of the side wall and the dielectric layer of the side wall is increased through the bonding layer of the side-wall shape is increased, the contact area of the phase change material and the lower electrode is reduced, and an operation current is reduced.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Piezoelectric sensor and preparation method thereof

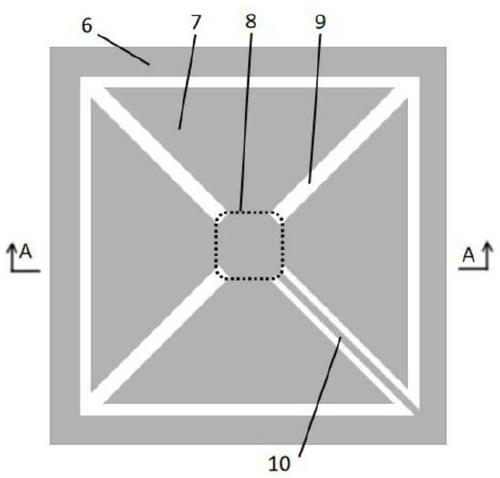

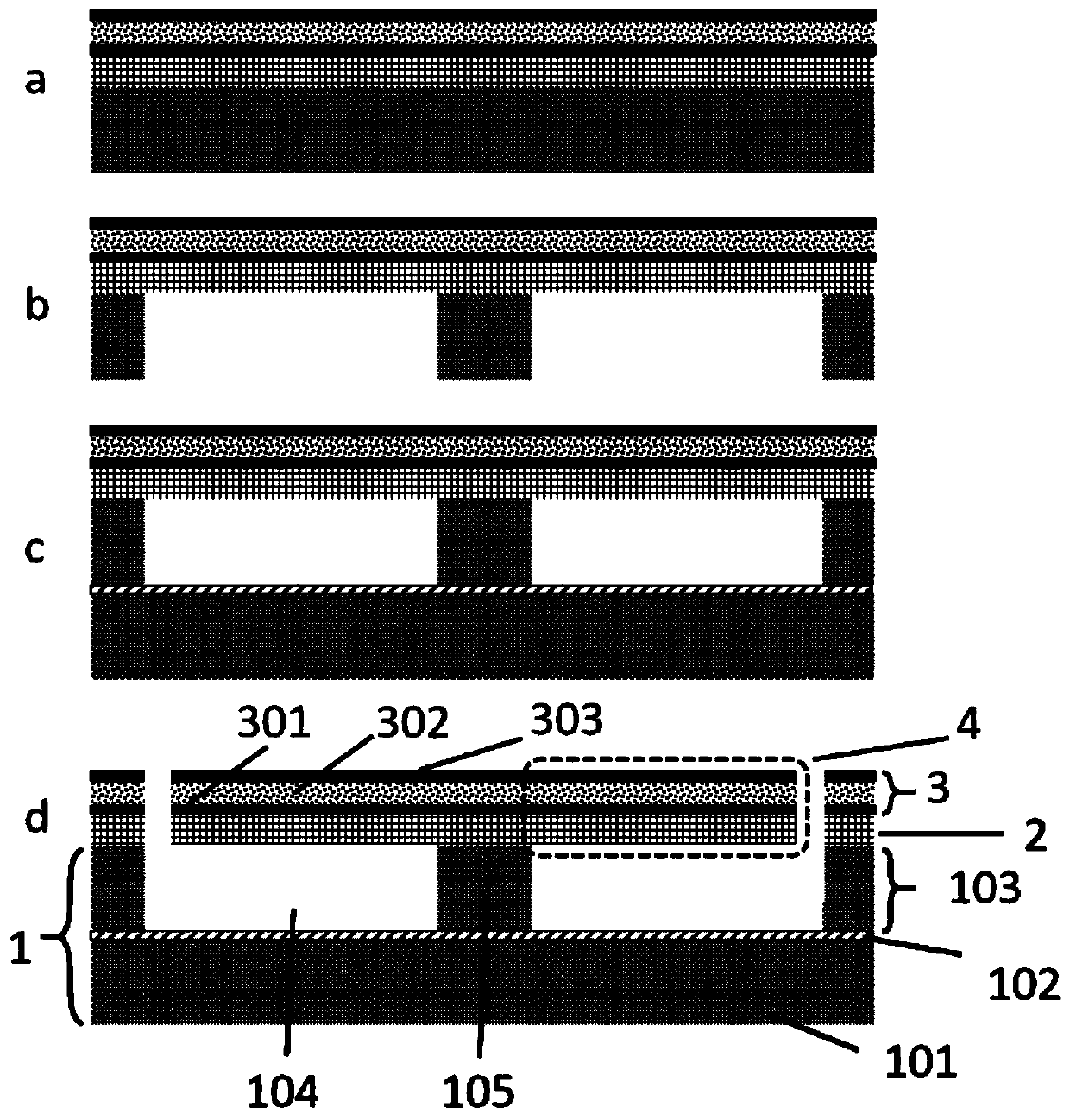

InactiveCN111174951AHigh sensitivityImprove signal-to-noise ratioTelevision system detailsFluid pressure measurement using piezo-electric devicesCantilevered beamWafering

The invention provides a piezoelectric sensor and a preparation method thereof. The piezoelectric sensor comprises a substrate, a plurality of piezoelectric cantilever beams and a fixed column, wherein the substrate is provided with a plurality of cavities; the piezoelectric cantilever beam is of a bimorph structure or is composed of a single-morph structure and a supporting layer, and the area ofa free end of the piezoelectric cantilever beam is larger than that of the fixed end; the fixed column is arranged in the center of the substrate and used for fixing the piezoelectric cantilever beam. According to the piezoelectric sensor provided by the invention, a new structural form of the piezoelectric cantilever beam is provided, and the substrate with a specific shape and a depth cavity iscombined, so that the performance such as the sensitivity of the sensor can be remarkably improved. The preparation method of the piezoelectric sensor comprises the following steps: processing the substrate with the cavity, and depositing and etching the supporting layer and a piezoelectric laminated layer in the piezoelectric cantilever beam on the substrate. The preparation method has the advantages of simple process and strong compatibility, and is suitable for processing piezoelectric sensors containing various piezoelectric materials and various substrates.

Owner:武汉敏声新技术有限公司

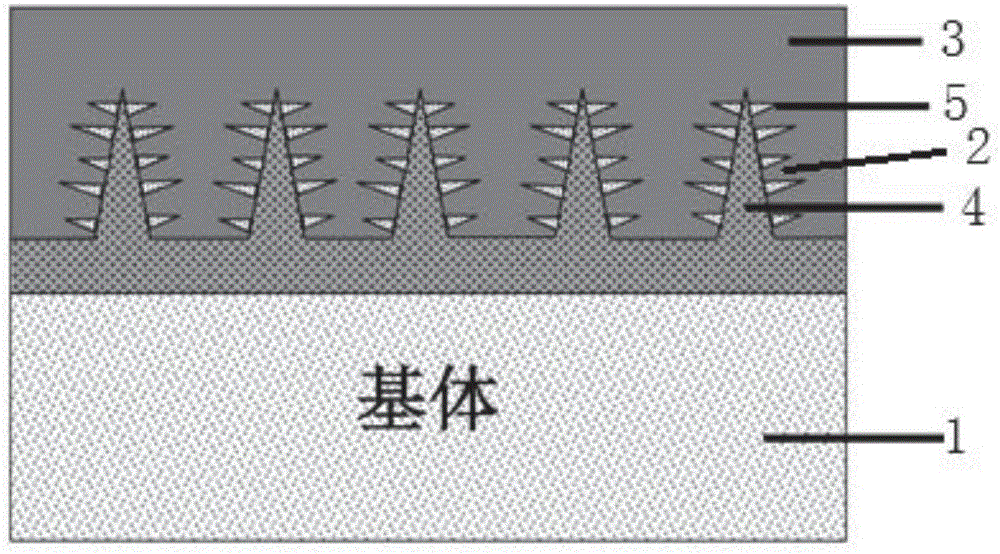

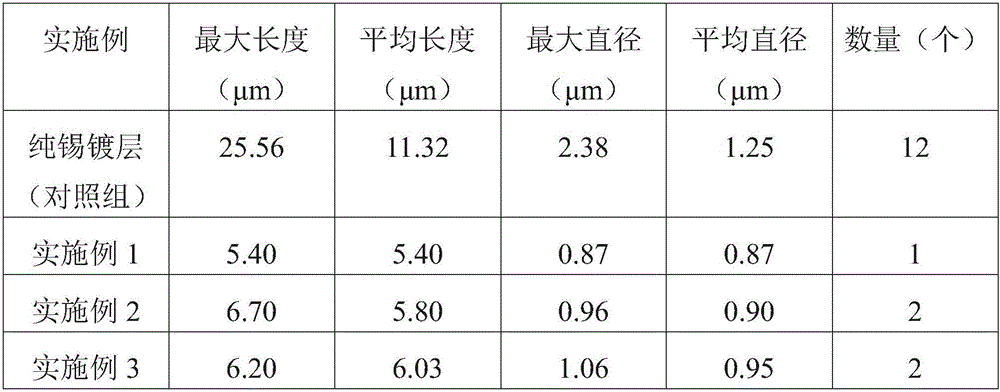

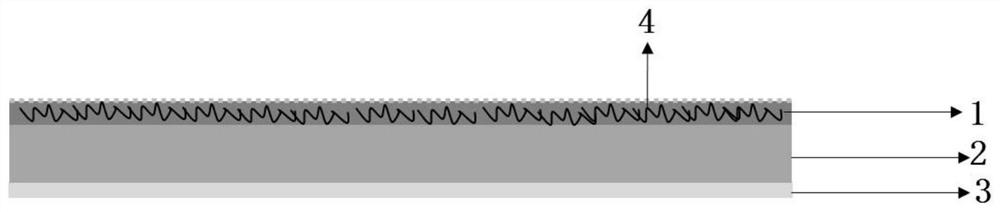

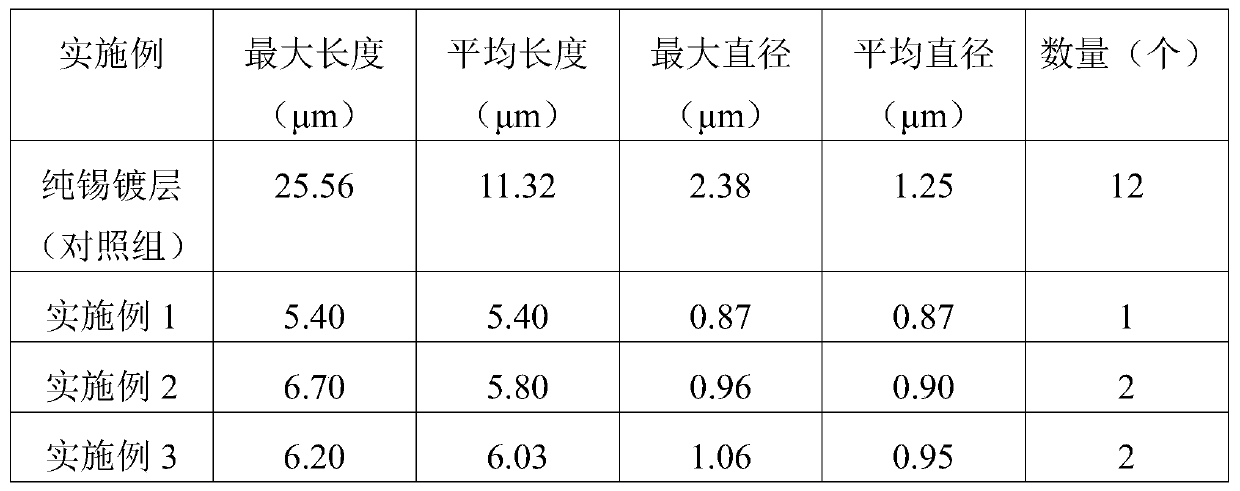

A method for restraining tin whisker growing based on micro-nano cone structure

InactiveCN106676598ASuitable for growthLarge specific surface areaSuperimposed coating processSemiconductor devicesMicro nanoSurface oxidation

The invention discloses a method for restraining tin whisker growing based on a micro-nano cone structure. The method comprises the following steps that a conductive matrix is selected and cleaned; after the matrix is cleaned, a micro-nano cone structure layer grows on the conductive matrix; then the micro-nano cone structure layer is cleaned, and a surface oxide layer is removed; and finally, tin-based welding flux grows on the micro-nano cone structure layer. According to the method, the pressure stress in a tin cladding layer is released by utilizing the fact that the micro-nano cone structure layer has a large specific surface area and a unique geometrical shape, driving force for tin cladding layer tin cladding layer is reduced, and formation of tin whisker is restrained; the method is suitable for growing of various types of tin layer thin films and has the advantages that the preparation method is simple, the temperature is low, compatibility of the technique is high, stability is high, and growing of tin whiskers can be effectively restrained.

Owner:SHANGHAI JIAO TONG UNIV

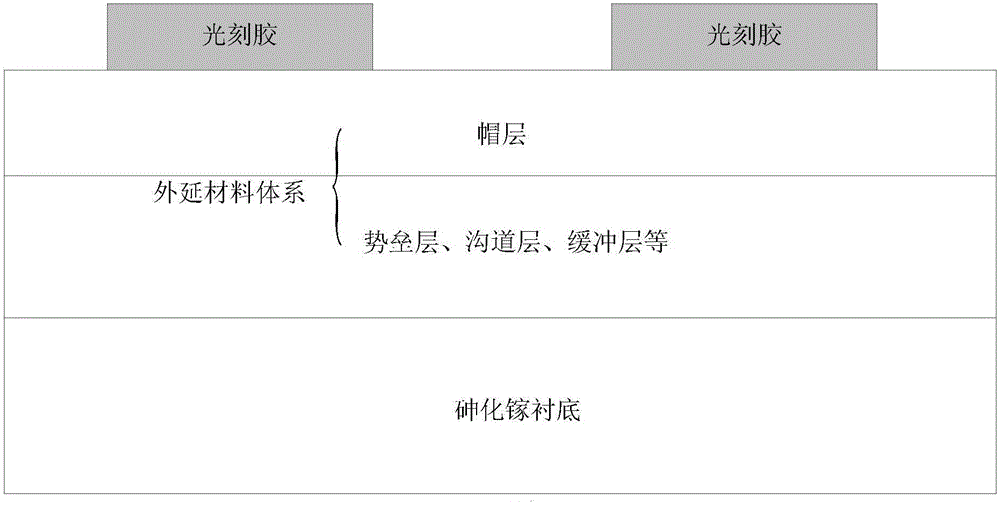

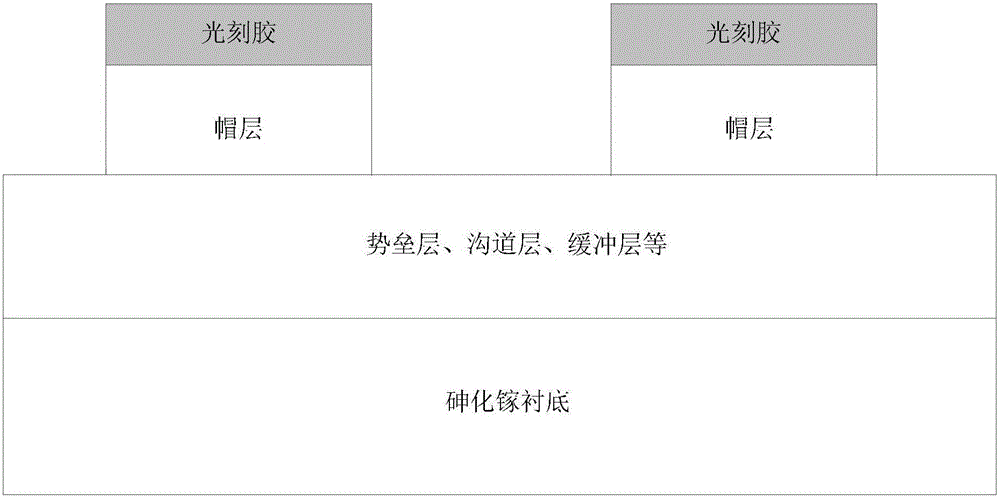

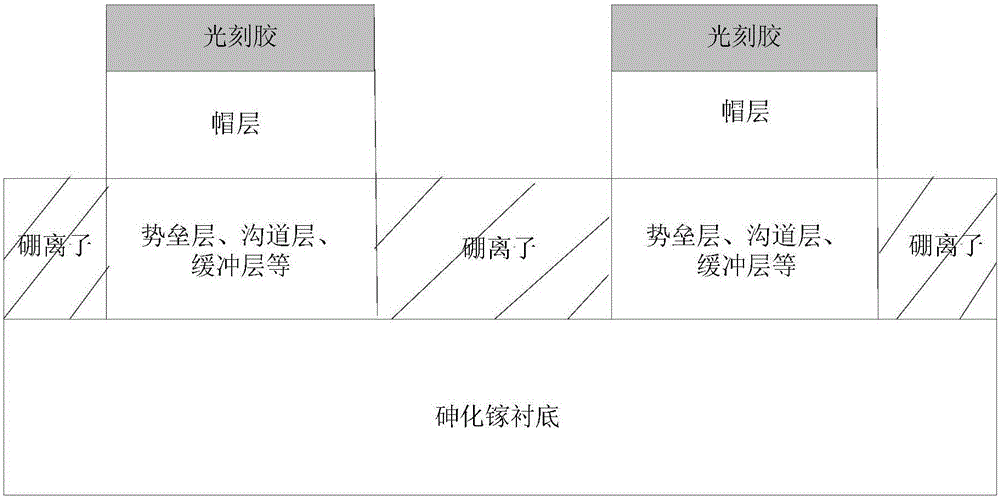

GaAs substrate mHEMT active region electrical isolating method

ActiveCN105070681AImprove the isolation effectImprove injection abilitySemiconductor/solid-state device manufacturingSemiconductor devicesIsolation effectEtching

The invention discloses a GaAs substrate mHEMT active region electrical isolating method, which is a method combining wet etching and ion implantation for active region electrical isolation of a various-component high-electron-mobility transistor. The GaAs substrate mHEMT active region electrical isolating method comprises the steps of removing a surface highly-doped layer and then carrying out ion implantation isolation, thereby effectively improving the ion implantation effect, and further improving the isolation effect between active regions. Under the same condition, the isolating method combining ion implantation and mesa etching has the advantages of good electrical isolation effect, high process compatibility, small impact on subsequent process, good reproducibility, easy implementation and the like, effectively avoids the defects caused by adopting mesa etching and ion implantation separately, and has good use value for the semiconductor manufacturing process.

Owner:GUILIN UNIV OF ELECTRONIC TECH

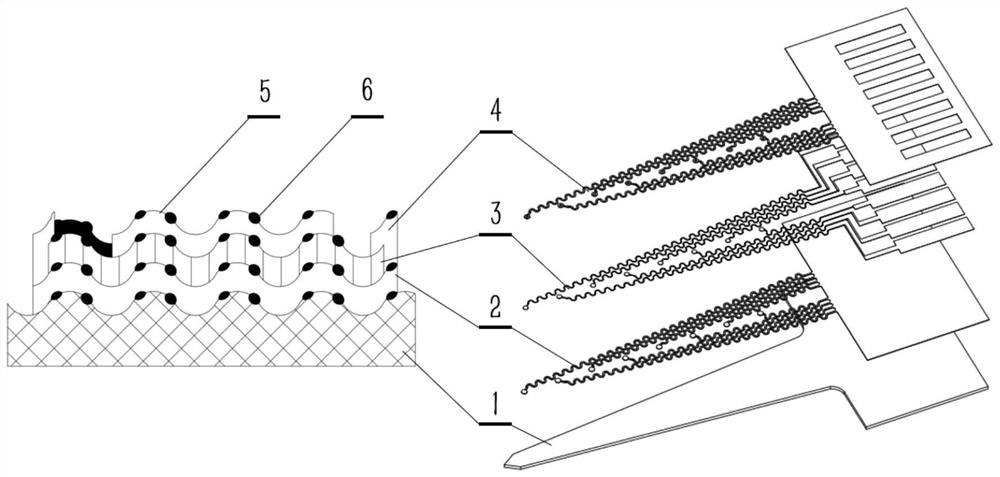

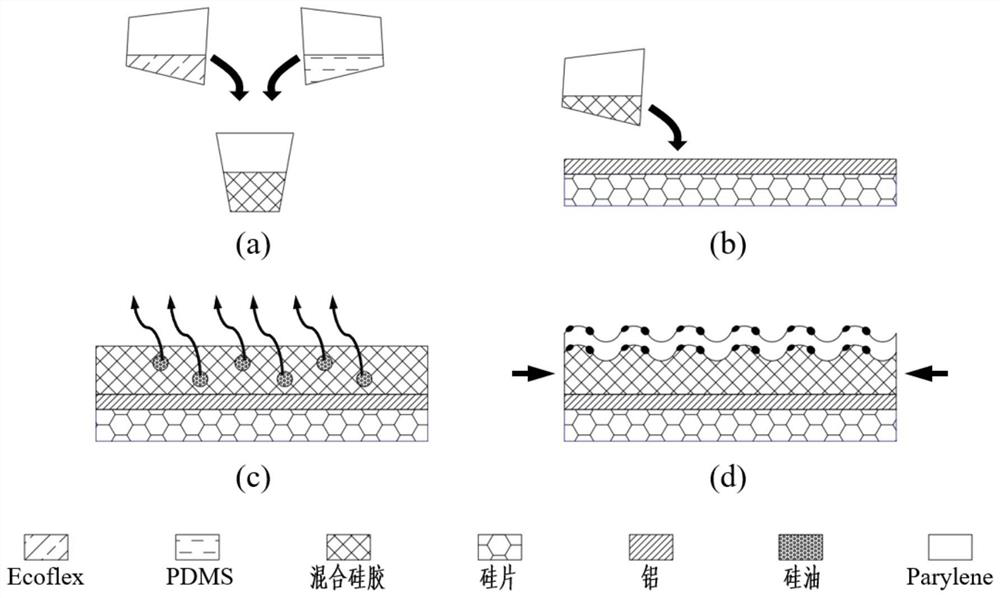

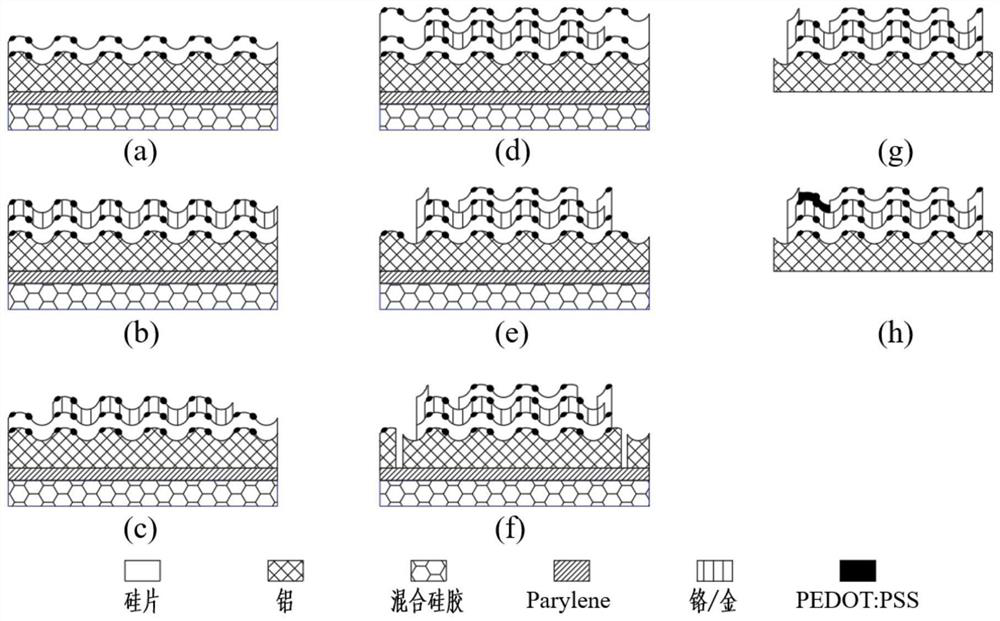

Soft nerve probe based on mixed silica gel and preparation method thereof

PendingCN114224346AIncreased wrinkle densityHigh specific surface areaDiagnostic recording/measuringSensorsThin membraneChemistry

The invention discloses a soft nerve probe based on mixed silica gel and a preparation method of the soft nerve probe. The preparation method comprises the following steps: mixing two or more silica gel with different Young moduli, and doping silicone oil to obtain an elastic mixed silica gel substrate; a first polymer film is deposited on an elastic mixed silica gel substrate to serve as a bottom polymer insulating layer, and wrinkles are formed automatically; the metal conducting layer is located on the bottom polymer insulating layer, and a second polymer film is deposited on the metal conducting layer to serve as a top polymer packaging layer; the two layers of polymer films are etched into a snakelike line contour through oxygen plasma reaction etching, and the flexible nerve probe contour is obtained through laser cutting of the elastic mixed silica gel substrate. The device is suitable for low-damage implantation of probes with different lengths; the bonding force between the electroplating modified material and an electrode point interface can be effectively improved, the stability of a plating layer is improved, the bonding force between the electroplating electrode modified material and the electrode interface is also effectively improved, and stable and reliable electrochemical performance is ensured.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

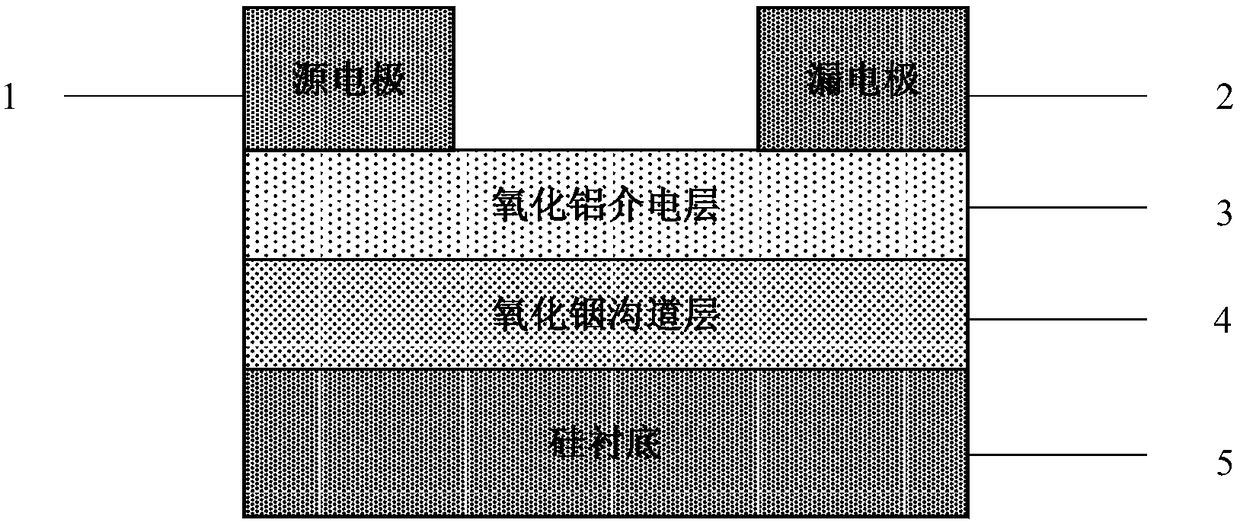

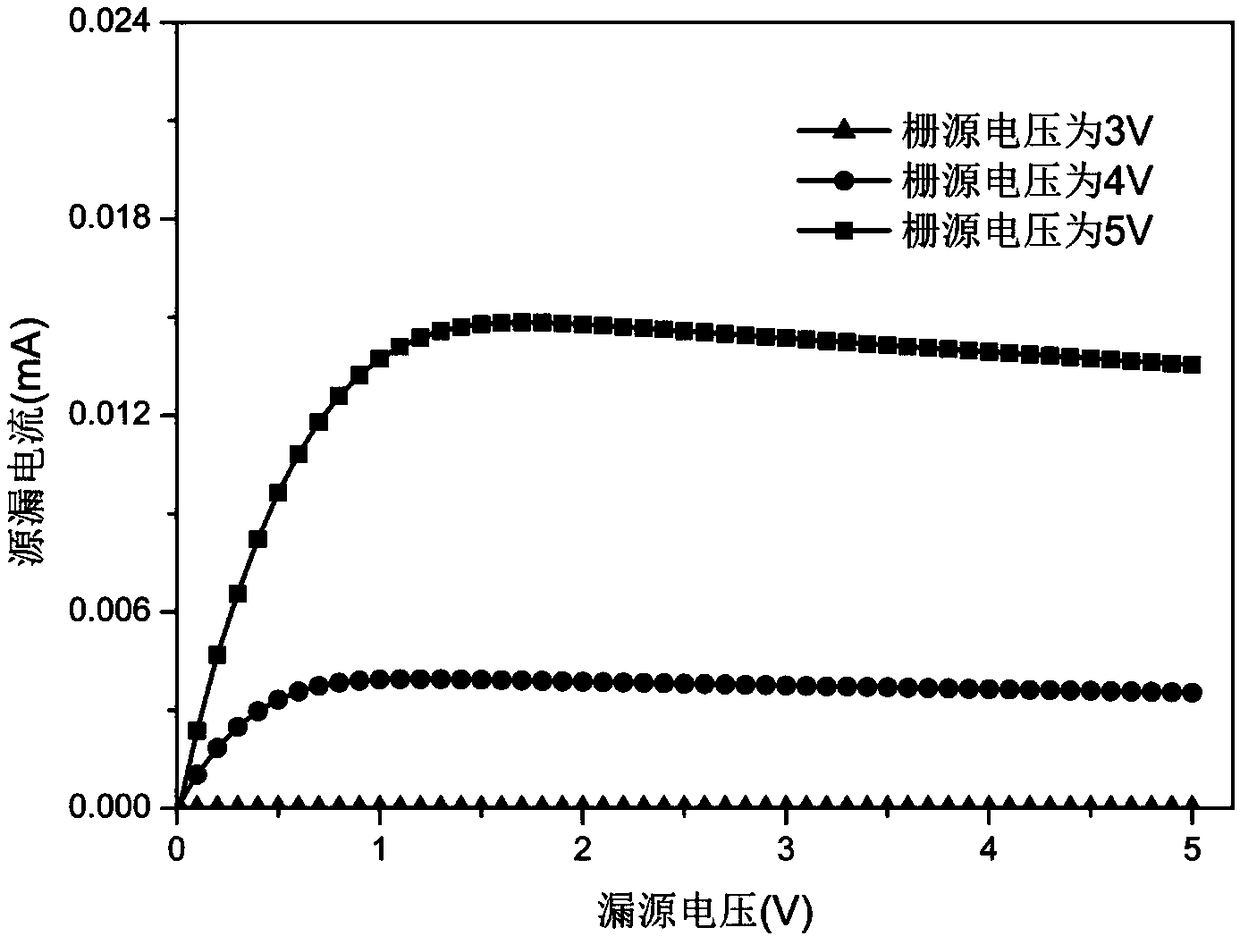

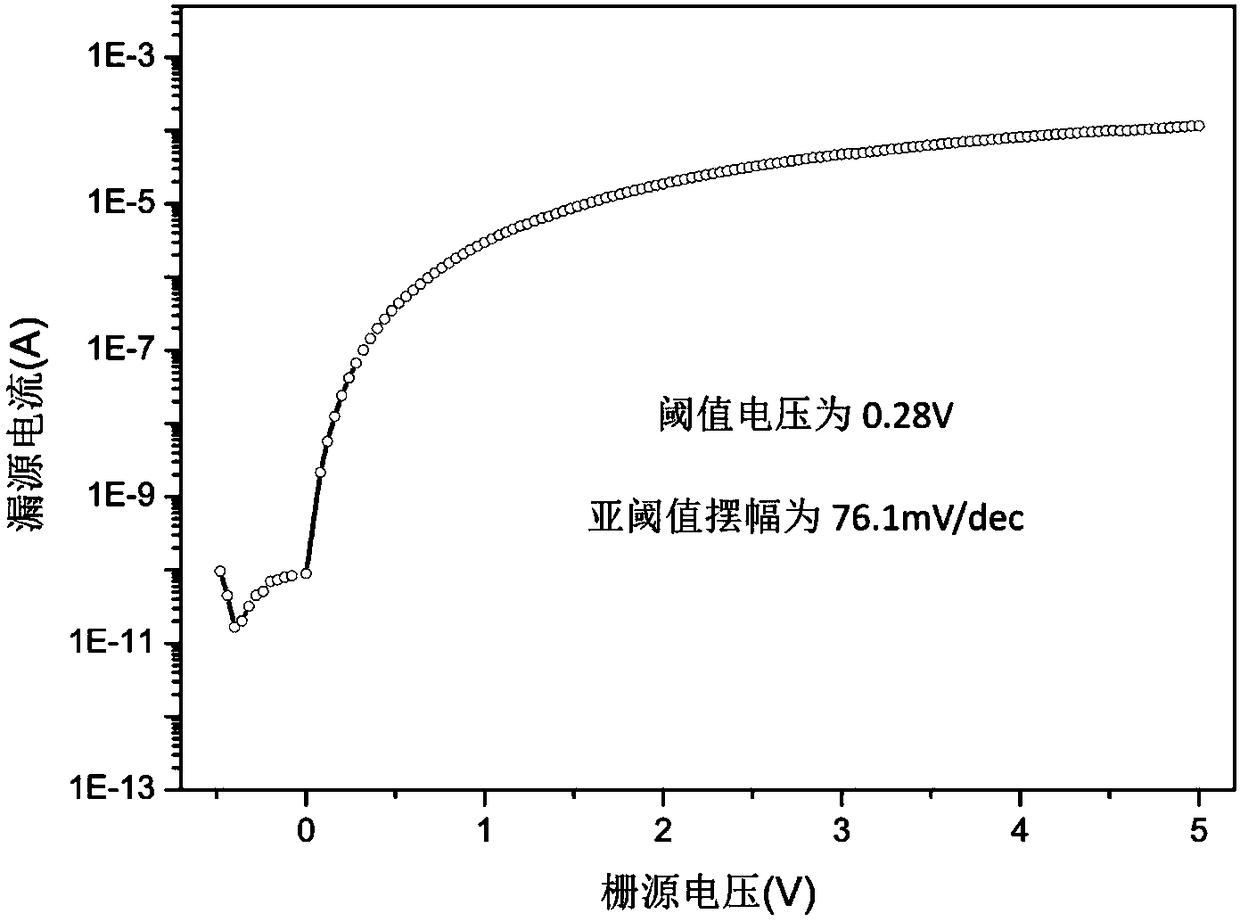

Preparation method of indium oxide thin film transistor of low sub-threshold value amplitude of oscillation

ActiveCN108598005AReduce interface defectsReduced subthreshold swingTransistorSemiconductor/solid-state device manufacturingEnvironmental resistanceOxide thin-film transistor

The invention discloses a preparation method of an indium oxide thin film transistor of low sub-threshold value amplitude of oscillation, and belongs to the technical field of preparation of a semiconductor thin film transistor. According to the method, atomic layer deposition (ALD) equipment is adopted, and a layer of aluminum oxide thin film is deposited on a heavily doped silicon substrate; then by adopting a spin coating mode, the aluminum oxide thin film is uniformly coated with an indium nitrate water solution to be pre-heated at a temperature of 100-150 DEG C for 10min; then optical annealing is performed in a position of 10cm below a high-pressure mercury lamp for 1.5h to decompose indium nitrate into indium oxide; and finally, by adopting a thermal evaporation mode, an aluminum electrode is evaporated on an indium oxide thin film to obtain the thin film transistor of low sub-threshold value amplitude of oscillation. By adoption of the preparation method, the preparation technology of the existing indium oxide thin film transistor is optimized, and low cost, simple and convenient operation and environment friendly materials are realized; the high-pressure mercury lamp is adopted for performing optical annealing, so that the indium oxide thin film can be prepared at a temperature of 100 DEG C or below; and the obtained thin film transistor is relatively low in sub-threshold value amplitude of oscillation and excellent in working performance.

Owner:EAST CHINA NORMAL UNIV

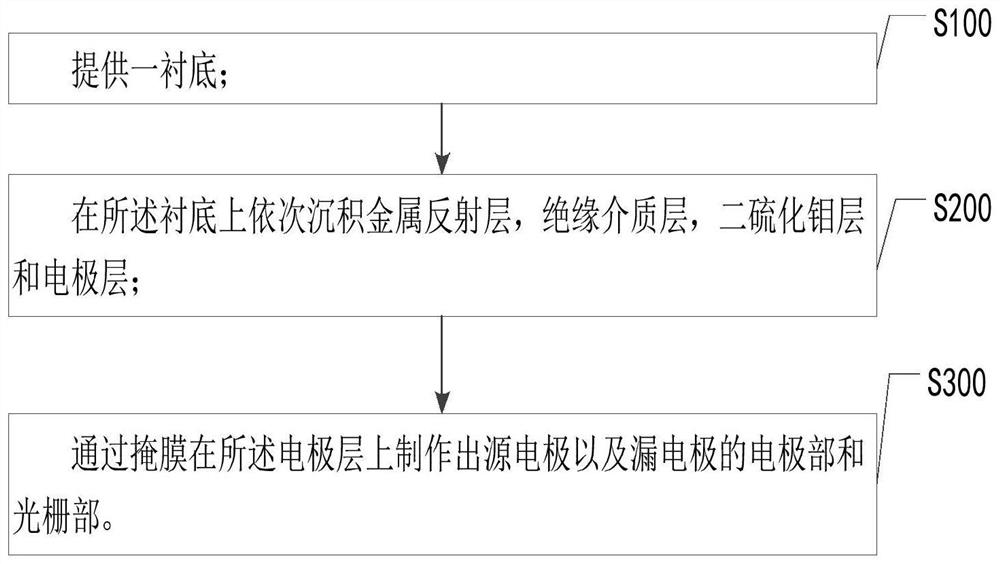

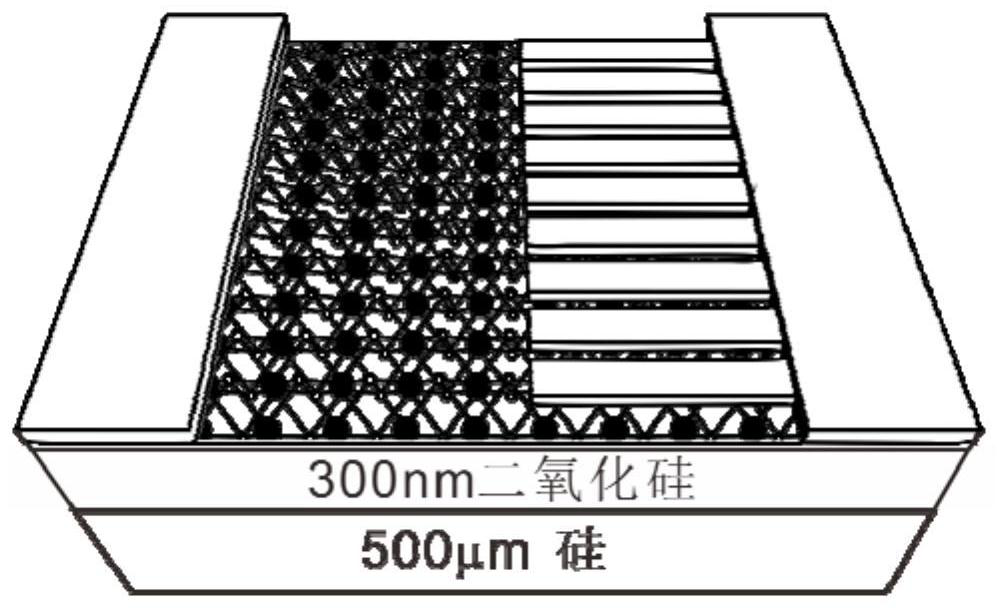

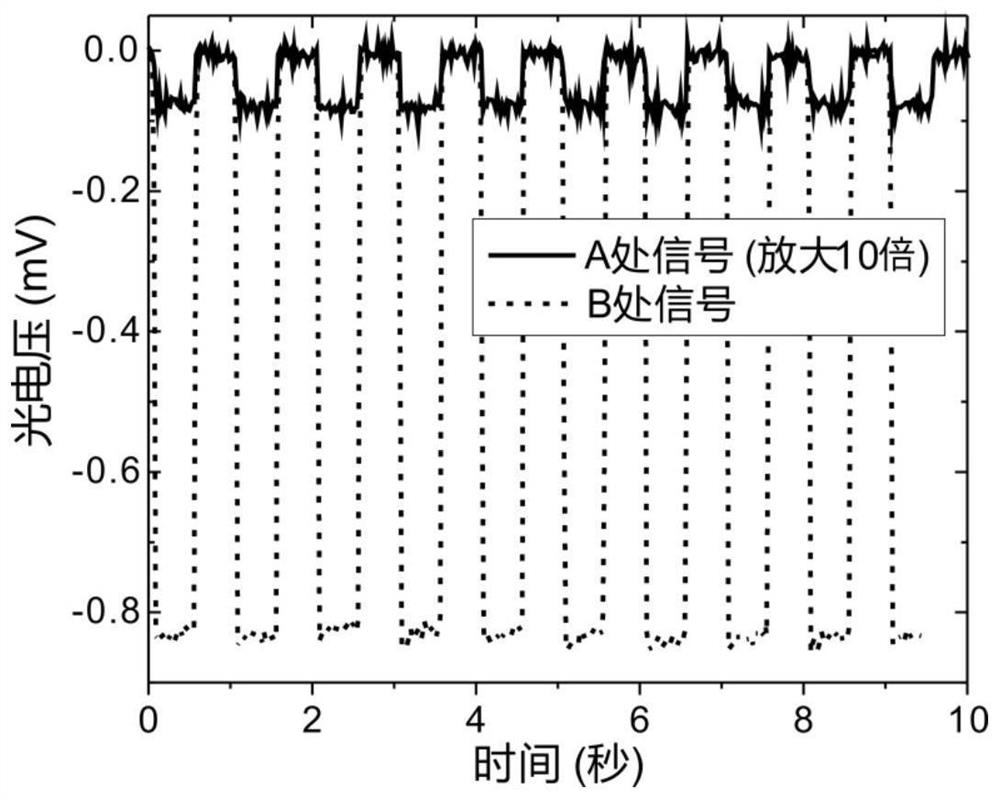

Molybdenum disulfide photoelectric detector and preparation method thereof

PendingCN113517357ABreak symmetryImprove photoresponseFinal product manufactureSemiconductor devicesChemistryLight absorbance

The invention provides a molybdenum disulfide photoelectric detector and a preparation method thereof. The molybdenum disulfide photoelectric detector comprises a metal reflecting layer, an insulating medium layer, a molybdenum disulfide layer, a source electrode and a drain electrode, wherein the metal reflecting layer, the insulating medium layer and the molybdenum disulfide layer are arranged from bottom to top, the source electrode and the drain electrode are arranged on the molybdenum disulfide layer at an interval, and the drain electrode comprises an electrode part and a grating part. According to the molybdenum disulfide photoelectric detector, the metal emission layer is adopted as the bottom layer, and the grating is integrated on the drain electrode, so that obvious light absorption difference can be formed between the drain electrode and the source electrode of the photoelectric detector, the symmetry of the light current at the two ends of the drain electrode and the source electrode is broken, and the light response of the photoelectric detector is enhanced.

Owner:深圳网联光仪科技有限公司

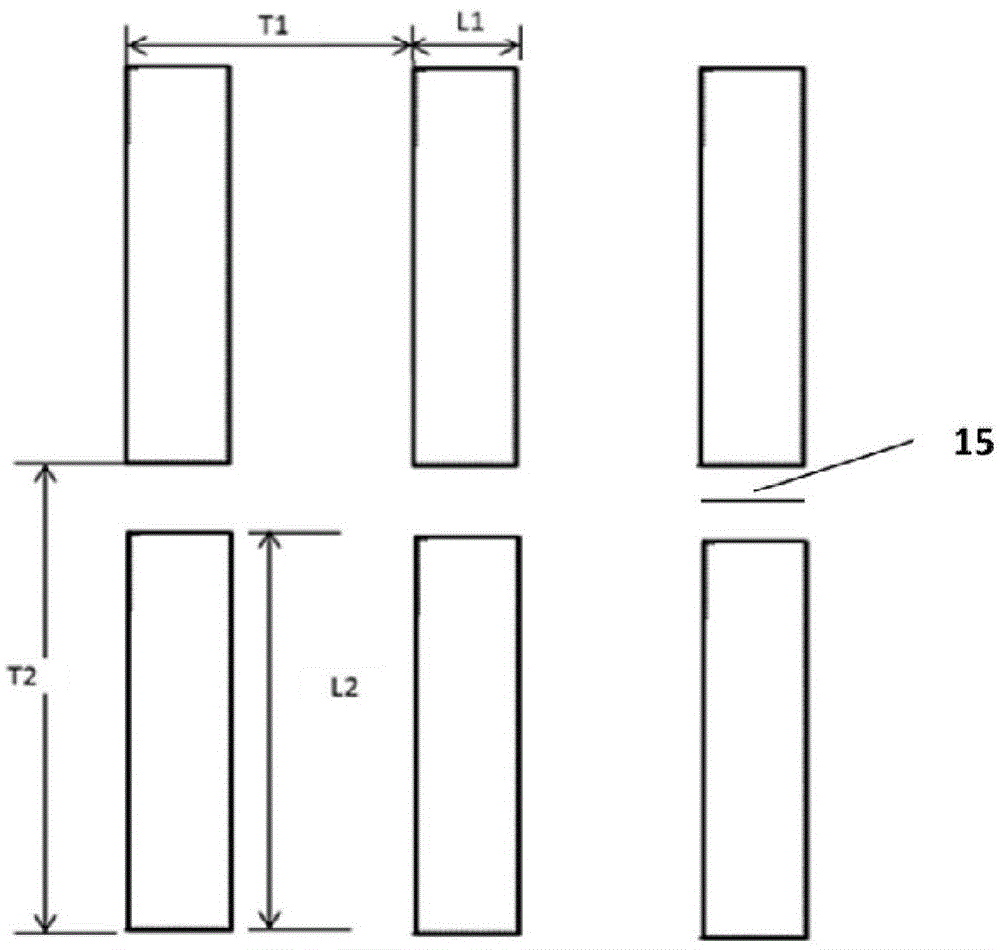

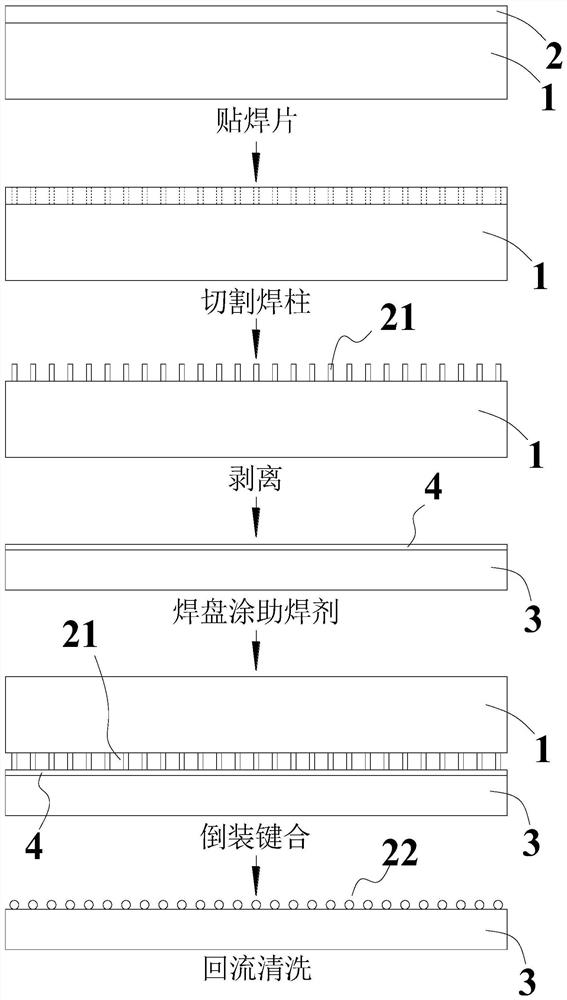

Preparation method of solder micro-bump array

ActiveCN111883502AFlexibleStrong process compatibilitySemiconductor/solid-state device detailsSolid-state devicesMicrosphereEngineering

The invention relates to the field of chip packaging, in particular to a preparation method of a solder micro-bump array, and the method comprises the following steps: pasting of a soldering lug: pasting the soldering lug on a carrier plate; cutting: cutting out a solder column array on the soldering lug; peeling: tearing off or peeling off the redundant soldering lugs, and only leaving the soldercolumn array; flip-chip bonding: transferring the solder column array to a bonding pad needing to be provided with a salient point area array. and reflowing: reflowing the bonding pad with the soldercolumn array to melt the solder column array into a ball so as to form a regular solder bump array. The method has the advantages that the method is simple in process, high in efficiency, flexible, convenient, suitable for welding flux of various types, free of specially-made microspheres, low in cost, suitable for overall manufacturing of wafers and suitable for cut chips and adapter plates, a specially-made ball mounting template is not needed, and large-scale application can be achieved.

Owner:CHINA ELECTRONIC TECH GRP CORP NO 38 RES INST

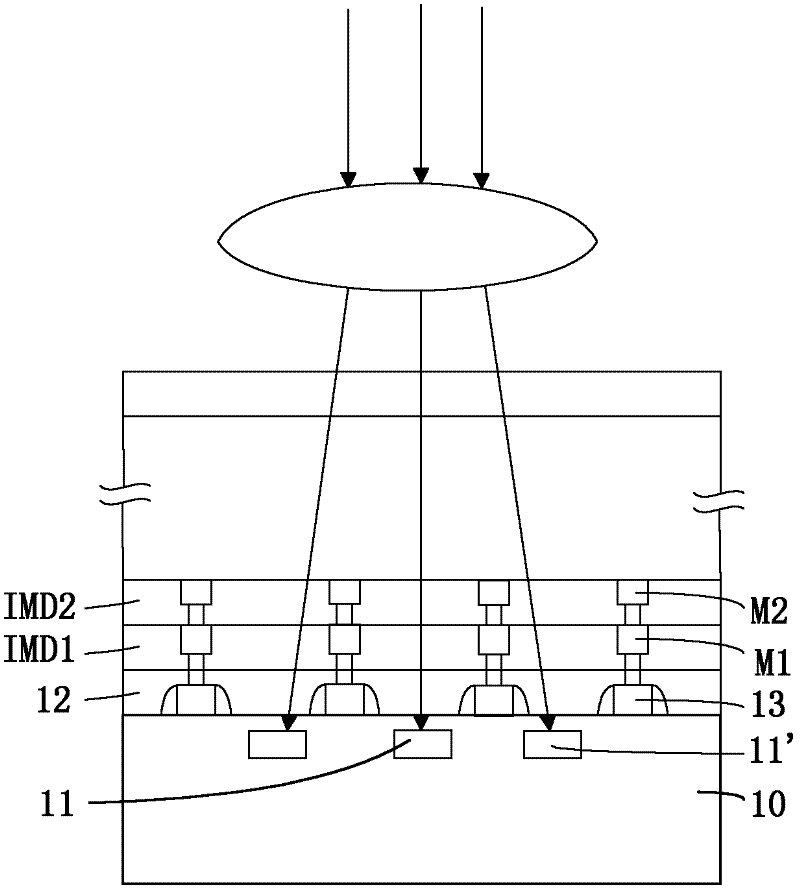

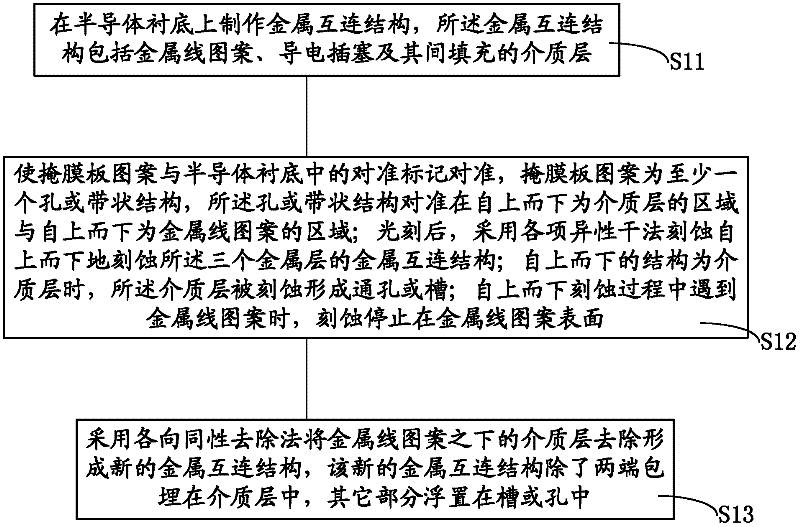

Metal interconnection structure and manufacturing method thereof

ActiveCN102543852AImprove performanceImprove the problem of high K valueSemiconductor/solid-state device detailsSolid-state devicesInterconnectionOptoelectronics

The invention provides a metal interconnection structure and a manufacturing method thereof. The manufacturing method comprises the following steps of: manufacturing a metal interconnection structure on a substrate, wherein the metal interconnection structure comprises a metal wire pattern, a conductive plug and a medium layer which is filled between the metal wire pattern and the conductive plug; performing photoetching, and etching the metal interconnection structure by adopting an anisotropic dry etching method from top to bottom, and at least forming a through hole or a groove on an area which is a medium layer from top to bottom; and removing the medium layer below the metal wire pattern by adopting an isotropic removing method to form a novel metal interconnection structure, wherein the two ends of the novel metal interconnection structure are embedded into the medium layer, and other parts of the novel metal interconnection structure float in the groove or the hole. Due to the adoption of the technical scheme of the invention, certain requirements on a suspended metal interconnection structure can be met, e.g., non-matching conditions with a lens can be reduced, the light crosstalk phenomenon is reduced, and needed materials can be filled into a suspended structure.

Owner:GALAXYCORE SHANGHAI

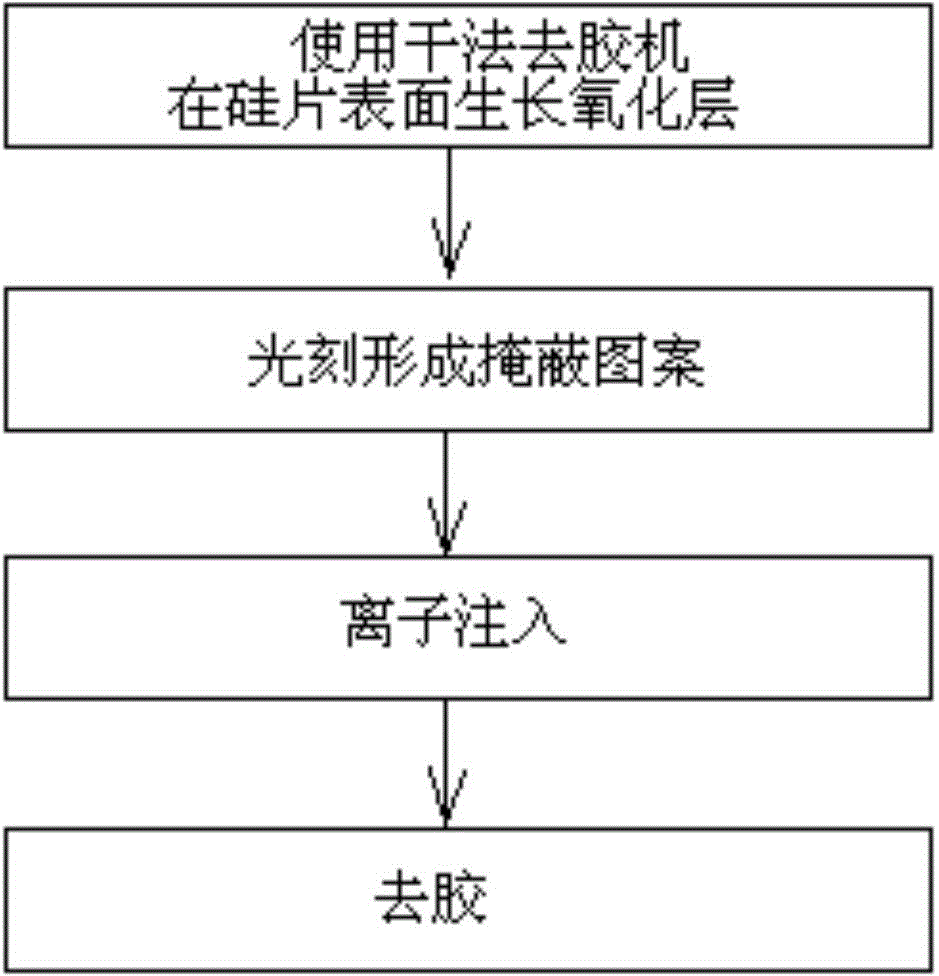

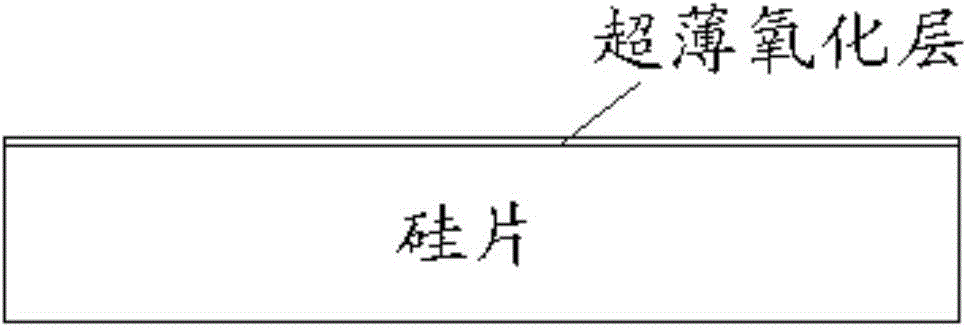

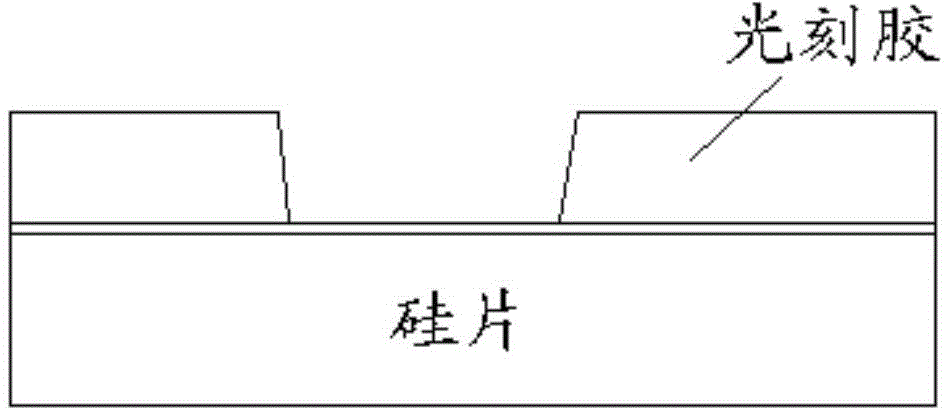

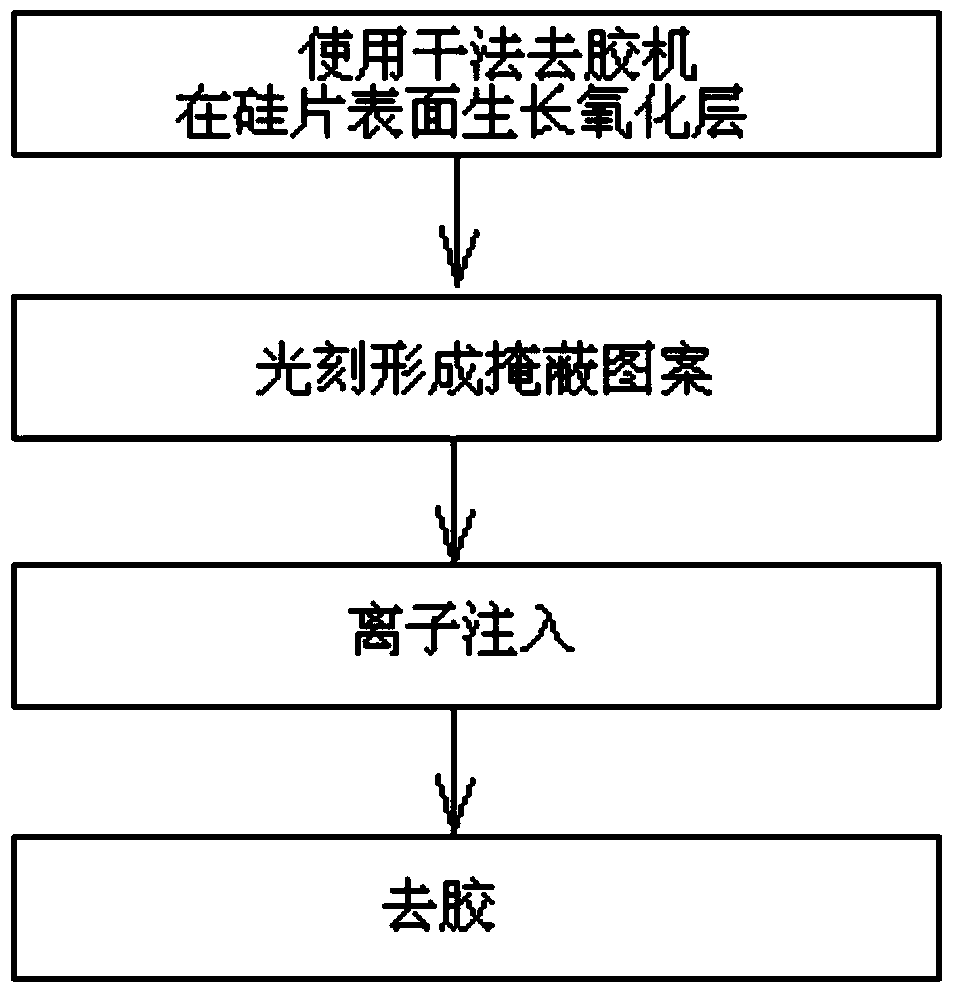

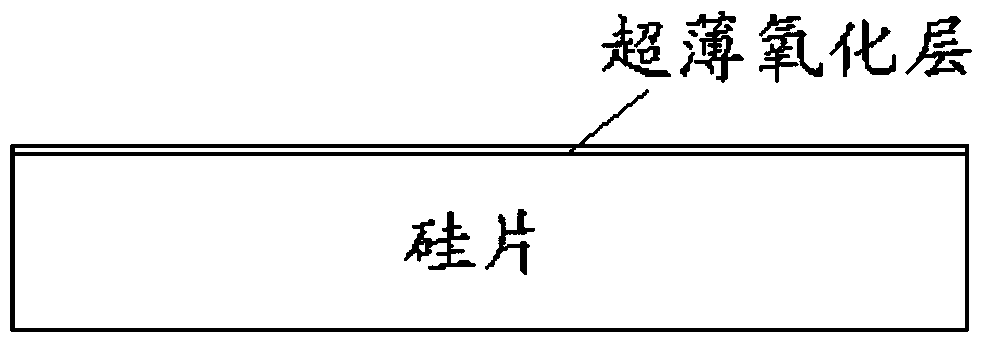

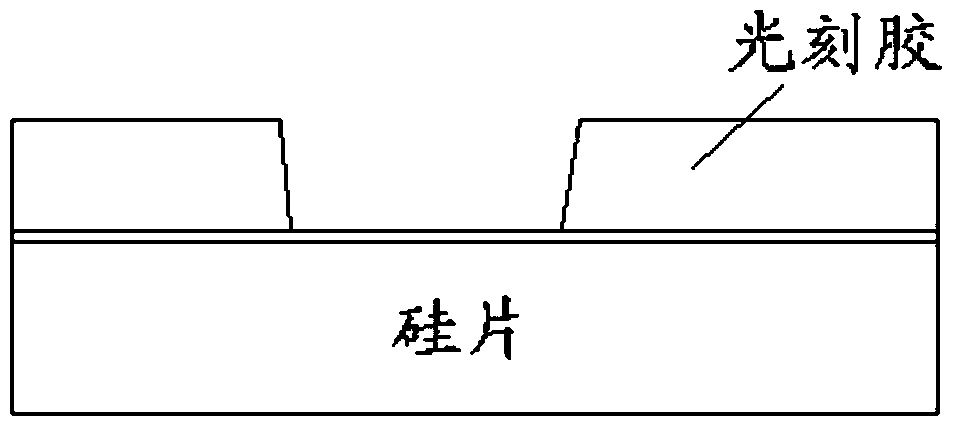

Ion implantation method capable of preventing silicon edge on boundary of ion implantation region from peeling off

ActiveCN104979171AAvoid generatingSolve peelingSemiconductor/solid-state device manufacturingSilicon chipPhotoresist

The present invention discloses an ion implantation method capable of preventing a silicon edge on the boundary of an ion implantation region from peeling off. The method comprises the following steps of: firstly, performing processing on the surface of a silicon chip, so that an oxide layer is generated on the surface of the silicon chip; then coating the silicon chip with a photoresist; then performing ion implantation on the silicon chip; and finally removing the photoresist on the surface of the silicon chip. According to the present invention, by performing processing on the surface of the silicon chip, an ultrathin oxide layer is generated on the surface of the silicon chip to prevent the silicon chip from generating the silicon edge in the photoresist-removing process, thereby avoiding the silicon peeling problem, reducing surface defects and improving the rate of finished products.

Owner:西安西岳电子技术有限公司

Array type multi-parameter wind sensor chip substrate

InactiveCN100568022CSimple preparation processImprove stabilityThermometers using electric/magnetic elementsVolume/mass flow by electric/magnetic effectsHeat sensitiveHeat balance

The invention relates to an array type multi-parameter wind sensor chip substrate, which relates to the field of wind sensors. The invention solves the problems of single measurement function, large thermal field influence, instability and long thermal equilibrium time in the prior art. The array multi-parameter wind sensor chip substrate is composed of a substrate, n heating elements, m thermal elements and several heat insulation grooves, where n is a natural number greater than or equal to 2, m=n+1, and the substrate is circular Or a regular polygonal non-conductive flat plate, on the back of the substrate, fix n heating elements symmetrical to the center point, between each two adjacent heating elements, engraved with a thermal insulation groove, on the front of the substrate, and n heating elements The position of the element corresponds to fixing n heat-sensitive elements, one heat-sensitive element is fixed in the center of the front of the substrate, and a heat-insulation groove is engraved between every two adjacent heat-sensitive elements. The array type multi-parameter wind sensor chip substrate of the present invention can be applied to wind sensors and wind parameter measurement systems.

Owner:HARBIN UNIV OF SCI & TECH

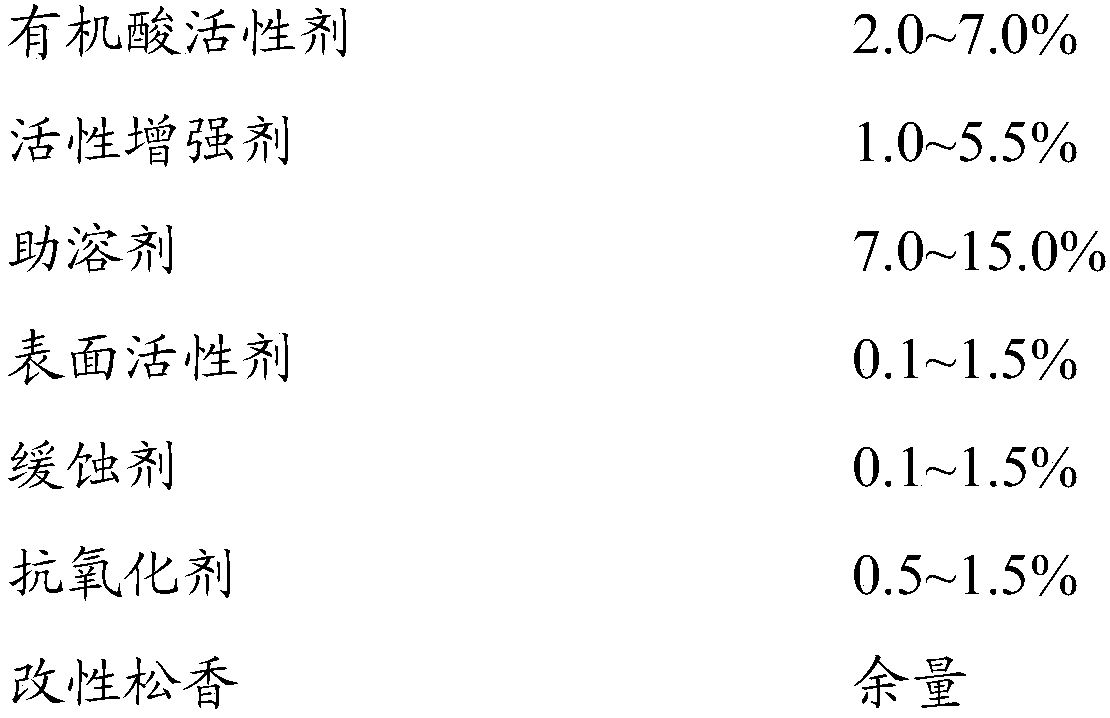

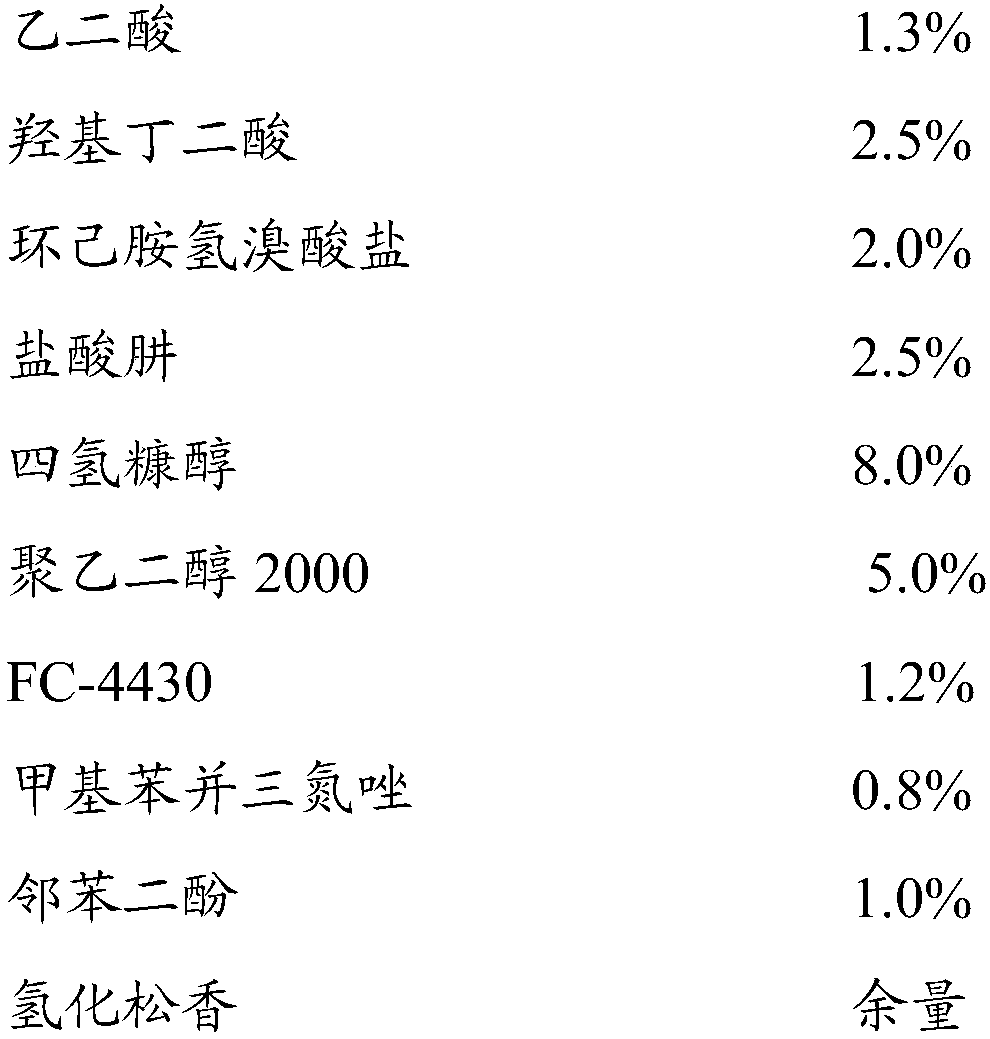

A kind of high-performance solder wire flux for automatic soldering and preparation method thereof

ActiveCN105458552BSuccessful realization of automatic solderingFast tinningWelding/cutting media/materialsSoldering mediaElectrical resistance and conductanceOrganic acid

Owner:SHENZHEN XINGHONGTAI TIN +1

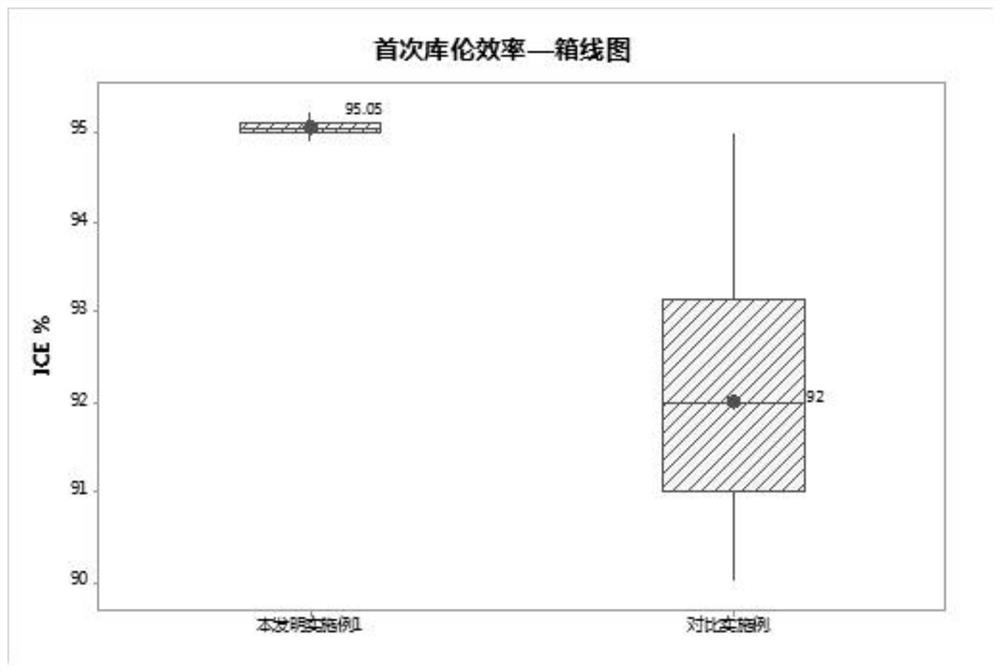

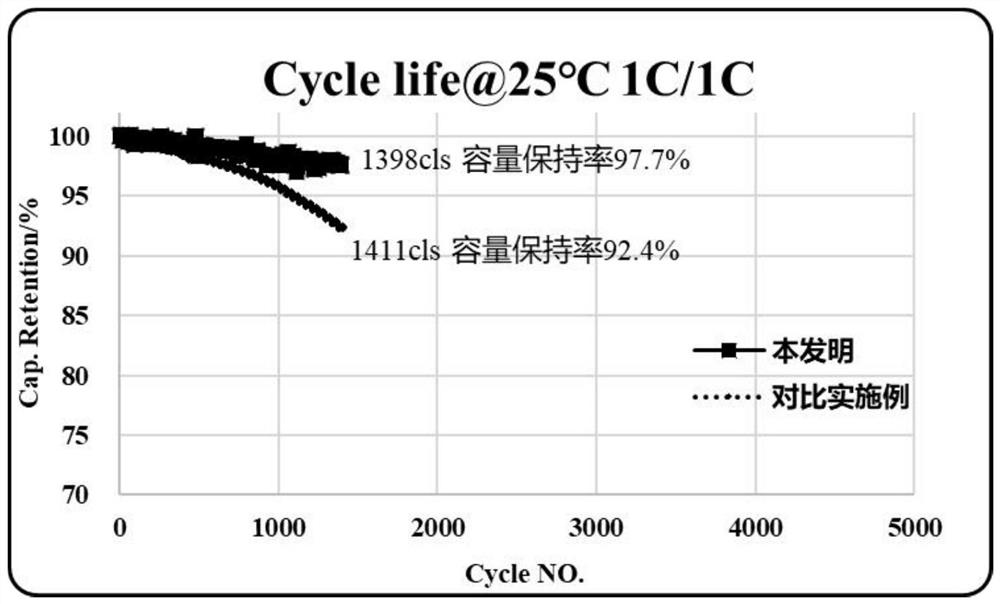

Pre-sodium-modified positive pole piece, application of pre-sodium-modified positive pole piece, sodium-ion battery and preparation method of sodium-ion battery

PendingCN114649504AImprove reliabilityImprove integrityCell electrodesFinal product manufactureElectrical batteryPhysical chemistry

The invention belongs to the technical field of battery materials. The invention provides a pre-sodium-modified positive pole piece. The pre-sodium-modified positive pole piece comprises high-voltage sodium ion positive pole slurry, high-capacity sodium ion positive pole slurry and a current collector, and the thickness of the high-voltage sodium ion positive electrode slurry is 10-15% of the sum of the thicknesses of the high-voltage sodium ion positive electrode slurry and the high-capacity sodium ion positive electrode slurry. Due to the effective use of the positive electrode sodium supplementing technology, the irreversible sodium loss of the hard carbon negative electrode is reduced, the dynamic performance of the sodium ion battery is improved, and the polarization is reduced; therefore, the high-performance sodium ion battery has the initial coulombic efficiency of more than 95%, the energy density of more than 150Wh / kg, the cycle life of more than 6000 weeks, the charge-discharge capacity at-40 DEG C and the continuous discharge capacity at 30C multiplying power, and the comprehensive electrochemical performance of the sodium ion battery is improved.

Owner:溧阳中科海钠科技有限责任公司

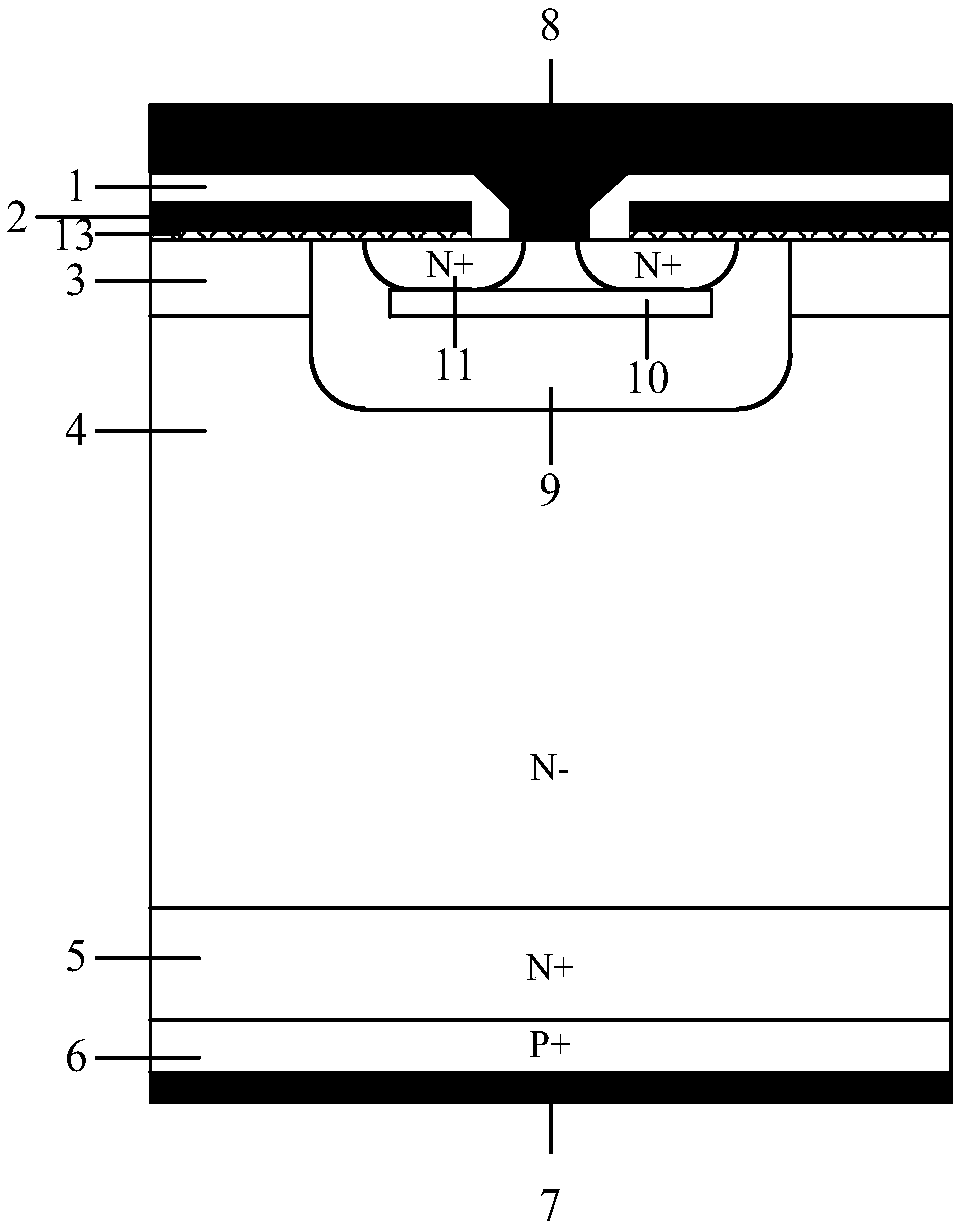

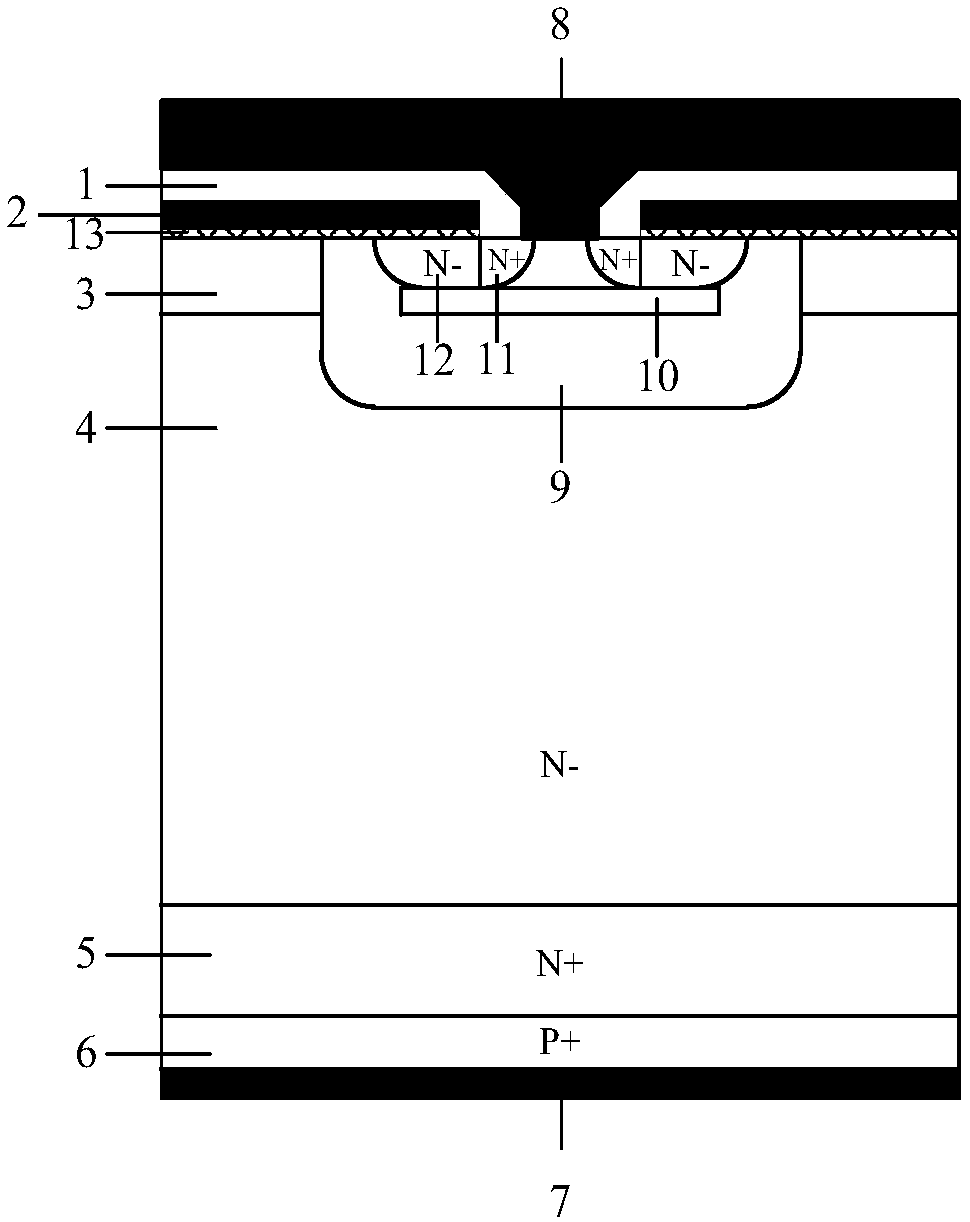

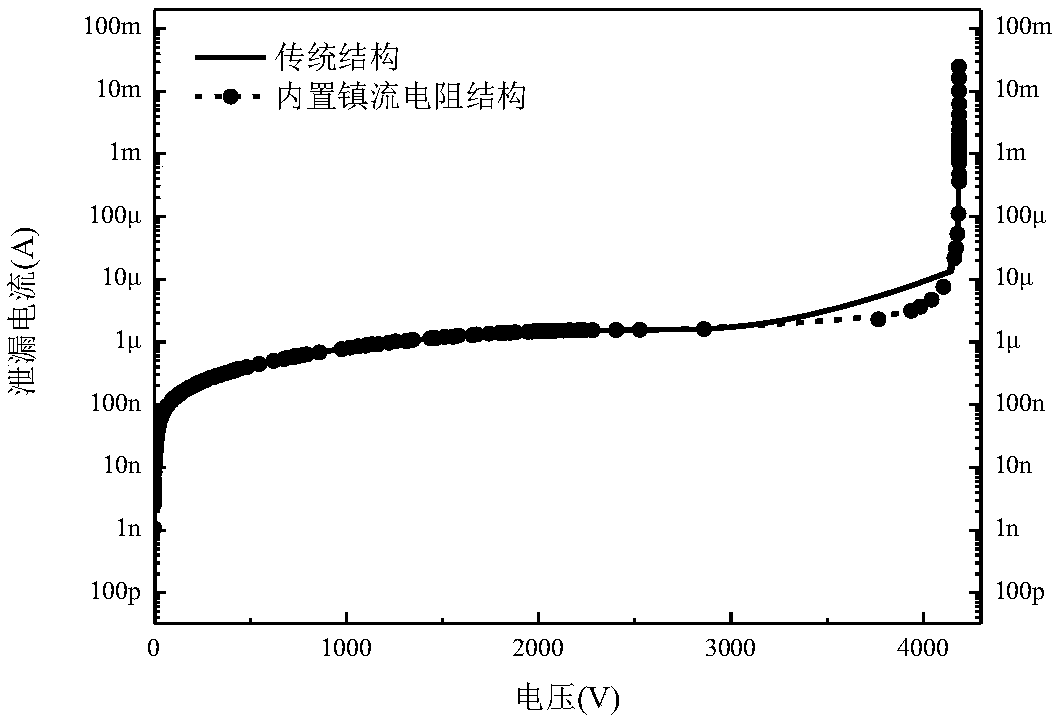

High-voltage IGBT device with a built-in ballast resistor

ActiveCN108172610AImprove short circuit performanceImprove thermal stabilitySemiconductor devicesHigh voltage igbtEngineering

The invention provides a high-voltage IGBT device with a built-in ballast resistor. A cell structure includes a first conductivity type semiconductor P+ collector region, a metal collector, a second conductivity type semiconductor buffer layer, a second conductivity type semiconductor N-drift region, a first conductivity type semiconductor P type base region, a heavily doped first conductivity type semiconductor P+ doping region, a second conductivity type semiconductor built-in ballast resistance region, and a heavily doped second conductivity type semiconductor N+ emitter region. The secondconductivity type semiconductor built-in ballast resistance region is used for replacing the part, extending horizontally towards the space below the gate structure, of the second conductivity type semiconductor N+ emitter region, so that the second conductivity type semiconductor built-in ballast resistance region is located in the gate voltage control region. On the basis of the positive temperature characteristic of the ballast resistance value at a high temperature, the short-circuit capability of the device is improved; and the thermal stability of the device in the forward blocking stateis enhanced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Process for making composite material by compounding PET and board

InactiveCN106364132AStrong appearance permeabilityStrong process compatibilityNon-macromolecular adhesive additivesLaminationHot stampingEngineering

The invention discloses a process for making a composite material by compounding PET and a board. The process comprises the following steps: 1), placing the PET coiled material on a film laminating machine, and dispensing unshaded UV glue on the board with the same width; 2), sending to the film laminating machine later and compounding with the PET coiled material, and evenly laminating the UV glue through the pressure of a rubber covered roller; 3) repeating the step 1) and step 2), until the needed layer number is obtained; and 4) curing and compounding UV, and obtaining a product. The provided process is capable of laminating and compounding the different thicknesses of the PET coiled materials and the different thicknesses of the boards, and performing the different processing steps, such as the silk-screening, glue-screening, digital spraying, hot stamping, and gravure, to the PET material before the compounding, and independently printing after the compounding. Various processes have strong compatibility.

Owner:WUXI KEHONG LABEL

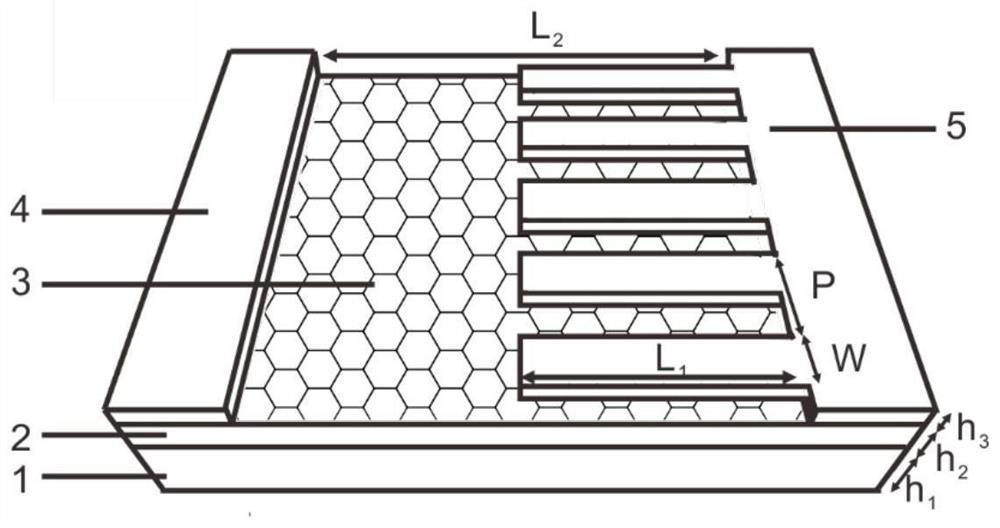

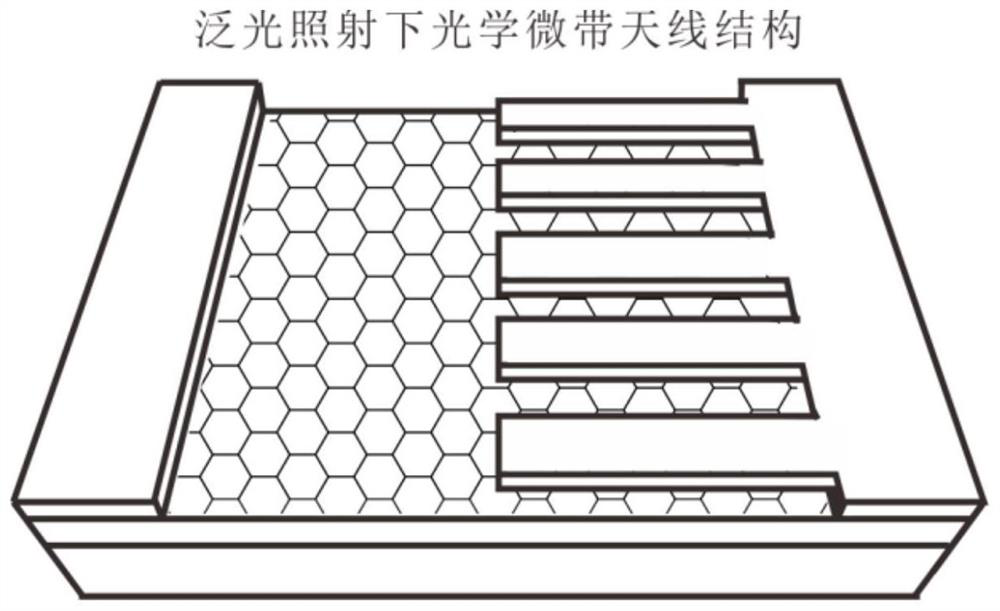

Two-dimensional material detector based on asymmetric integration of optical microstrip antenna

ActiveCN112242456AEnhanced light absorptionExpand the borderAntenna supports/mountingsSubstantially flat resonant elementsPhoto irradiationResponsivity

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

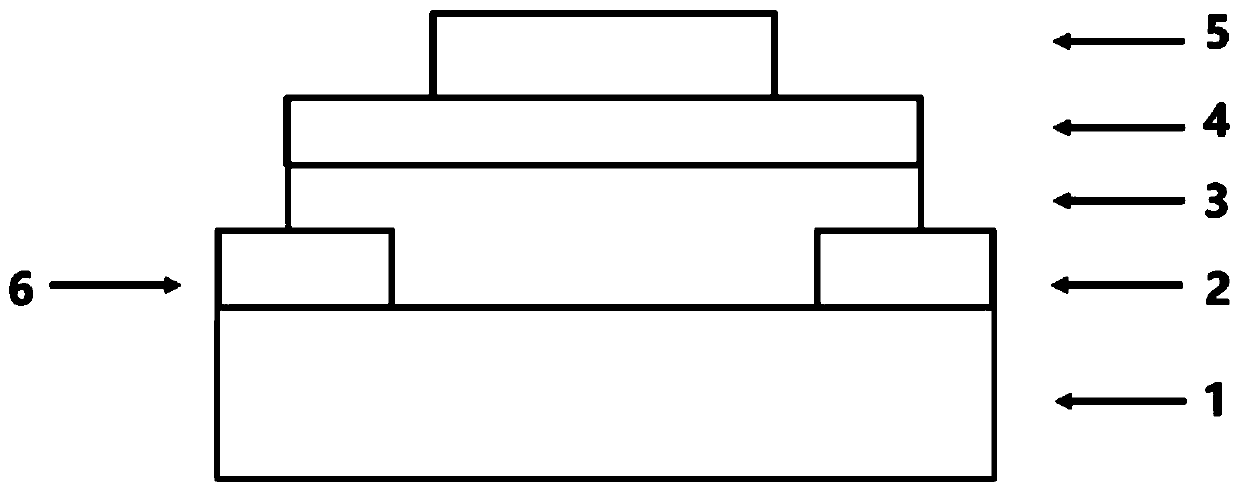

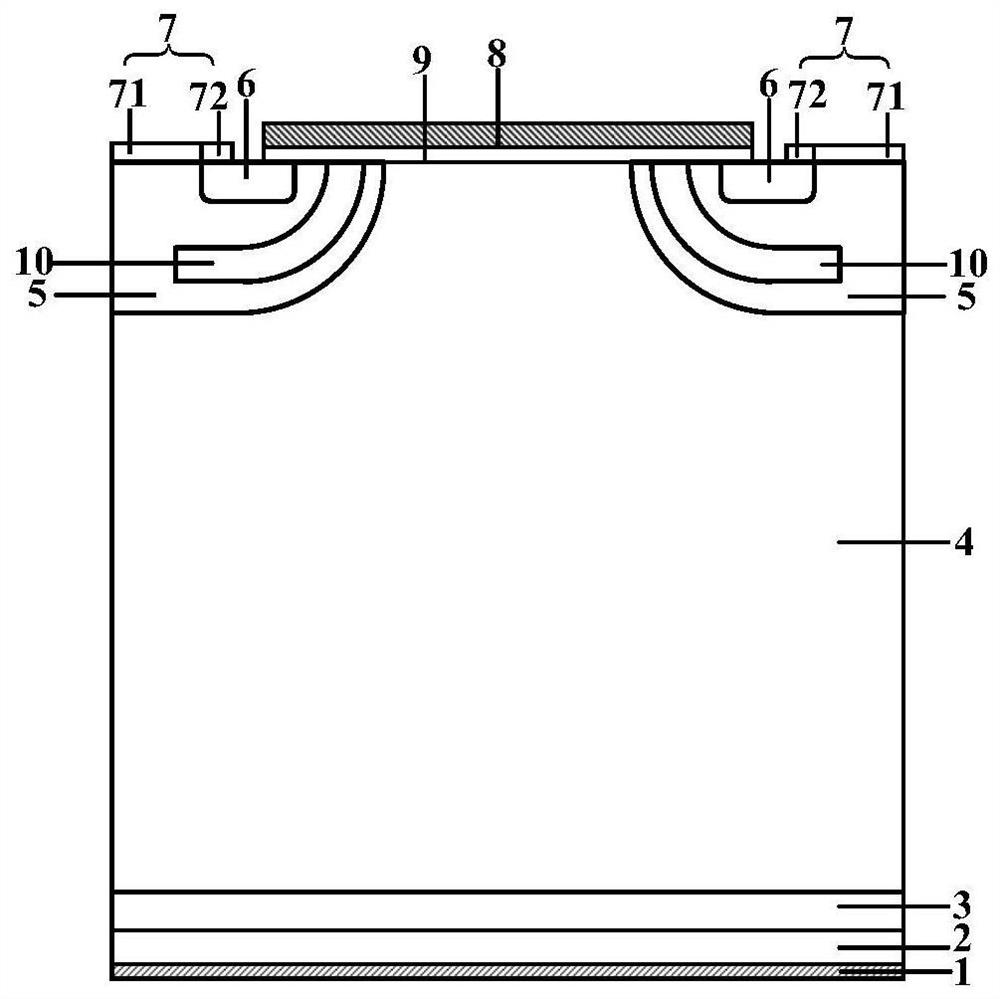

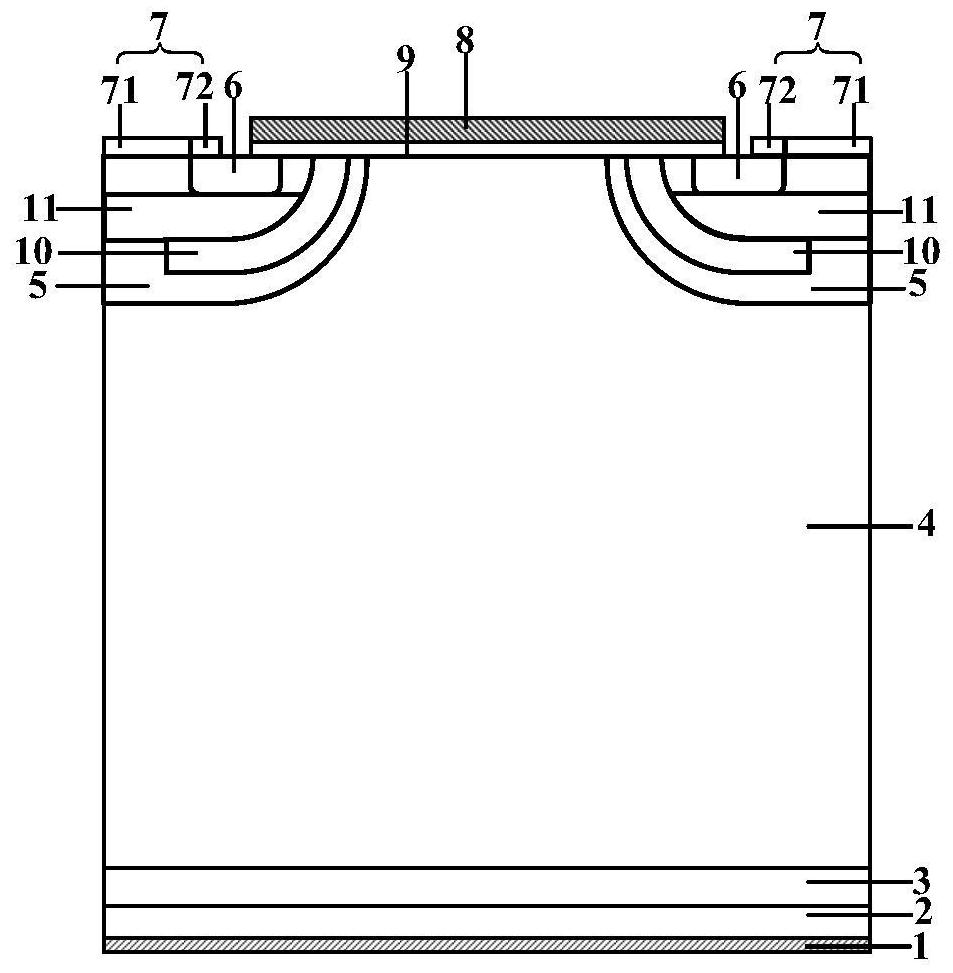

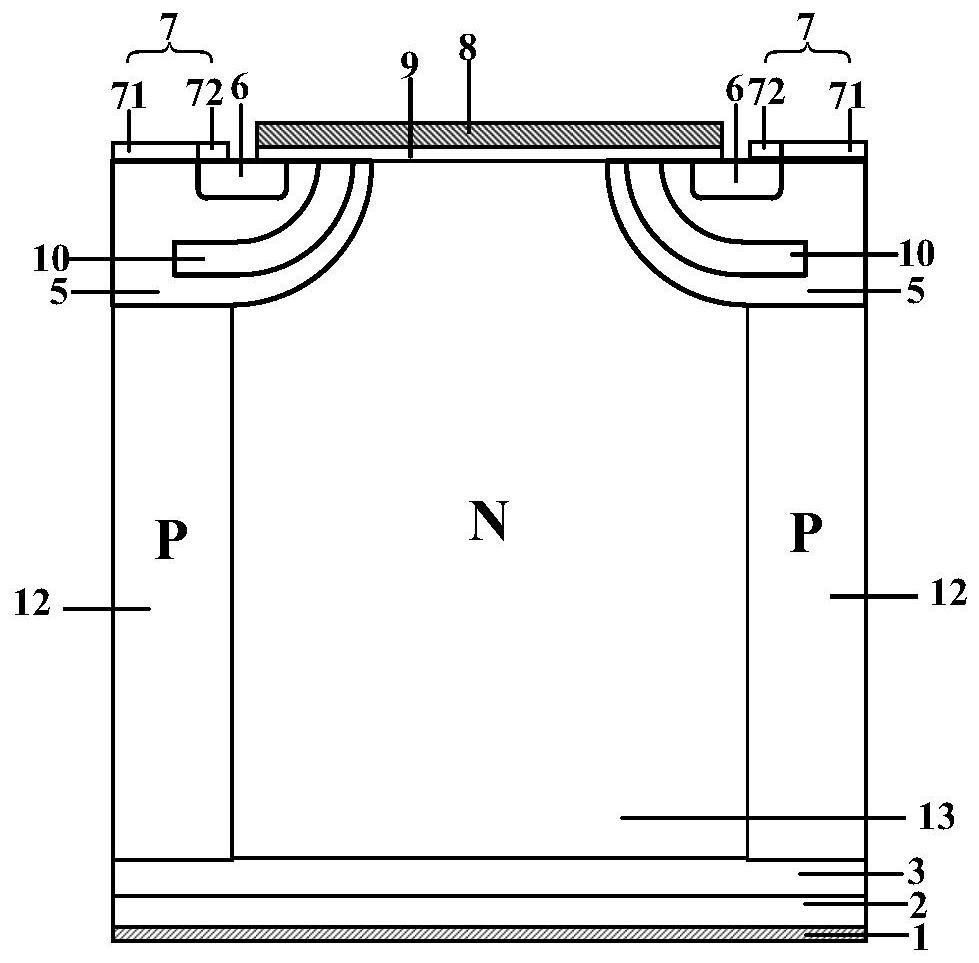

Insulated gate bipolar transistor and preparation method thereof

PendingCN112510077AReduce conduction voltage dropInhibition of latch-upTransistorSemiconductor/solid-state device manufacturingVoltage dropEngineering

The invention provides an insulated gate bipolar transistor and a preparation method thereof. The insulated gate bipolar transistor comprises an N-drift region (4), P-type base regions (5), N-buffer layers (10) and N+emitter regions (6); the P-type base regions (5) are located on the two sides of the upper surface of the N-drift region (4), and the N+emitter regions (6) are located on the upper surfaces of the P-type base regions (5) and have a set distance away from the outer sides of the P-type base regions (5); and the N-buffer layers (10) are located in the P-type base regions (5) below the N+emitter regions (6), the conduction voltage drop of the insulated gate bipolar transistor is reduced through the N-buffer layers (10), and the latch-up phenomenon of the insulated gate bipolar transistor is effectively inhibited. According to the insulated gate bipolar transistor, the carrier concentration in the drift region is improved through Schottky contact, and the distribution of carriers in the drift region of the insulated gate bipolar transistor is further improved, so that the conductivity modulation effect is enhanced, the conduction voltage drop is reduced, the firmness of theinsulated gate bipolar transistor is improved through the N-buffer layers, and the large-current turn-off capability of the insulated gate bipolar transistor is improved.

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD +3

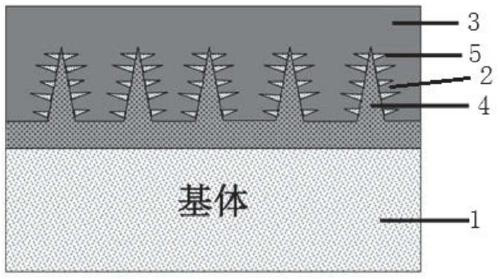

A method for inhibiting the growth of tin whiskers based on micro-nano needle cone structure

InactiveCN106676598BSuitable for growthLarge specific surface areaSuperimposed coating processSemiconductor devicesMicro nanoSurface oxidation

The invention discloses a method for restraining tin whisker growing based on a micro-nano cone structure. The method comprises the following steps that a conductive matrix is selected and cleaned; after the matrix is cleaned, a micro-nano cone structure layer grows on the conductive matrix; then the micro-nano cone structure layer is cleaned, and a surface oxide layer is removed; and finally, tin-based welding flux grows on the micro-nano cone structure layer. According to the method, the pressure stress in a tin cladding layer is released by utilizing the fact that the micro-nano cone structure layer has a large specific surface area and a unique geometrical shape, driving force for tin cladding layer tin cladding layer is reduced, and formation of tin whisker is restrained; the method is suitable for growing of various types of tin layer thin films and has the advantages that the preparation method is simple, the temperature is low, compatibility of the technique is high, stability is high, and growing of tin whiskers can be effectively restrained.

Owner:SHANGHAI JIAOTONG UNIV

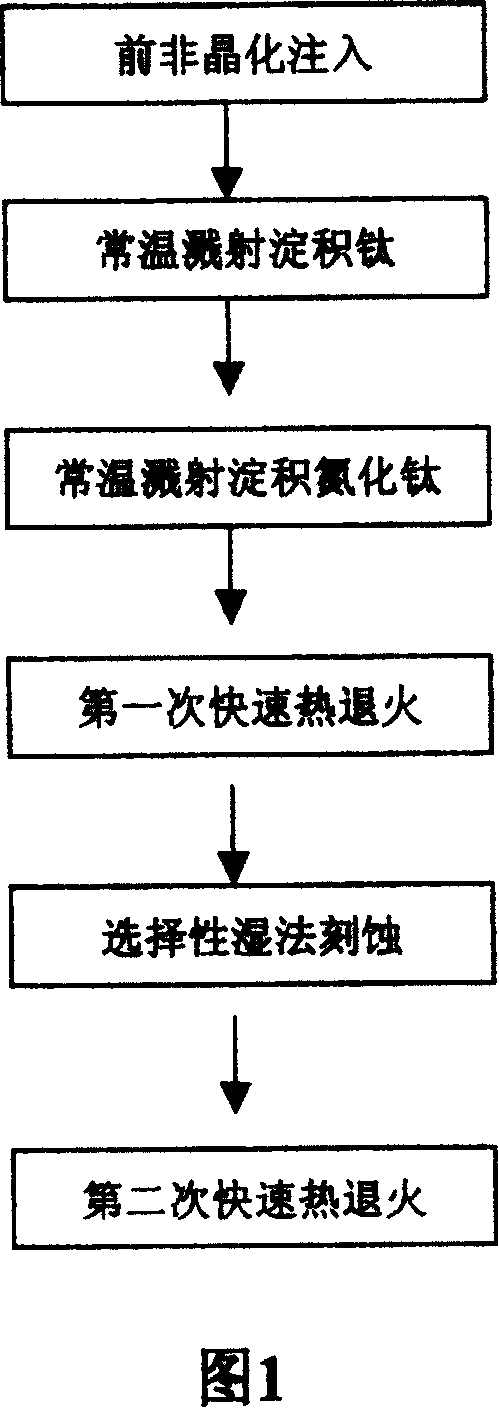

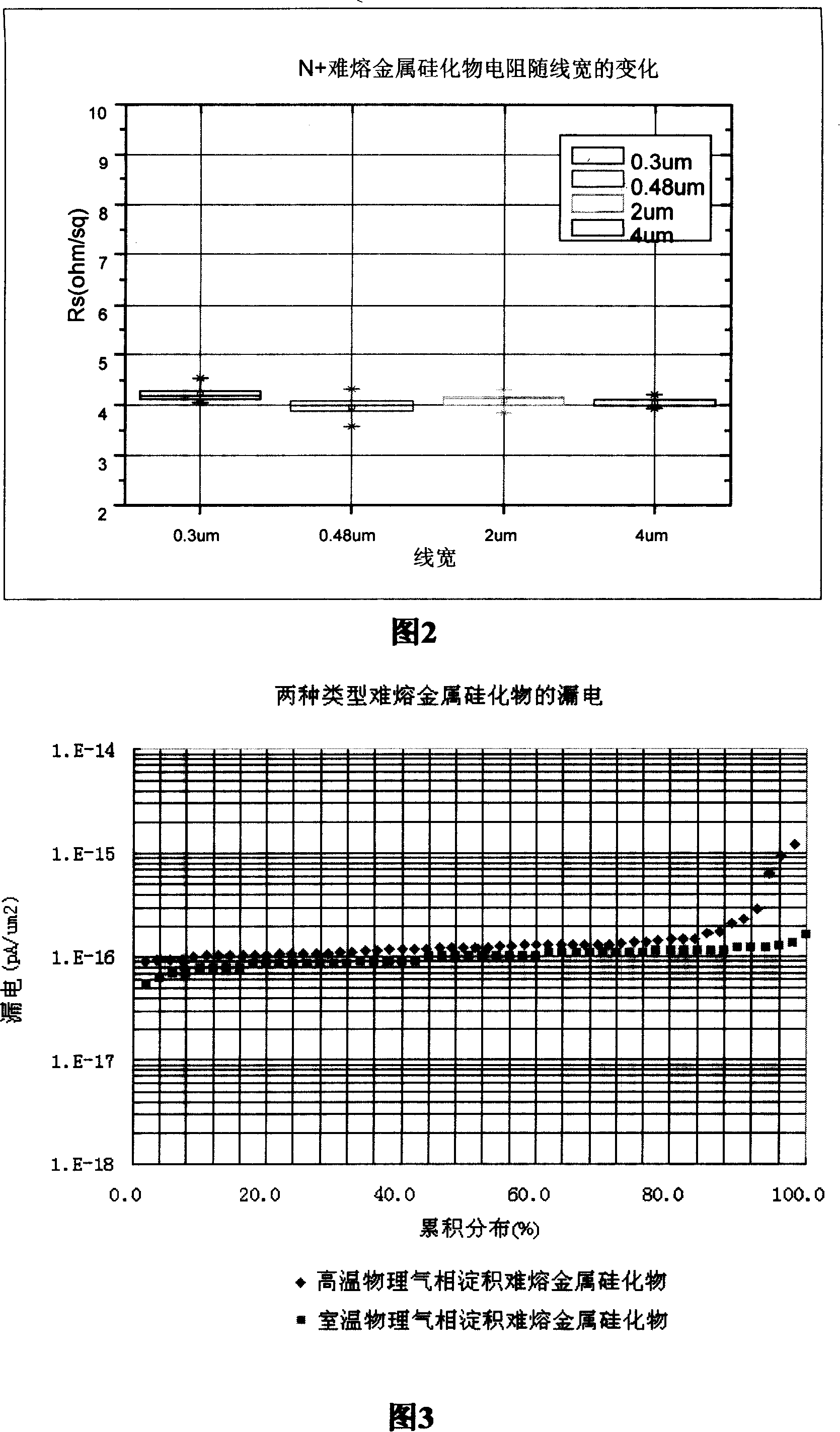

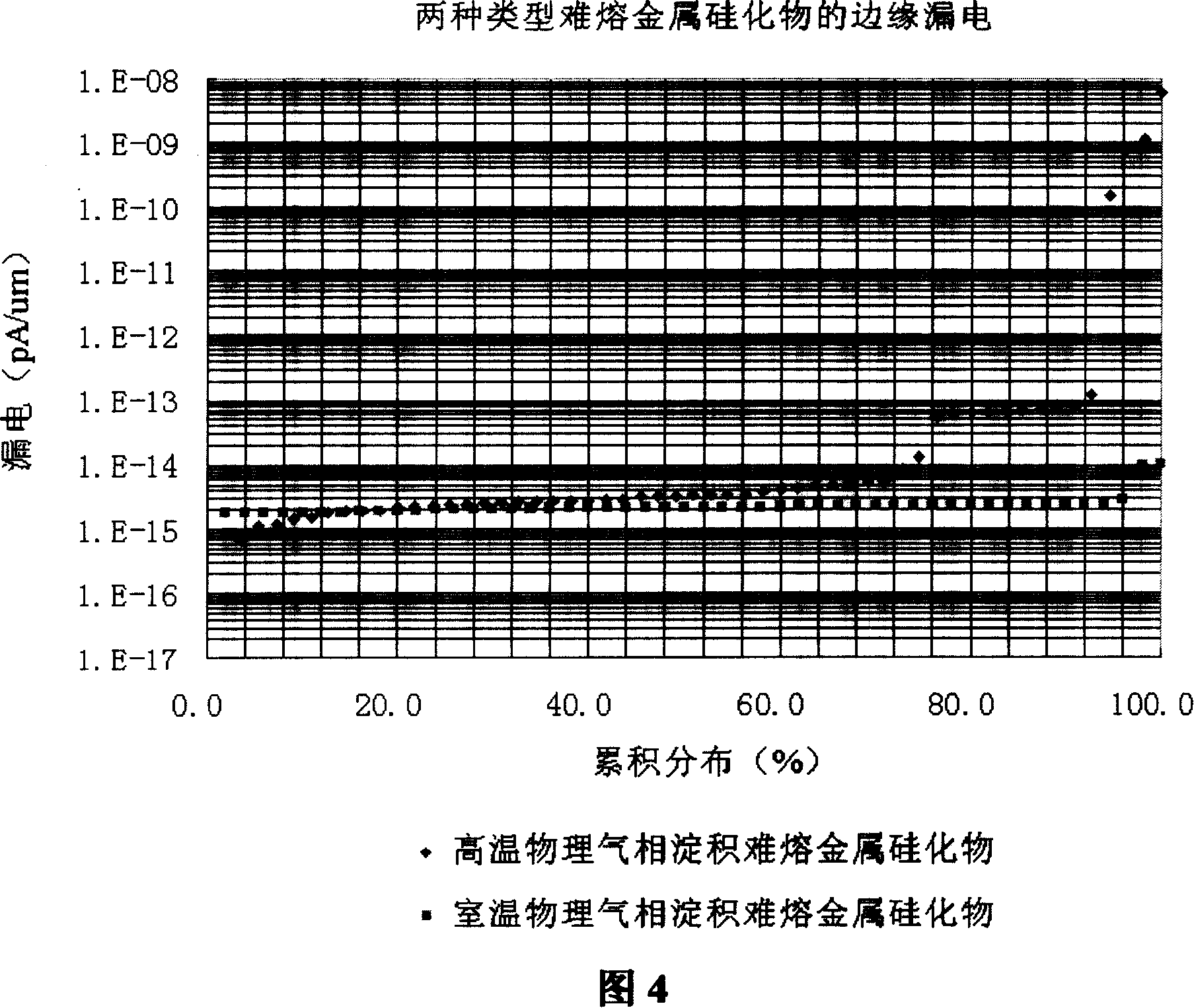

Titanium silicide realization method in CMOS process by means of titanium deposition at normal temperature

ActiveCN100353523CSuppression of narrow channel effectsLow costSemiconductor/solid-state device manufacturingEtchingTitanium nitride

The invention relates to realization method for the titanium silicide in CMOS technique, which comprises, first, injecting amorphous compound on CMOS with formed source / drain / grid; then, sputtering to deposit titan at normal temperature for CMOS and adding the sputter and deposit for titanium nitride; annealing quickly for the first time; wet etching by NH4OH / H2O2 / H2O; finally, annealing quickly for the second time to form titanium silicide. This method restrains effectively the narrow channel effect, saves time and cost.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

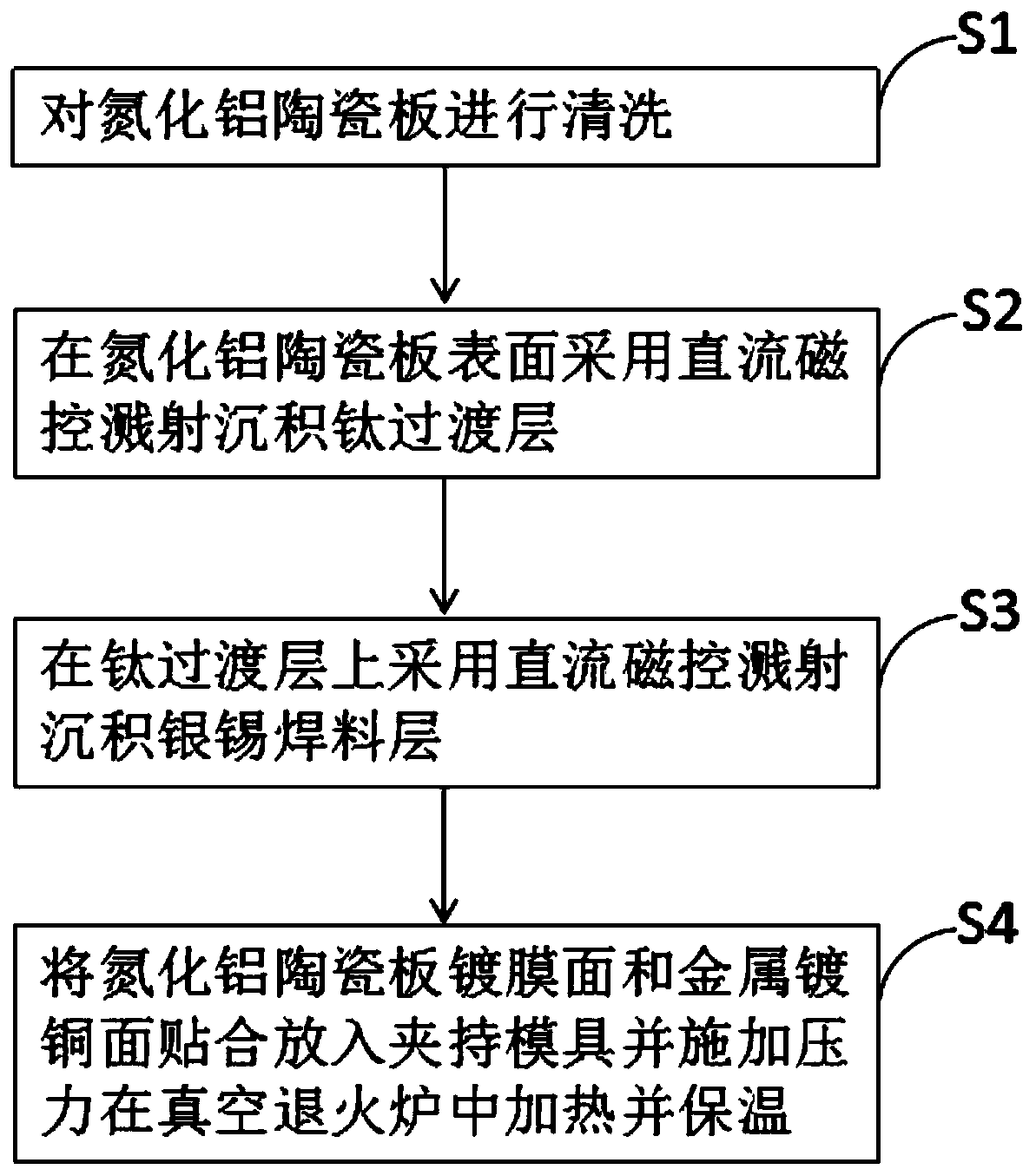

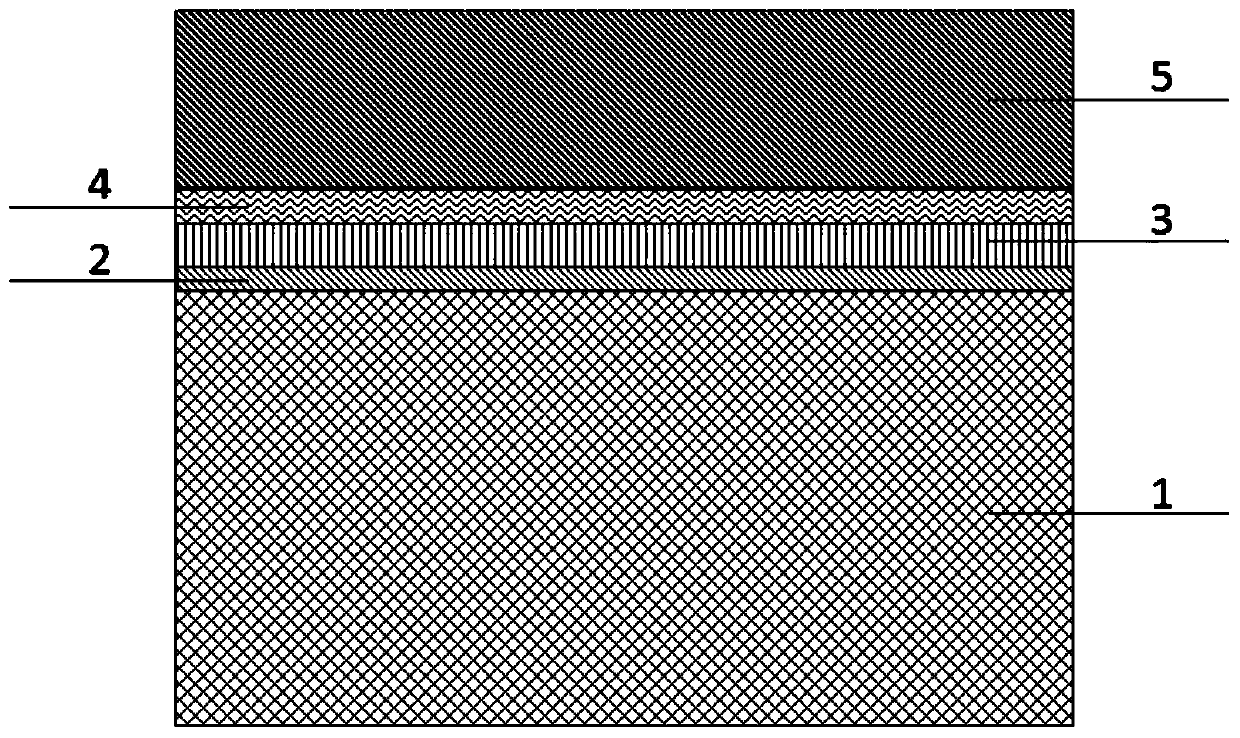

A method for connecting aluminum nitride ceramic plate and metal based on PVD deposition method

ActiveCN109136848BMature technologySimple control conditionsVacuum evaporation coatingSputtering coatingCoated surfaceAir tightness

The invention discloses a method for connecting an aluminum nitride ceramic plate and metal based on PVD deposition, The method includes the following steps that, firstly, a layer of titanium film isformed on the surface of the aluminum nitride ceramic plate through PVD deposition, a silver-tin layer with a certain thickness is deposited, then a clamping die is used for combining the coated surface of the aluminum nitride ceramic plate with a metal plate (block) coated with copper film and applying certain pressure, finally the aluminum nitride ceramic plate combined with the metal plate is placed in a vacuum annealing furnace for heating and heat preservation, and the high-strength connection between the aluminum nitride ceramic plate and the metal can be achieved. After the high-strength connection between the aluminum nitride ceramic plate and the metal is achieved, a traditional ceramic-metal connection process is simplified, the problem of air tightness of the bonding surface caused by oxide bonding in a direct copper cladding method is avoided, and the thermal conductivity and heat dissipation performance of the substrate are improved.

Owner:苏州博志金钻科技有限责任公司

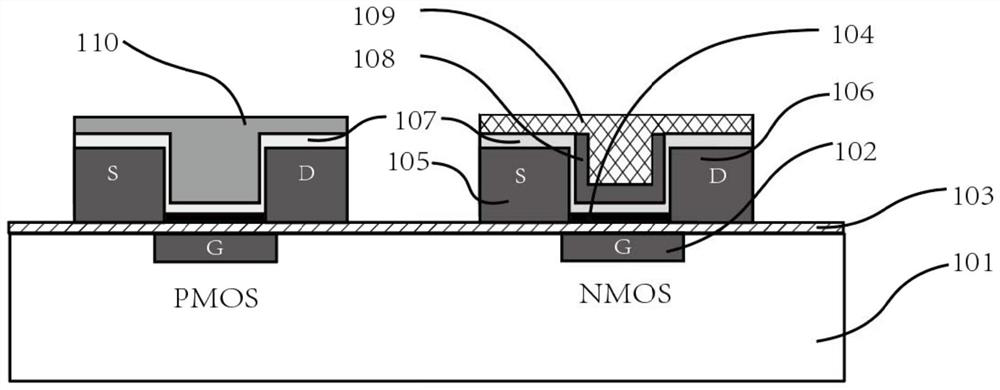

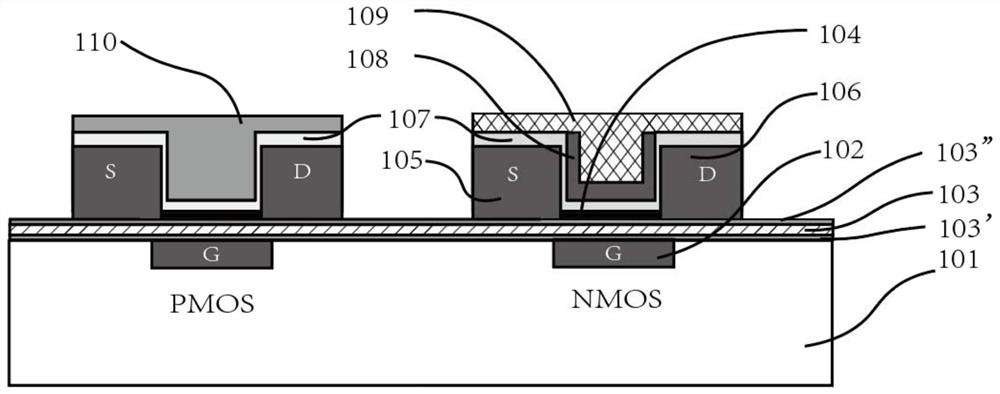

Transistor with local bottom gate and manufacturing method thereof

PendingCN113690300APlay a protective effectImprove interface propertiesSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricBottom gate

The invention relates to a transistor with a local bottom gate and a manufacturing method of the transistor. The transistor comprises a substrate, a low-dimensional semiconductor layer, a source electrode, a drain electrode and the local bottom gate; the local bottom gate is located on the substrate, a gate dielectric layer is arranged on the local bottom gate, the low-dimensional semiconductor layer is located on the gate dielectric layer to serve as a channel of a transistor device, the source electrode and the drain electrode are located on the two opposite sides of the low-dimensional semiconductor channel and make contact with one or more parts of the low-dimensional semiconductor layer respectively; a transition layer and an electrostatic doping layer are arranged on the source electrode, the drain electrode and the channel layer, and fixed charges are arranged in the electrostatic doping layer, so that electrostatic doping is carried out on the corresponding low-dimensional semiconductor channel layer to form an NMOS device, and meanwhile, the invention also provides a manufacturing method of the transistor. The transistor provided by the invention has the advantages of good thermal stability, accurate and controllable threshold voltage and compatibility in process, and can meet the requirements of large-scale carbon-based integrated circuit production.

Owner:BEIJING HUA TAN YUAN XIN ELECTRONICS TECH CO LTD

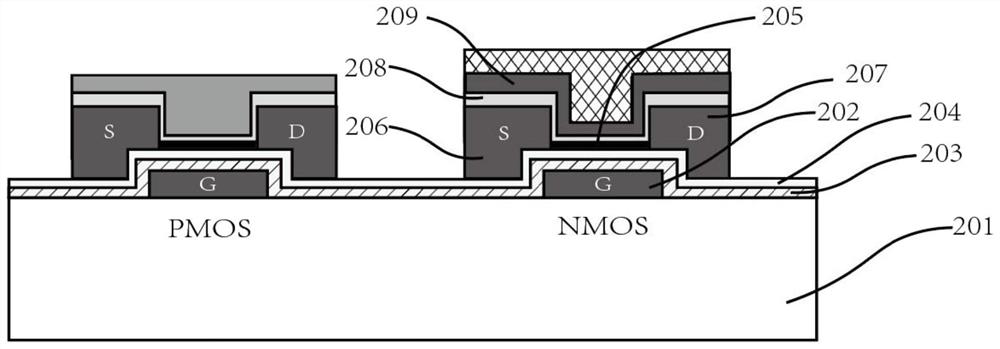

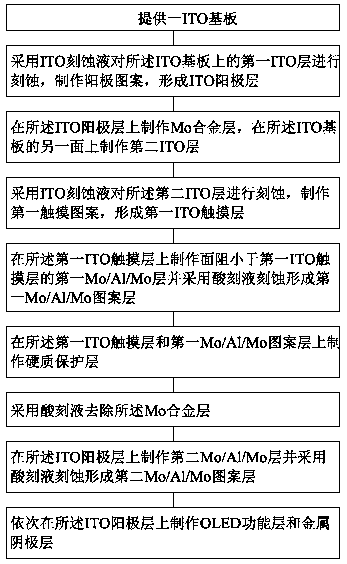

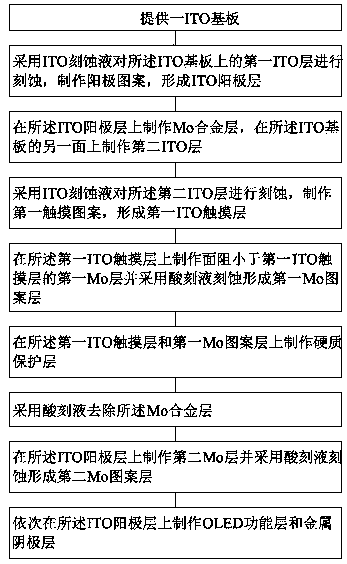

OLED product and production method thereof

ActiveCN108539055AImprove protectionHigh melting pointSolid-state devicesSemiconductor/solid-state device manufacturingAlloyOn cells

The invention provides an OLED product and a production method thereof. The production method comprises the following steps: 1, providing an ITO substrate; 2, etching a first ITO layer on the ITO substrate to form an ITO anode layer; 3, producing an Mo alloy layer on the ITO anode layer, and producing a second ITO layer on the other surface of the ITO substrate; 4, etching the second ITO layer toform a first ITO touch layer; 5, producing and etching a first Mo / Al / Mo pattern layer on the first ITO touch layer; 6, producing a hard protective layer on the first ITO touch layer and the first Mo / Al / Mo pattern layer; 7, removing the Mo alloy layer; 8, producing and etching a second Mo / Al / Mo pattern layer on the ITO anode layer; 9: producing an OLED functional layer and a metal cathode layer. Bythe production method, the problem of poor compatibility between the existing technical scheme of adding auxiliary metal in the process of producing an OLED product by an ON CELL technology and an Moalloy protection scheme can be solved, and the product quality and the production efficiency can be effectively improved.

Owner:TRULY SEMICON

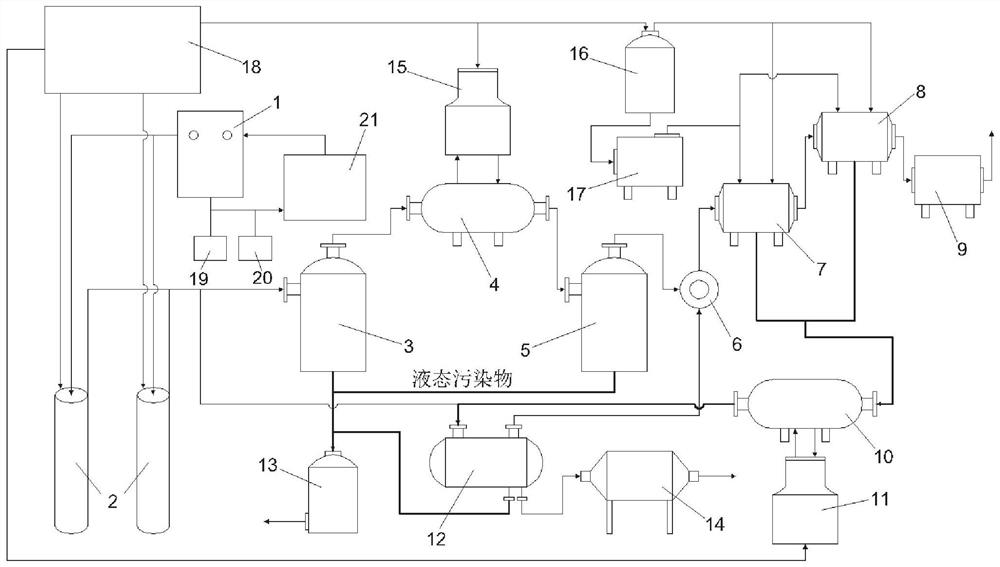

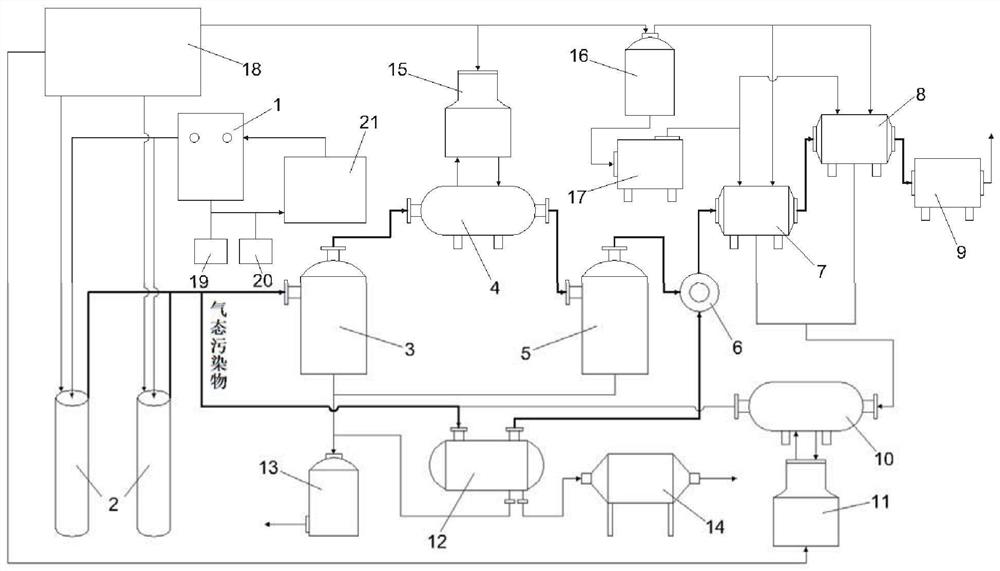

Device and method for remediating organically polluted soil with resistance heating coupling oxidant

ActiveCN113182343BImprove oxidation efficiencyStrong process compatibilitySolid waste disposalContaminated soil reclamationEnvironmental engineeringElectric transport

The invention discloses a high-efficiency and energy-saving resistance heating coupled electric transport oxidant delivery device and method for repairing organic polluted soil, comprising a heating unit, an extraction unit, a monitoring unit and a ground treatment unit. Simply using resistance heating requires a long heating time, and simply using chemical oxidation cannot effectively transport the oxidant to the polluted area. Resistance heating can activate oxidants, increase the vapor pressure and solubility of pollutants, and promote their volatilization and dissolution, thereby improving oxidation efficiency and enhancing the contact ability with pollutants, shortening the repair period and reducing repair costs. At the same time, the oxidant can improve the efficiency of resistance heating repair, and the electric transport of oxidant can transport the oxidant to the target contaminated area to enhance precise repair, reduce the energy consumption required for resistance heating, and have strong process compatibility with resistance heating equipment. The invention can be installed according to the specific conditions of local polluted areas, has low investment cost, is suitable for repairing soil polluted by organic non-heavy metals, and has great popularization value.

Owner:RES CENT FOR ECO ENVIRONMENTAL SCI THE CHINESE ACAD OF SCI

An ion implantation method capable of preventing peeling of silicon ribs at the boundary of the ion implantation region

ActiveCN104979171BAvoid generatingSolve peelingSemiconductor/solid-state device manufacturingSilicon chipPhotoresist

The present invention discloses an ion implantation method capable of preventing a silicon edge on the boundary of an ion implantation region from peeling off. The method comprises the following steps of: firstly, performing processing on the surface of a silicon chip, so that an oxide layer is generated on the surface of the silicon chip; then coating the silicon chip with a photoresist; then performing ion implantation on the silicon chip; and finally removing the photoresist on the surface of the silicon chip. According to the present invention, by performing processing on the surface of the silicon chip, an ultrathin oxide layer is generated on the surface of the silicon chip to prevent the silicon chip from generating the silicon edge in the photoresist-removing process, thereby avoiding the silicon peeling problem, reducing surface defects and improving the rate of finished products.

Owner:西安西岳电子技术有限公司