Titanium silicide realization method in CMOS process by means of titanium deposition at normal temperature

An implementation method and technology of titanium silicide, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as increasing the leakage current of shallow junctions, and achieve the goal of suppressing narrow channel effects, improving component leakage, and reducing costs. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The present invention will be further described below with reference to the accompanying drawings and embodiments.

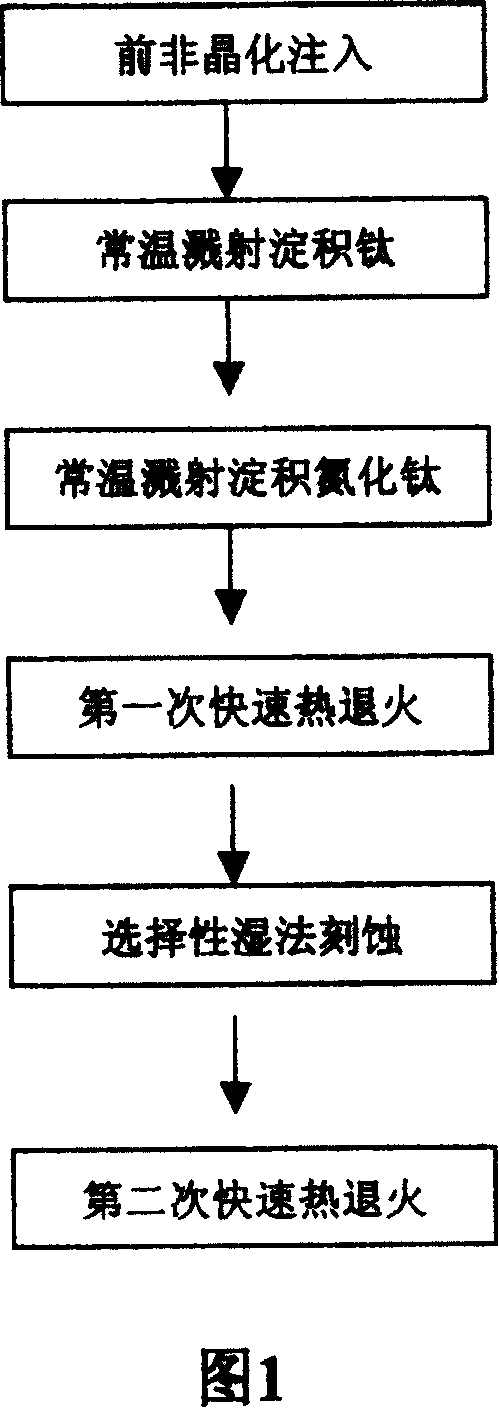

[0020] Referring to FIG. 1 , which is a flow chart of an embodiment of the present invention, a method for realizing titanium silicide by depositing titanium at room temperature in a CMOS process. The following steps:

[0021] Pre-amorphization implantation is performed on the CMOS where the source, drain and gate are formed. As+ implantation is used, and the dose of As+ is 3e14atom / cm3 to amorphize the area where titanium silicide is to be formed, and its energy is equal to The subsequent formation of titanium silicide has a great influence. While not changing the characteristics of the device, optimize its energy to make it the most favorable for the formation of titanium silicide. At the same time, if Ge+ ions are used for implantation, the ideal effect can also be achieved;

[0022] Titanium is deposited by sputtering at room temperature, and titaniu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More