Shallow trench isolation manufacturing method and cmos manufacturing method

A shallow trench and isolation trench technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as increasing leakage, reducing the threshold voltage of semiconductor devices, and the loss of the top of the oxide layer 5, and reaching a stable threshold value Voltage, performance improvement, effect of suppressing narrow channel effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

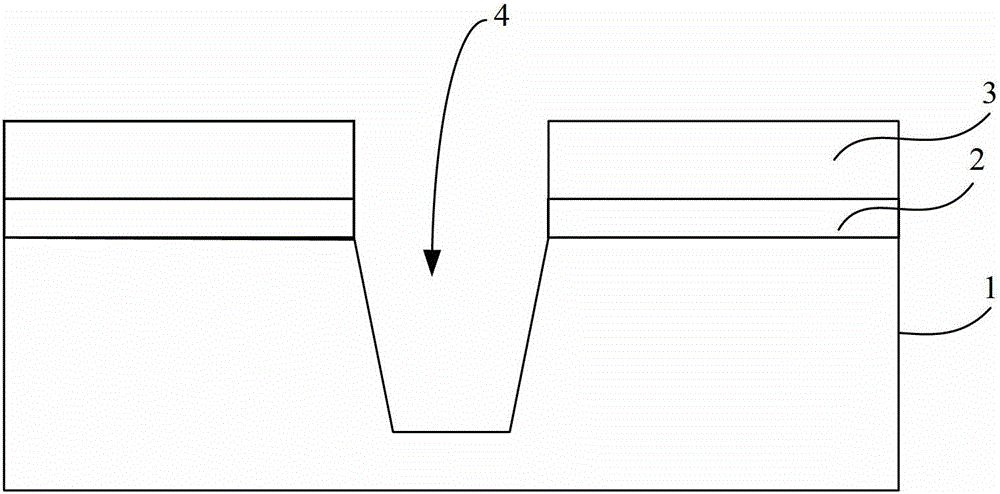

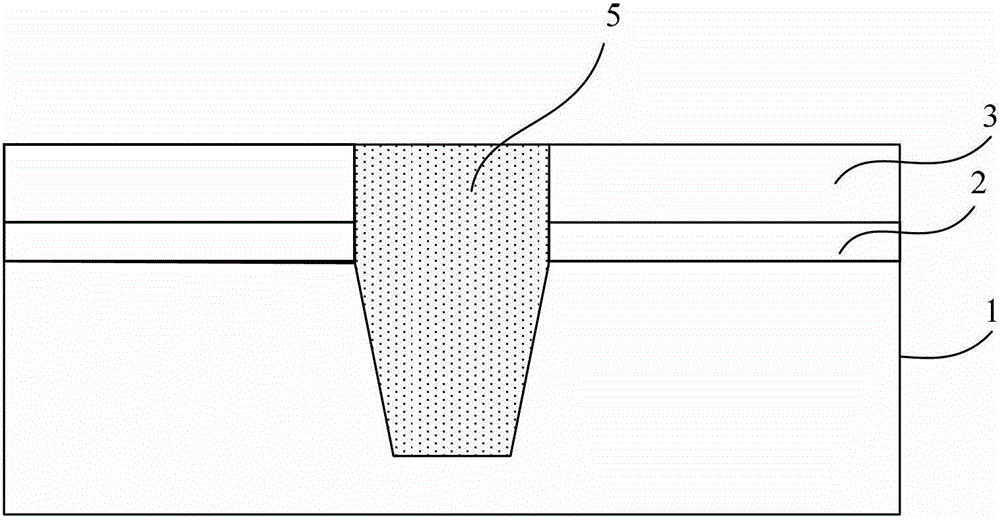

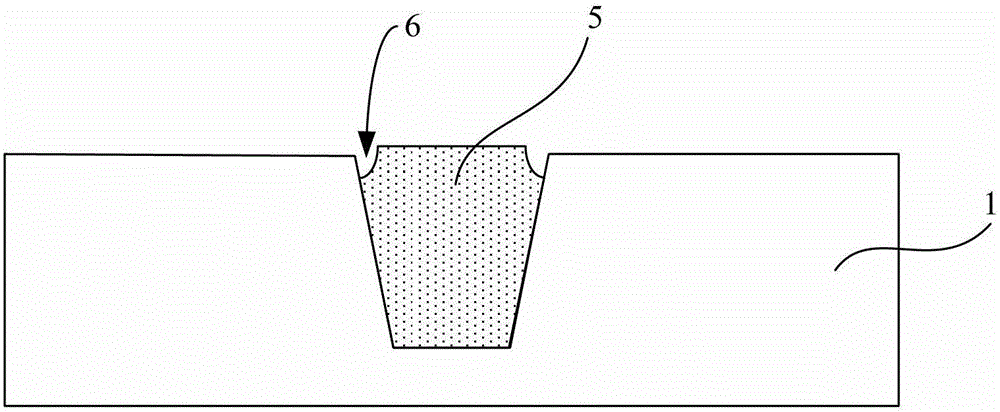

[0033] The principles and features of the present invention are described below in conjunction with the accompanying drawings, and the examples given are only used to explain the present invention, and are not intended to limit the scope of the present invention.

[0034] Aiming at the defects of the prior art, that is, due to the unavoidable depression at the interface between the top of the oxide filled in the shallow trench and the substrate, the formation of the gate oxide layer is affected by the morphology at this point, resulting in a thinner oxide layer. layer, and then induce the narrow channel effect, the starting point of the present invention is to increase the thickness of the oxide layer formed on the surface of the substrate in the depression, and because the region doped with fluorine ions in the substrate has a higher oxide growth rate than the The region not doped with fluorine ions, the present invention is proposed based on the above principle.

[0035] Suc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More