Insulated gate bipolar transistor and preparation method thereof

A technology of bipolar transistors and insulated gates, which is applied in the direction of transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problems of poor robustness and high conduction voltage, so as to improve the robustness, improve the distribution of carriers, reduce the The effect of small parasitic resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

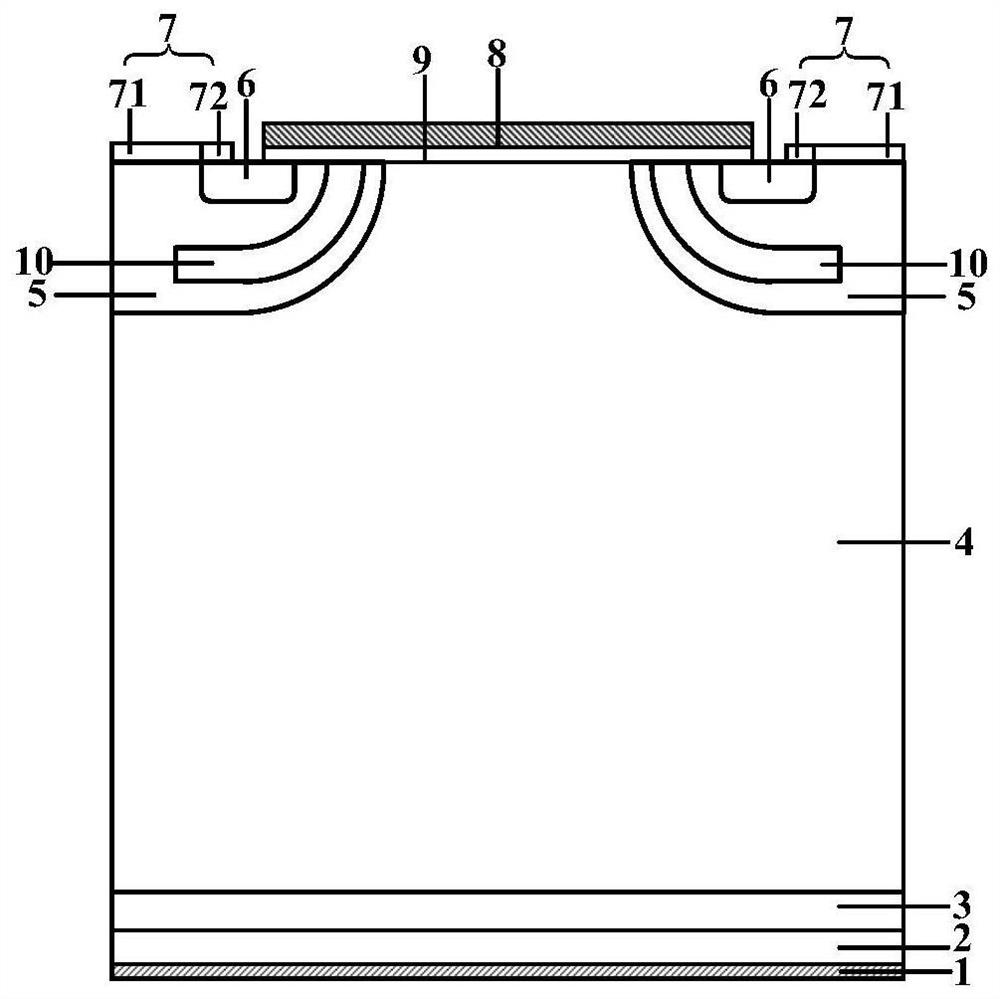

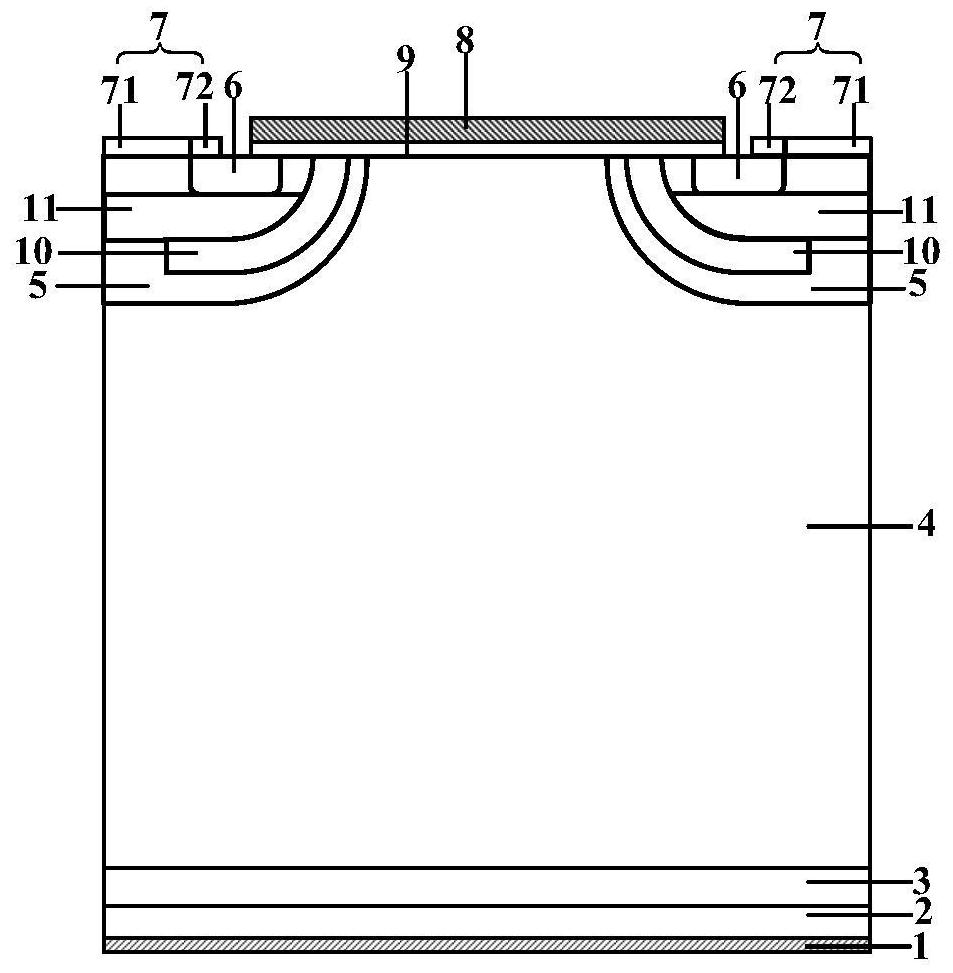

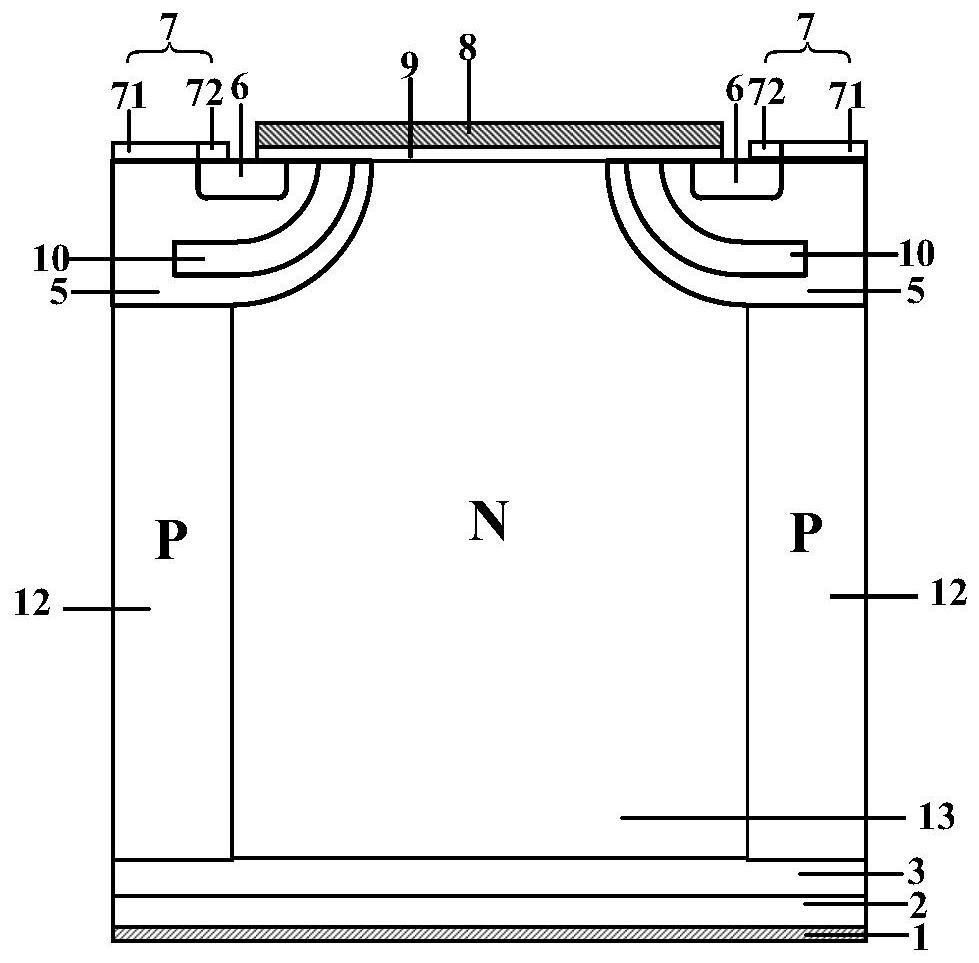

[0061] Embodiment 1 of the present invention provides an insulated gate bipolar transistor, such as figure 1 As shown, it includes N-drift region (4), P-type base region (5), N-buffer layer (10), N+ emission region (6);

[0062] The P-type base region (5) is located on both sides of the upper surface of the N-drift region (4), and the N+ emitter region (6) is located on the upper surface of the P-type base region (5), and is separated from the P-type base region (5). ) has a set distance outside; the N-buffer layer (10) (that is, the N-type charge storage layer) is located inside the P-type base region (5) below the N+ emitter region (6).

[0063] The distance between the outside of the N-buffer layer (10) and the edge of the N-drift region (4) is smaller than the distance between the outside of the N+ emitting region (6) and the edge of the N-drift region (4).

[0064] The middle position on the upper surface of the N-drift region (4) also includes: a grid (8) and a gate die...

Embodiment 2

[0097] Embodiment 2 of the present invention provides a method for preparing an insulated gate bipolar transistor, the specific flow chart is shown in the figure, and the specific process is as follows:

[0098] S101: forming a P-type base region (5) on both sides of the upper surface of the N-drift region (4);

[0099] S102: forming an N-buffer layer (10) inside the P-type base region (5);

[0100] S103: forming an N+ emitter region (6) on the upper surface of the P-type base region (5) above the N-buffer layer (10) and having a set distance from the outside of the P-type base region (5).

[0101] In the above S101, a P-type base region (5) is formed on both sides of the upper surface of the N-drift region (4), including:

[0102] A P-type base region (5) is formed on both sides of the upper surface of the N-drift region (4) by sequentially adopting a thermal oxidation process, a glue coating process, a photolithography process, an ion implantation process and an annealing p...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More