Transistor with local bottom gate and manufacturing method thereof

A manufacturing method and transistor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as unfavorable gate control, poor process repeatability, unstable interface, etc., and achieve good thermal stability and strong process compatibility Sexuality, the effect of good interface characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

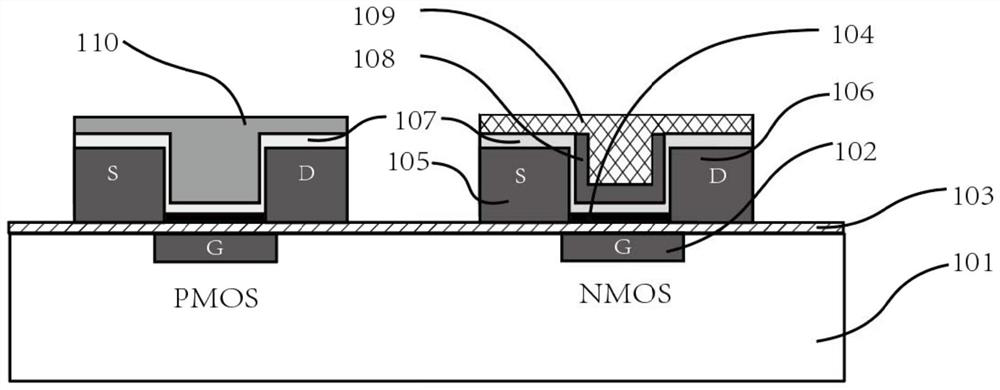

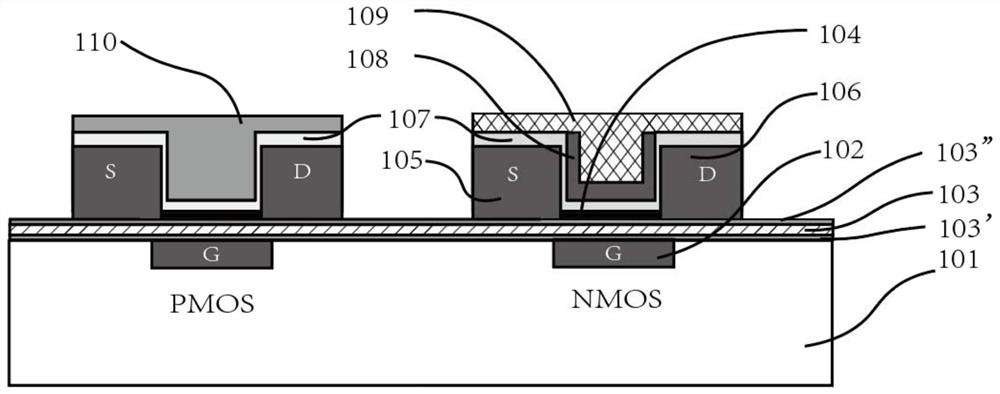

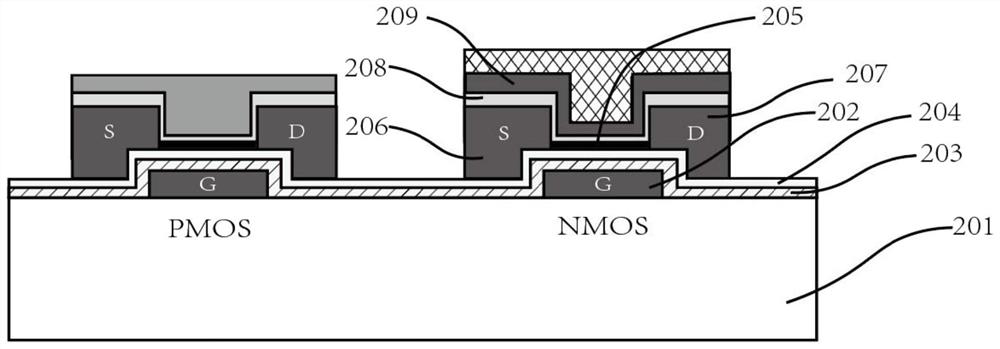

[0071] Embodiments of the present invention will be described in detail below with reference to the accompanying drawings. In the various drawings, the same elements are denoted by the same reference numerals, and various parts in the drawings are not drawn to scale. Also, some well-known parts may not be shown. For the sake of simplicity, the semiconductor structure obtained after several steps can be described in one figure.

[0072] It should be noted that, in the case of no conflict, the embodiments in the present application and the features in the embodiments can be combined with each other. The present invention will be described in detail below with reference to the accompanying drawings and examples.

[0073] The structure of the present embodiment with the localized bottom-gate transistor is as follows figure 1 As shown, the transistor includes a substrate 101 in which a local bottom gate 102 is embedded. In this embodiment, the above-mentioned substrate 101 is a...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More