Ion implantation method capable of preventing silicon edge on boundary of ion implantation region from peeling off

An ion implantation area, ion implantation technology, applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of silicon surface amorphization, silicon peeling, etc., to improve product yield, reduce surface defects, strong The effect of process compatibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

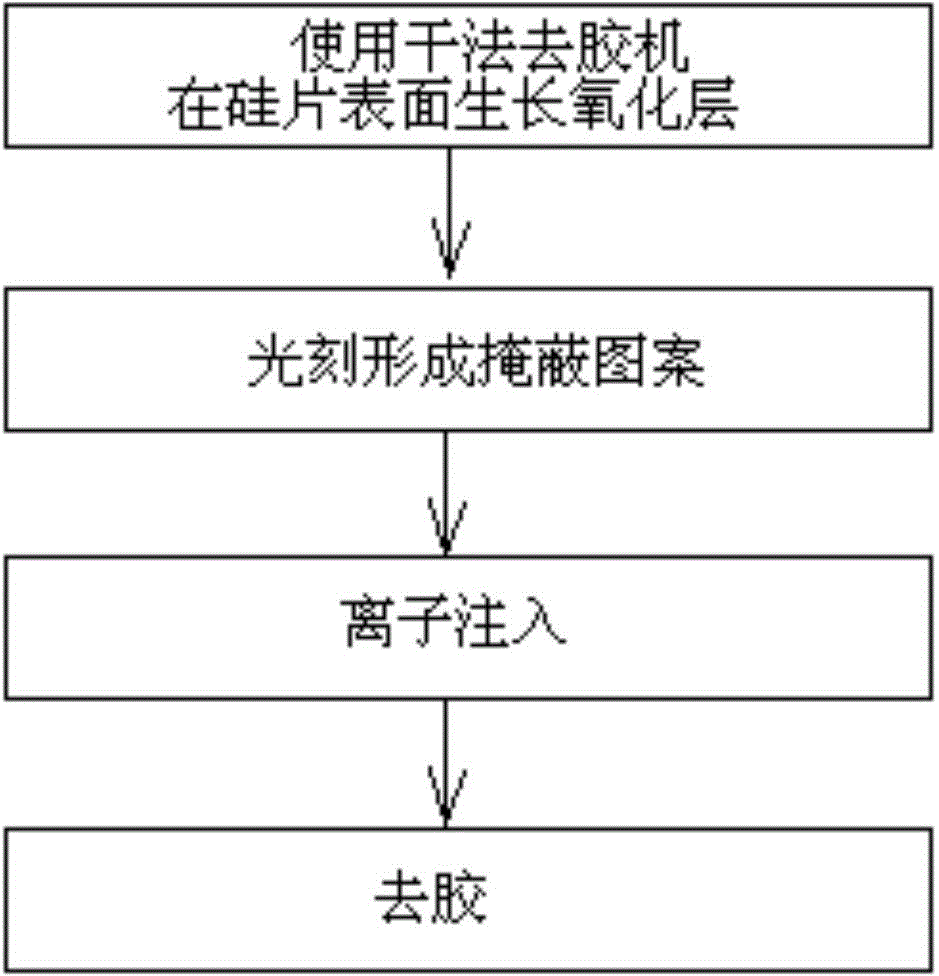

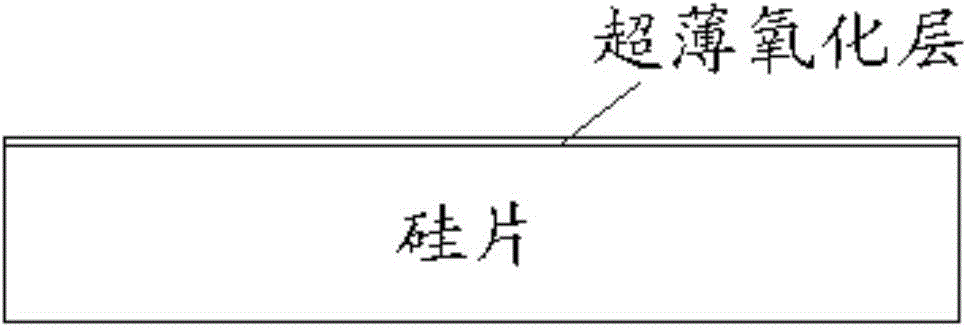

[0042] Step 1: Use a dry degumming machine to treat the surface of the silicon wafer. The specific method is: use a lamp to illuminate the silicon wafer to 180°C, and the illumination time is 20s. During the whole process, O 2 , pass into O 2 The flow rate is 6SLPM, O 2 The air pressure is 4.5Torr, so that the surface growth thickness of the silicon wafer is the oxide layer;

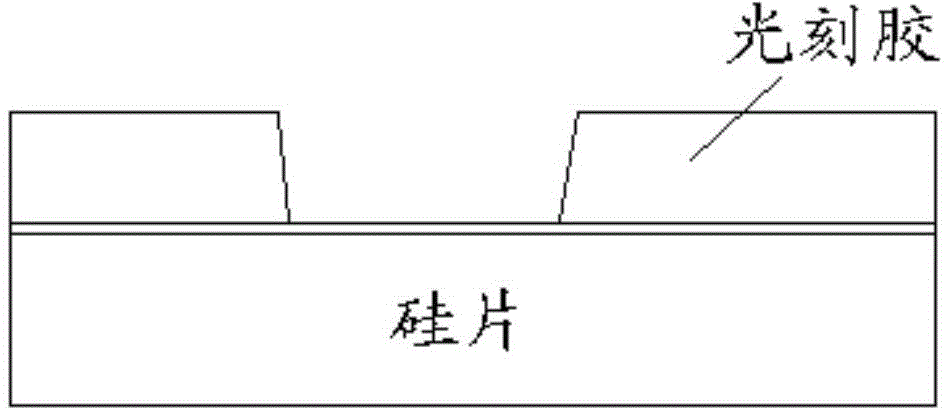

[0043] Step 2: Coating thickness on the silicon wafer treated in step 1 is photoresist;

[0044] Step 3: Perform ion implantation on the silicon wafer treated in step 2, the implantation energy is 80KeV during ion implantation, and the implantation dose of arsenic is 1E15ions / cm 2 ;

[0045] Step 4: firstly remove the photoresist on the surface of the silicon wafer by using the plasma dry method to remove the glue, and then use the wet method to remove the glue.

Embodiment 2

[0047] Step 1: Use a dry degumming machine to treat the surface of the silicon wafer. The specific method is: use a lamp to illuminate the silicon wafer to 220°C, and the illumination time is 40s. During the whole process, O 2 , pass into O 2 The flow rate is 4SLPM, O 2 The air pressure is 3.5Torr, so that the surface growth thickness of the silicon wafer is the oxide layer;

[0048] Step 2: Coating thickness on the silicon wafer treated in step 1 is photoresist;

[0049] Step 3: Perform ion implantation on the silicon wafer treated in step 2, the implantation energy is 160KeV during ion implantation, and the implantation dose of phosphorus is 4E15ions / cm 2 ;

[0050] Step 4: Removing the photoresist on the surface of the silicon wafer by means of dry stripping and wet stripping.

Embodiment 3

[0052] Step 1: Use a dry degumming machine to treat the surface of the silicon wafer. The specific method is: use a lamp to illuminate the silicon wafer to 200°C, and the illumination time is 30s. During the whole process, O 2 , pass into O 2 The flow rate is 5SLPM, O 2 The air pressure is 4Torr, so that the surface growth thickness of the silicon wafer is the oxide layer;

[0053] Step 2: Coating thickness on the silicon wafer treated in step 1 is photoresist;

[0054] Step 3: Perform ion implantation on the silicon wafer treated in step 2, the implantation energy is 120KeV during ion implantation, implant arsenic and the implantation dose is 6E15ions / cm 2 ;

[0055] Step 4: Removing the photoresist on the surface of the silicon wafer by means of dry stripping and wet stripping.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More