Method for manufacturing high-voltage VDMOS by adopting silicon-silicon bonding process

A silicon-silicon bond and bonding technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of long preparation process time, low production efficiency, and wide transition zone, so as to reduce production costs and improve production Efficiency, effect of narrow transition zone

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

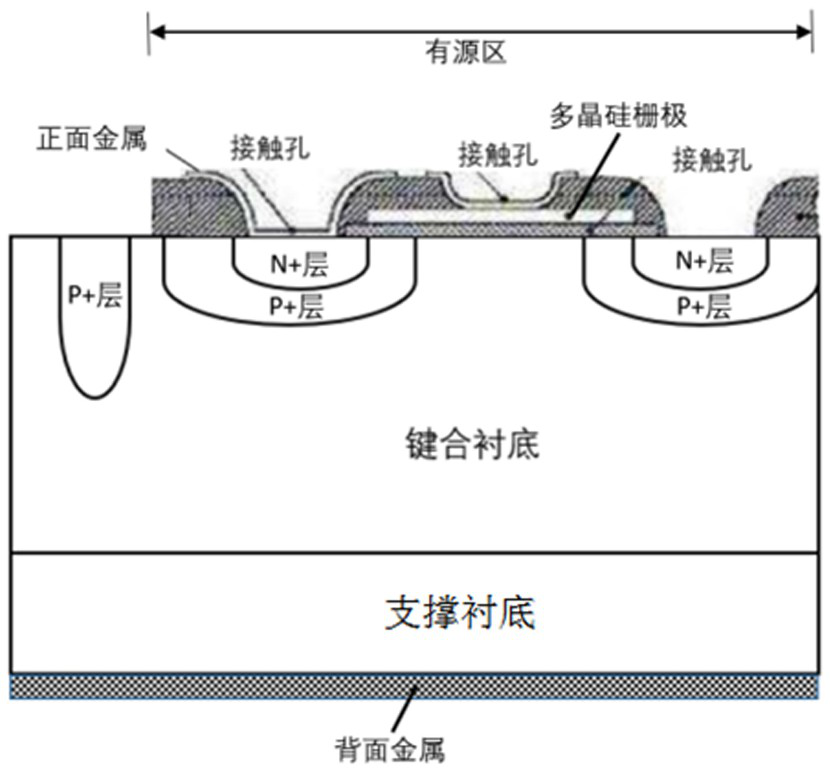

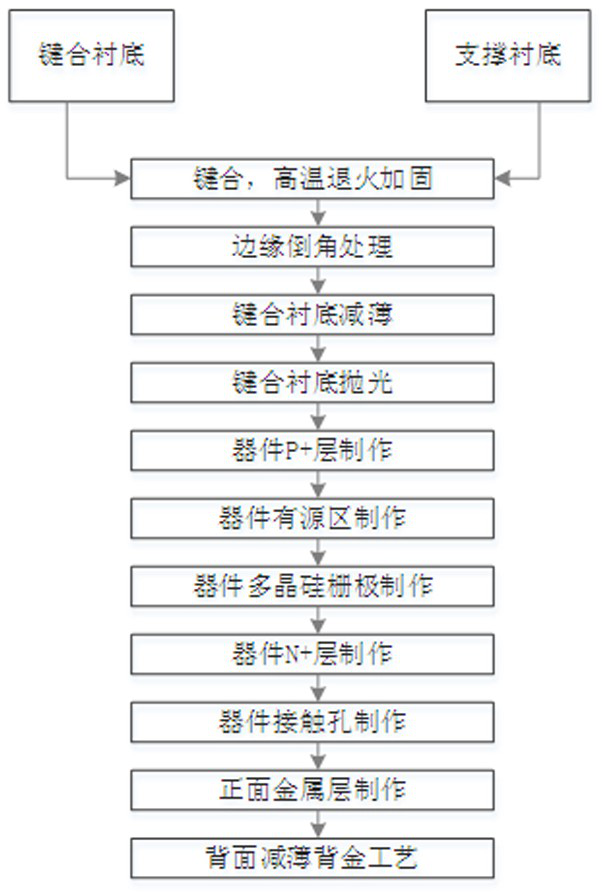

[0021] Hereinafter, exemplary embodiments of the present application will be described in detail with reference to the accompanying drawings. Apparently, the described embodiments are only some of the embodiments of the present application, rather than all the embodiments of the present application. It should be understood that the present application is not limited by the exemplary embodiments described here.

[0022] Application overview

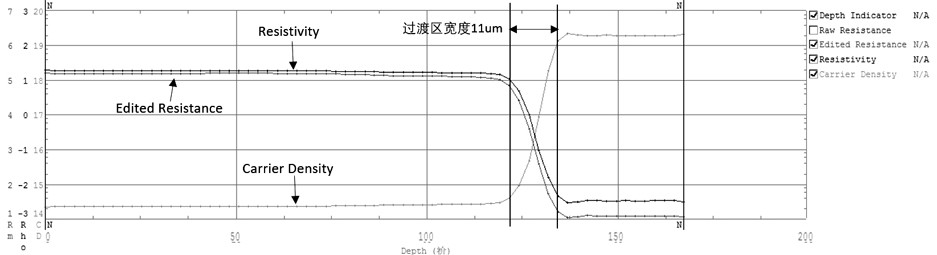

[0023] The process flow of conventional high-voltage VDMOS products is as follows: Prepare the substrate—grow epitaxy on the substrate. The thickness of the epitaxy is usually 50~250um according to the voltage requirement. For high-voltage and high-voltage VDMOS products, the thickness and resistivity of the epitaxy are directly related to the withstand voltage. This also leads to long preparation process time when the epitaxial thickness reaches 100um, and the single furnace process time exceeds 2.5 hours, the production efficiency is low...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More