Semiconductor forming method and structure thereof

A semiconductor and graphics technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problems of low utilization efficiency of a single wafer, small number of effective chips, etc., to improve area utilization , Improve the effect of alignment accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

[0031] Figure 1 to Figure 5 is a schematic diagram of an alignment mark forming method provided by an embodiment of the present invention.

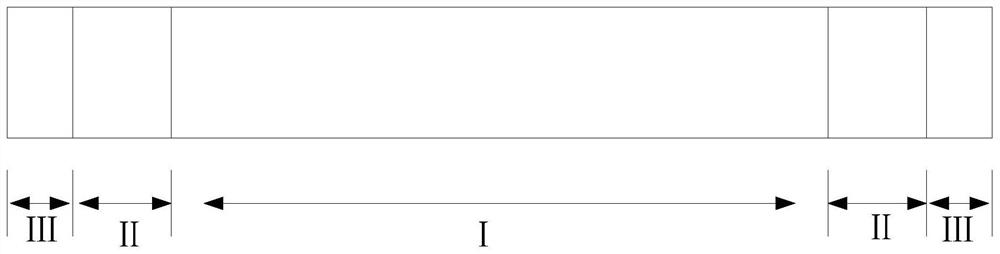

[0032] refer to figure 1 , provide a chip, the chip includes a chip device area I, a dummy device area II on the periphery of the chip device area I, the periphery of the dummy device area II also includes a sealing device area III, and a dicing line ( not shown).

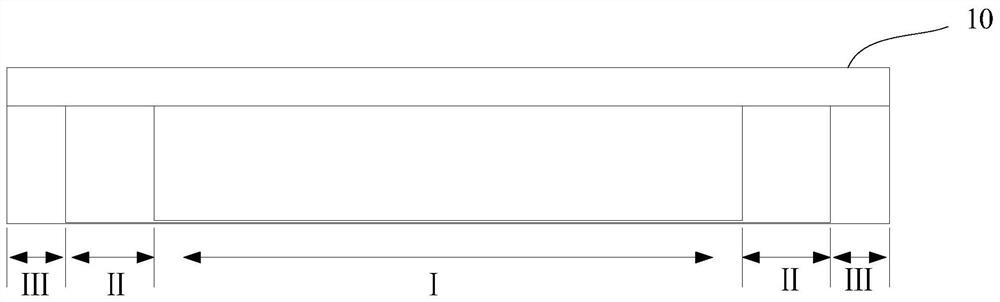

[0033] refer to figure 2 , forming a photoresist layer 10 on the surface of the dummy device region II. Specifically, the method for forming the photoresist layer 10 is a dynamic spray coating method, which first rotates at a low speed so that the photoresist is uniformly diffused, and then rotates at a high speed to form a uniform photoresist in the dummy device region II. Resist layer 10.

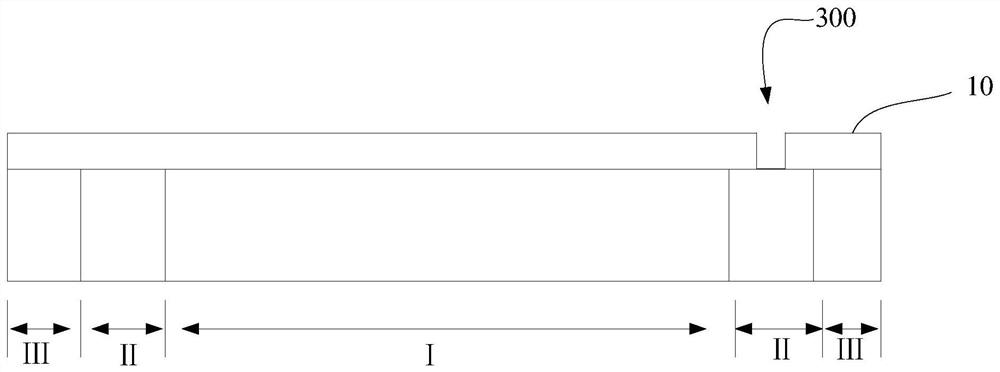

[0034] refer to image 3 , transferring the pattern with the alignment mark 300 of the present invention onto the photoresist layer 10 . The specific steps include: placing a mas...

no. 2 example

[0054] Figure 8 It is a schematic diagram of the pattern of the alignment mark provided by another embodiment of the present invention.

[0055] refer to Figure 8 , in this embodiment, the alignment mark 300 is Figure 6 The structure of the alignment mark in is effectively split, and can be formed in the dummy device region II without affecting the function of the alignment mark 300 . Specifically, the alignment mark 300 includes a first alignment mark aligned in a first direction x and a second alignment mark aligned in a second direction y, and the first alignment mark is aligned with the second alignment mark. The quasi-identification is separated. The purpose of splitting the alignment mark 300 is to ensure that the alignment mark 300 is completely formed in the dummy device region II due to the limited area size of the dummy device region II.

[0056] In this embodiment, the first alignment mark includes the grating group A and the grating group D. It can be seen t...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Spacing | aaaaa | aaaaa |

| Length | aaaaa | aaaaa |

| Width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More