Method and device for reducing high-temperature off-state electric leakage of semiconductor device

A device and high-temperature technology, applied in the field of reducing high-temperature off-state leakage of semiconductor devices, can solve the problems of complex process flow and high cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

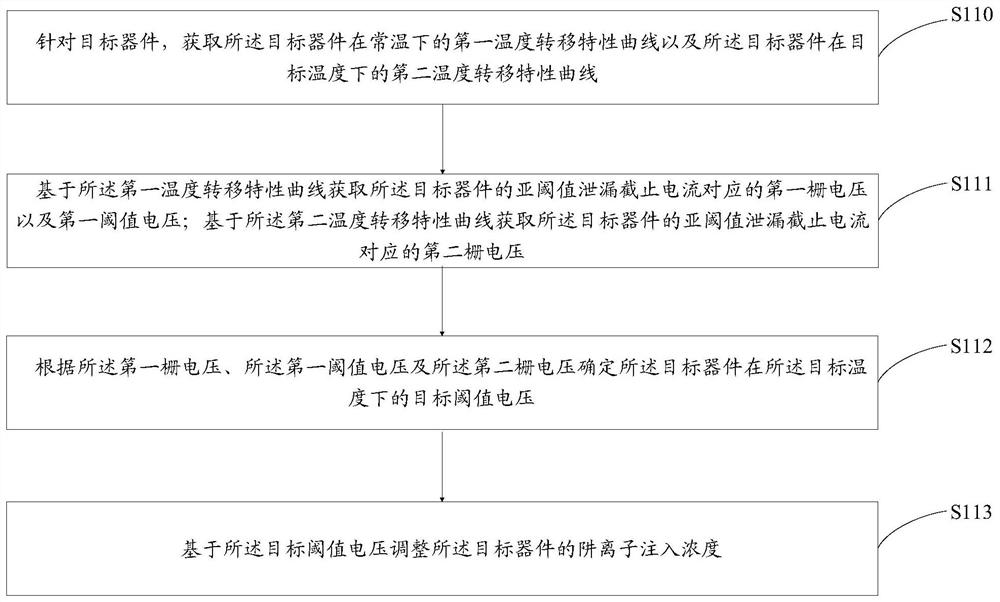

[0050] This embodiment provides a method for reducing high-temperature off-state leakage of semiconductor devices. When the temperature is greater than 125 degrees, it is called high temperature, such as figure 1 As shown, the methods include:

[0051] S110, for the target device, acquire a first temperature transfer characteristic curve of the target device at room temperature and a second temperature transfer characteristic curve of the target device at a target temperature;

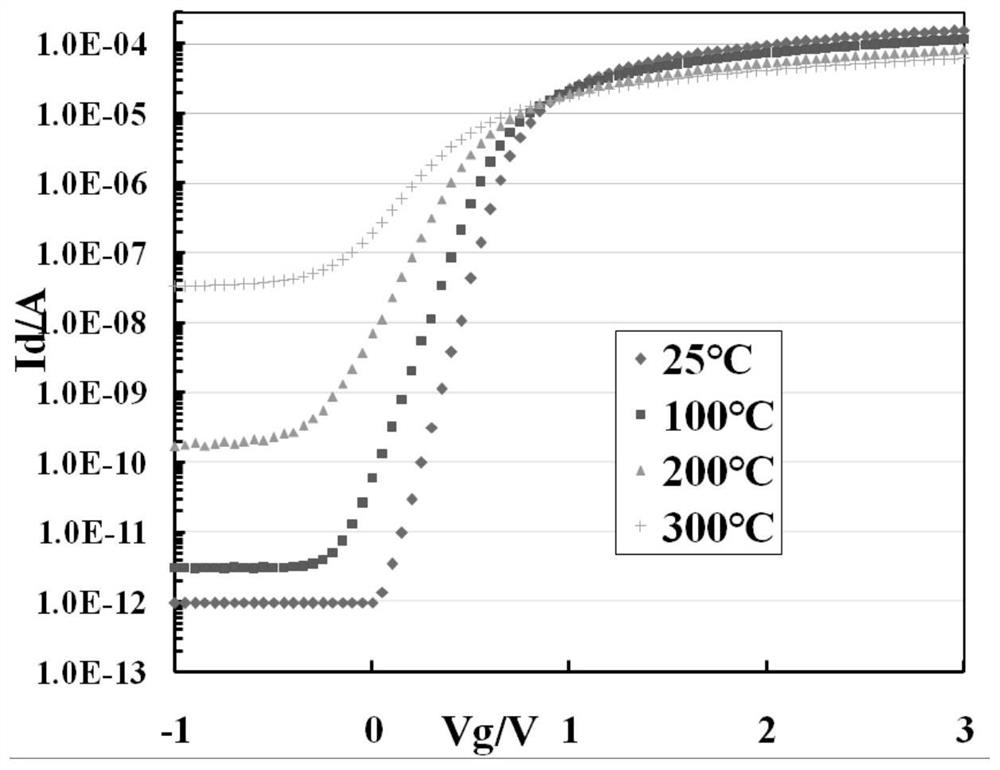

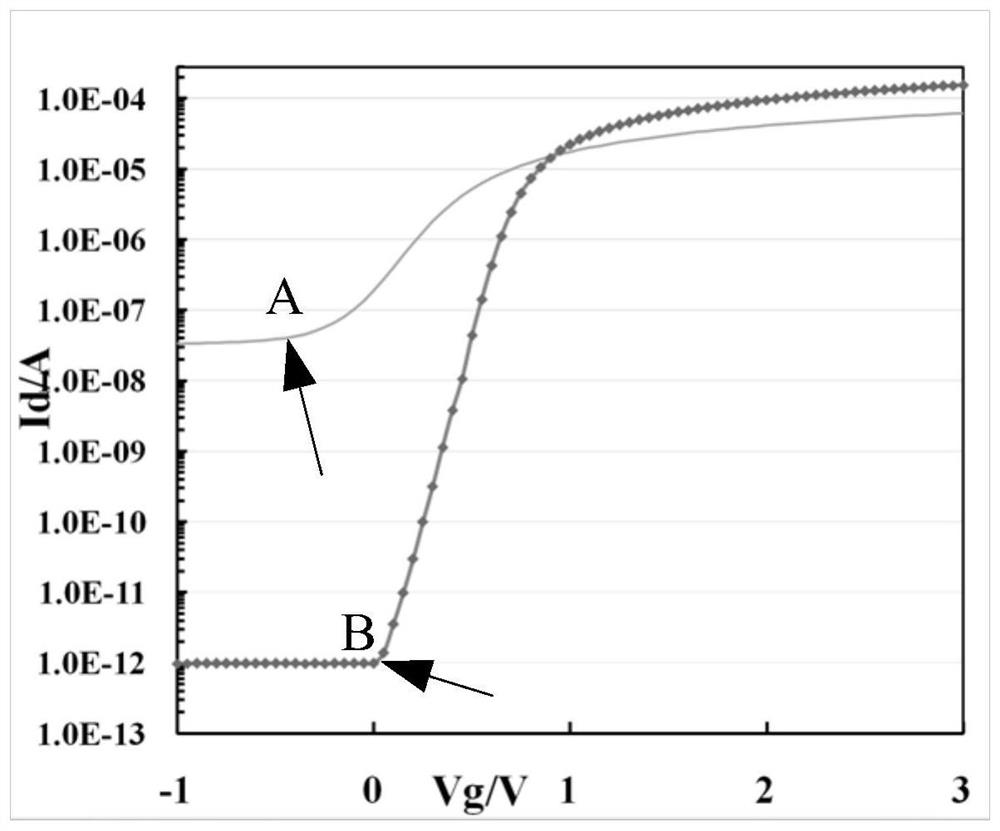

[0052] For either device, refer to figure 2 , can test the temperature transfer characteristic curve of the device at different temperatures (respectively 25°C, 100°C, 200°C and 300°C), and determine the threshold voltage (Vth) and off-state leakage of the target device from the temperature transfer characteristic curve , drive current and sub-threshold leakage cut-off current Idb and other electrical parameters. here, figure 2 It is the temperature transfer characteristic curve of NMOS device at ...

Embodiment 2

[0083] This embodiment provides a device for reducing the high-temperature off-state leakage of semiconductor devices, such as Figure 5 As shown, the device includes: an acquisition unit 51, a determination unit 52, and an adjustment unit 53; wherein,

[0084] The acquiring unit 51 is configured to acquire, for the target device, a first temperature transfer characteristic curve of the target device at normal temperature and a second temperature transfer characteristic curve of the target device at a target temperature; based on the first temperature transfer characteristic Obtaining the first gate voltage and the first threshold voltage corresponding to the subthreshold leakage cut-off current of the target device according to the curve; obtaining the second gate voltage corresponding to the subthreshold leakage cut-off current of the target device based on the second temperature transfer characteristic curve ;

[0085] A determining unit 52, configured to determine a targe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More