DDR control system and DDR storage system

A control system and memory technology, applied to instruments, electrical digital data processing, etc., to achieve the effects of reducing design and application complexity, dynamically configurable data, and improving scalability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032]The technical solution proposed by the present invention will be further described in detail below with reference to the drawings and specific embodiments. According to the following description, the advantages and features of the present invention will be clearer. It should be noted that the drawings are in a very simplified form and all use imprecise proportions, which are only used to conveniently and clearly assist in explaining the purpose of the embodiments of the present invention.

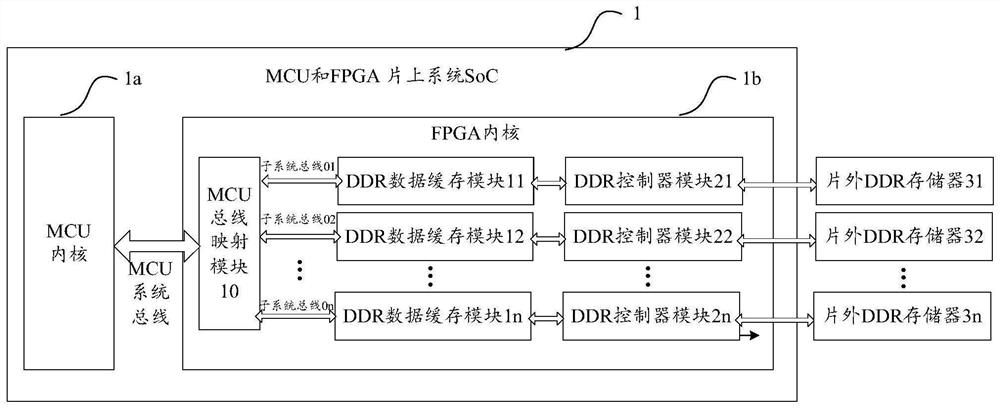

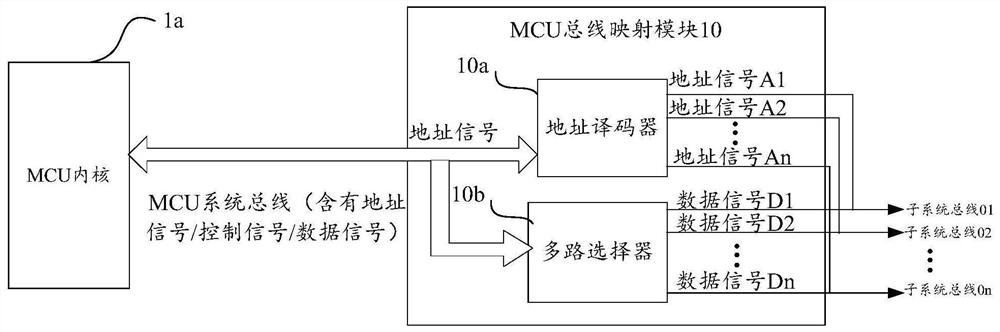

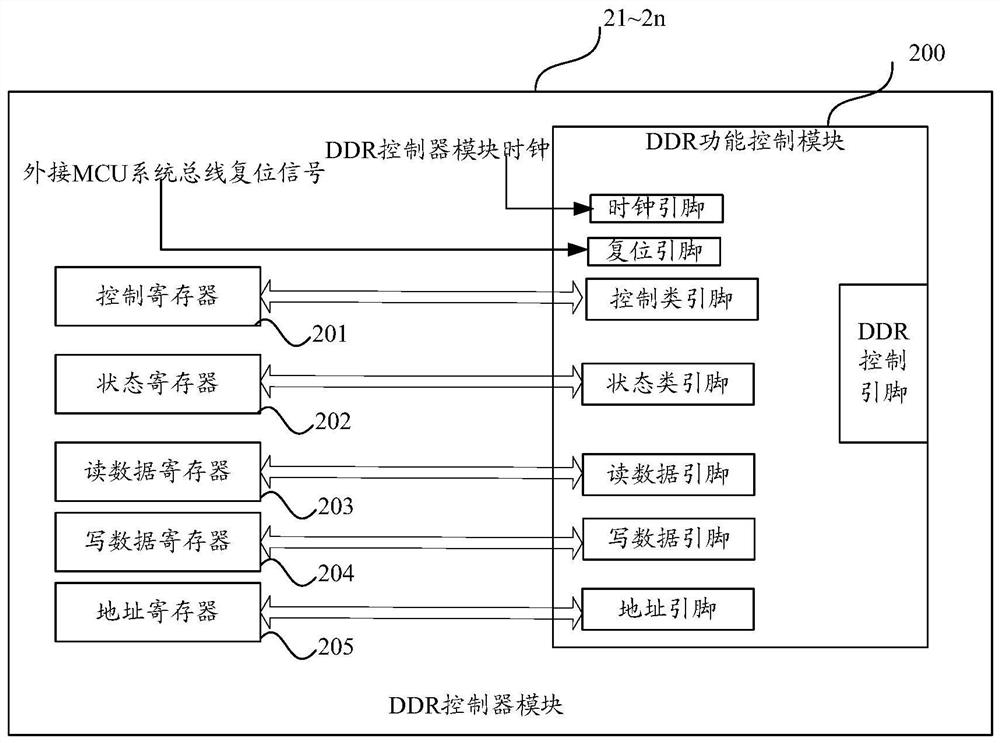

[0033]Please refer tofigure 1 An embodiment of the present invention provides a DDR control system. The DDR control system is an on-chip DDR control system based on MCU and FPGA SoC architecture 1. It includes an MCU core 1a and an FPGA core integrated in the same system-on-chip Soc. 1b. The logic resources inside the FPGA core 1b mainly include logic control block (Logical Control Block, LCB) resources, clock network resources, clock processing resources, block random access memory (Block RAM...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More