TFT array substrate structure and manufacturing method

A fabrication method and array substrate technology, which are applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve the problems affecting the driving current of IGZOTFT, the increase of Schottky contact resistance, and the reduction of carrier mobility, etc. problem, to achieve the effect of saving cost output, reducing electrical drift of the device, and fine grain

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

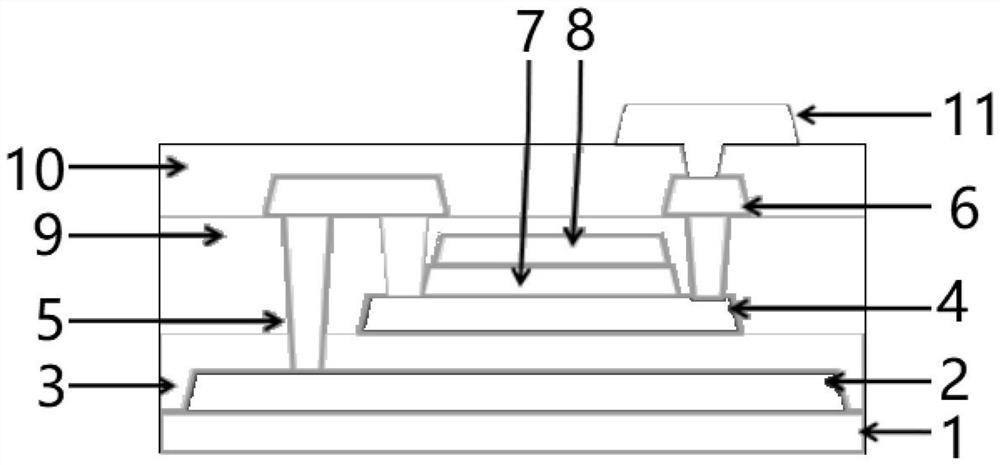

[0036] In order to explain in detail the technical content, structural features, achieved goals and effects of the technical solution, the following will be described in detail in conjunction with specific embodiments and accompanying drawings.

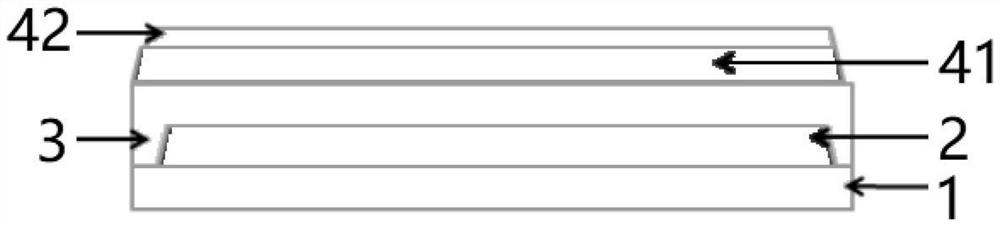

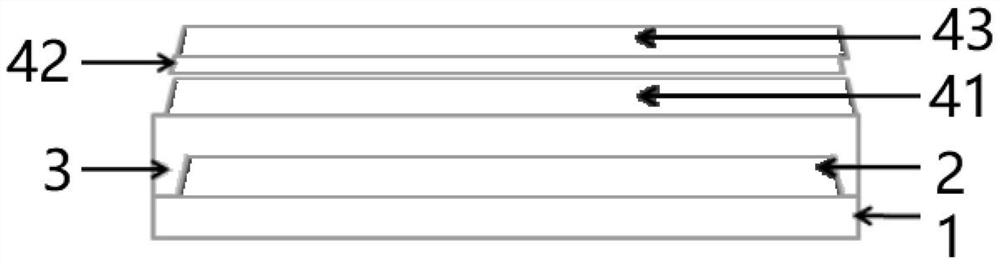

[0037] see Figure 1 to Figure 5, the present embodiment provides a method for manufacturing a TFT array substrate, comprising the steps of: depositing a light-shielding layer 2 on the substrate 1, and fabricating a buffer layer 3 on the light-shielding layer 2; fabricating a first buffer layer 3 on the buffer layer 3 active layer 41, and make a second active layer 42 on the first active layer 41; pattern the first active layer 41 and the second active layer 42 to form an active layer film 4; The active layer film 4 includes: a first active layer 41 and a second active layer 42; a gate insulating layer 7 is formed on the first active layer 41, and a gate insulating layer 7 is formed on the gate insulating layer 7 metal gate layer 8; ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More