Multi-channel DAC sampling synchronization system

A sampling synchronization, multi-channel technology, applied in the direction of digital-to-analog converters, etc., can solve the problem that the DAC cannot meet the high sampling and synchronous multi-source output, etc., to achieve the effect of high controlled synchronization ability, avoid synchronization errors, and simple hardware structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

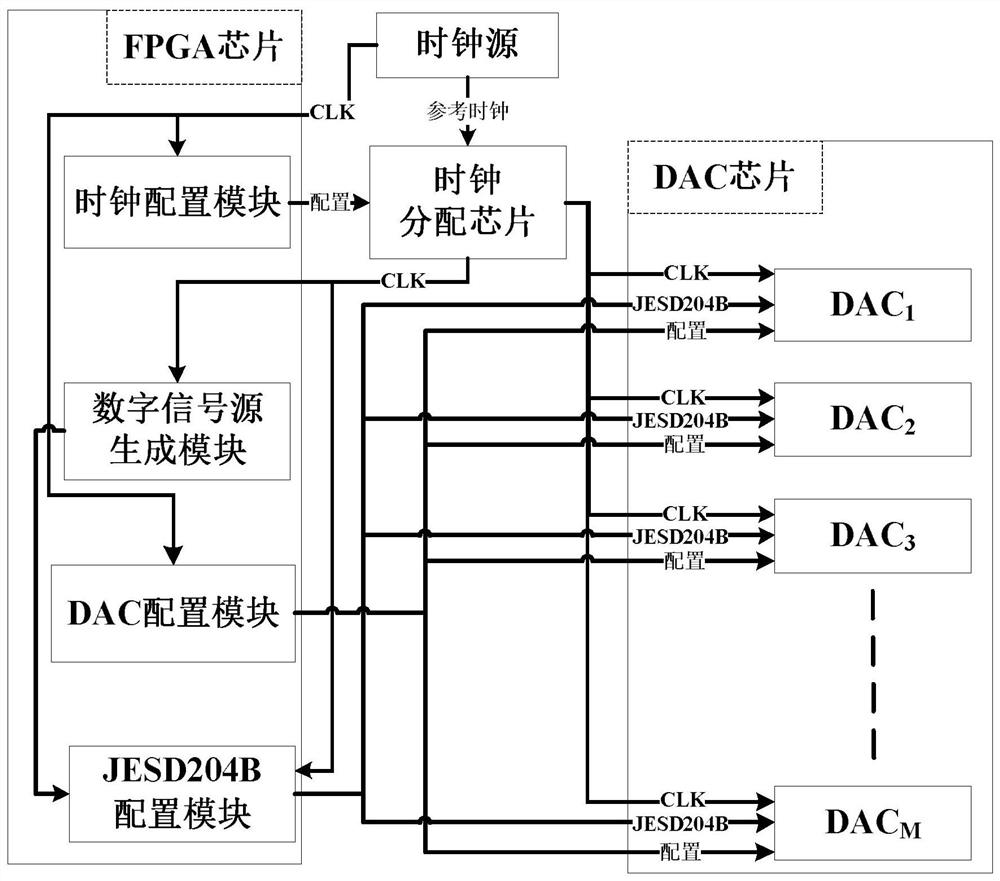

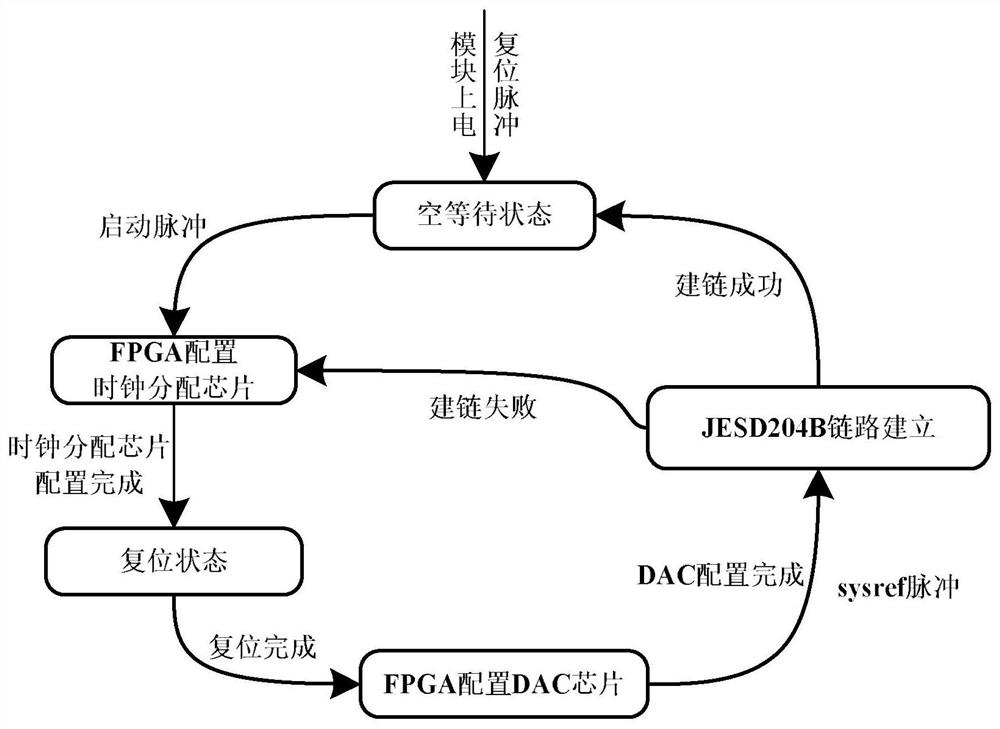

[0015] refer to figure 1 . In the preferred embodiment described below, a multi-channel DAC sampling synchronization system includes: a large-scale programmable gate array FPGA connected to an external clock source and a clock distribution chip, and the FPGA chip is connected in parallel to a multi-channel high-speed digital-to-analog converter DAC. The FPGA chip built-in program software integrates a clock configuration module, a digital signal source generation module, a DAC configuration module and a JESD204B configuration module; the external clock source inputs the clock source data flow into the clock configuration module, the DAC configuration module and the clock distribution chip respectively , provide the logic clock for the clock configuration module and the DAC configuration module respectively, and provide the reference clock for the clock distribution chip; the clock configuration module completes the specific parameter configuration for the multi-channel clock ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More