Compiling method for reducing multi-class memory access conflicts for coarse-grained reconfigurable structure

A memory access and compiler technology, which is applied in the field of coarse-grained reconfigurable structure compilers, can solve the problems of not considering the impact of memory access conflict performance, increasing the time cost of on-chip memory, and increasing the complexity of data storage in on-chip memory.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0071] The following describes the preferred embodiments of the present application with reference to the accompanying drawings to make the technical content clearer and easier to understand. The present application can be embodied in many different forms of embodiments, and the protection scope of the present application is not limited to the embodiments mentioned herein.

[0072] The idea, specific structure and technical effects of the present invention will be further described below to fully understand the purpose, features and effects of the present invention, but the protection of the present invention is not limited thereto.

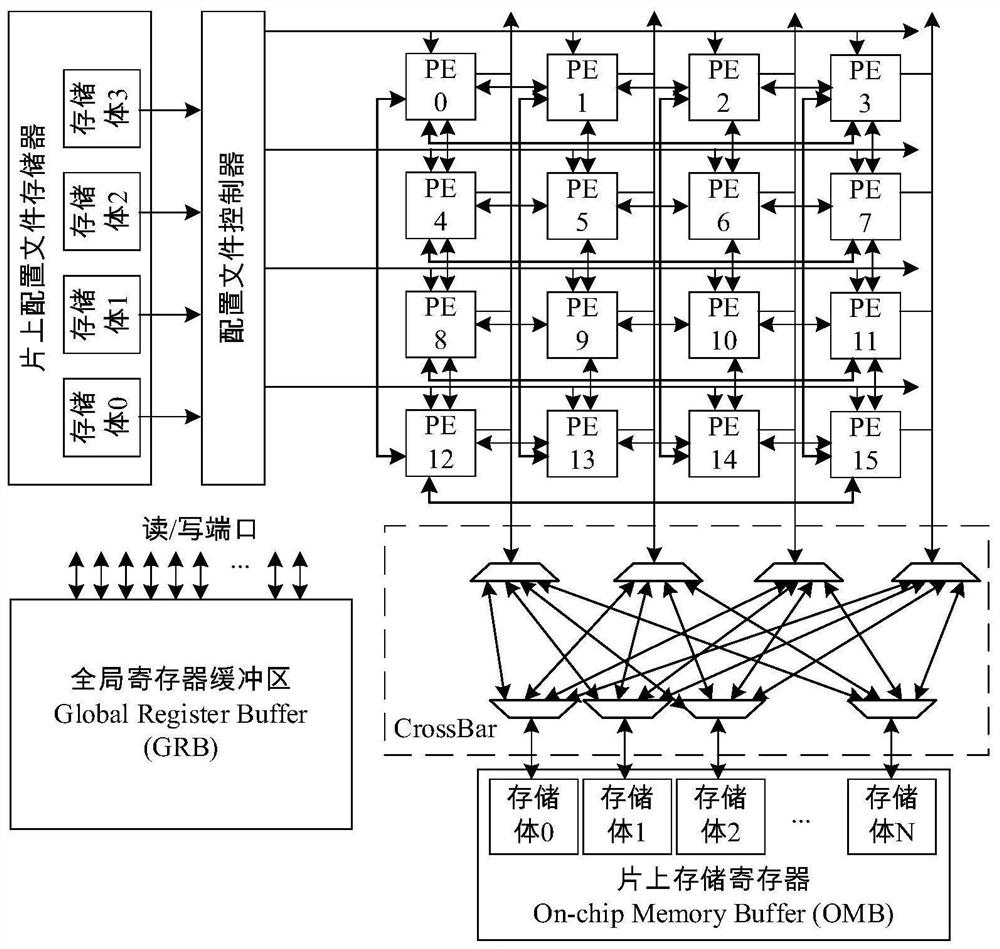

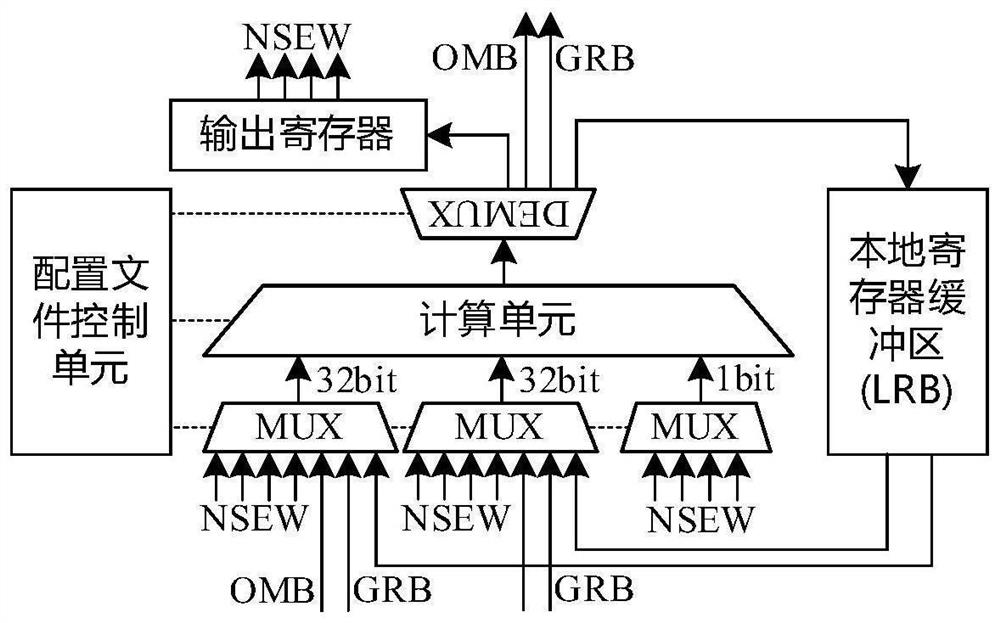

[0073] The hardware structure that the present invention is based on

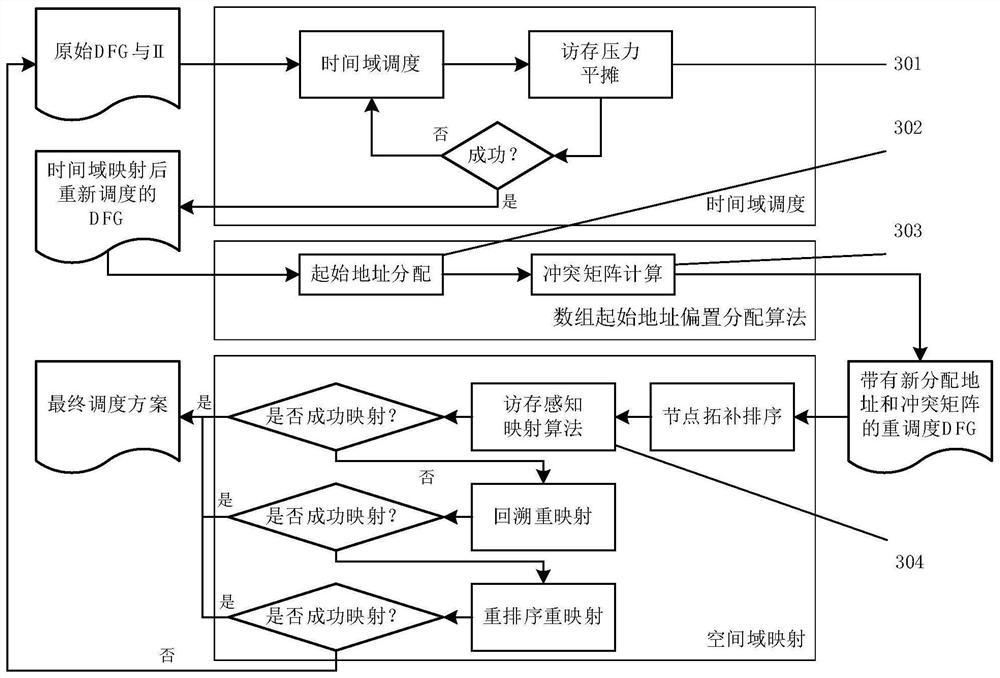

[0074] The invention aims to optimize the scheduling and mapping process of the reconfigurable processor compiler, comprehensively consider the multi-storage conflicts and interconnection conflicts between memory access operators, and propose a method to reduce the memory acce...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More