A compilation method for reducing multi-class memory access conflicts for coarse-grained reconfigurable structures

A memory access and compiler technology, applied in the field of coarse-grained reconfigurable structure compilers, can solve problems such as performance degradation, failure to consider interconnection conflicts, and performance impact of memory access conflicts, etc., to achieve high application speed-up ratio and flow The effect of simple structure and reduced time cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0071] The preferred embodiments of the present application will be described below with reference to the accompanying drawings, so as to make its technical content clearer and easier to understand. The present application can be embodied in many different forms of embodiments, and the protection scope of the present application is not limited to the embodiments mentioned herein.

[0072] The concept, specific structure and technical effects of the present invention will be further described below to fully understand the purpose, features and effects of the present invention, but the protection of the present invention is not limited to this.

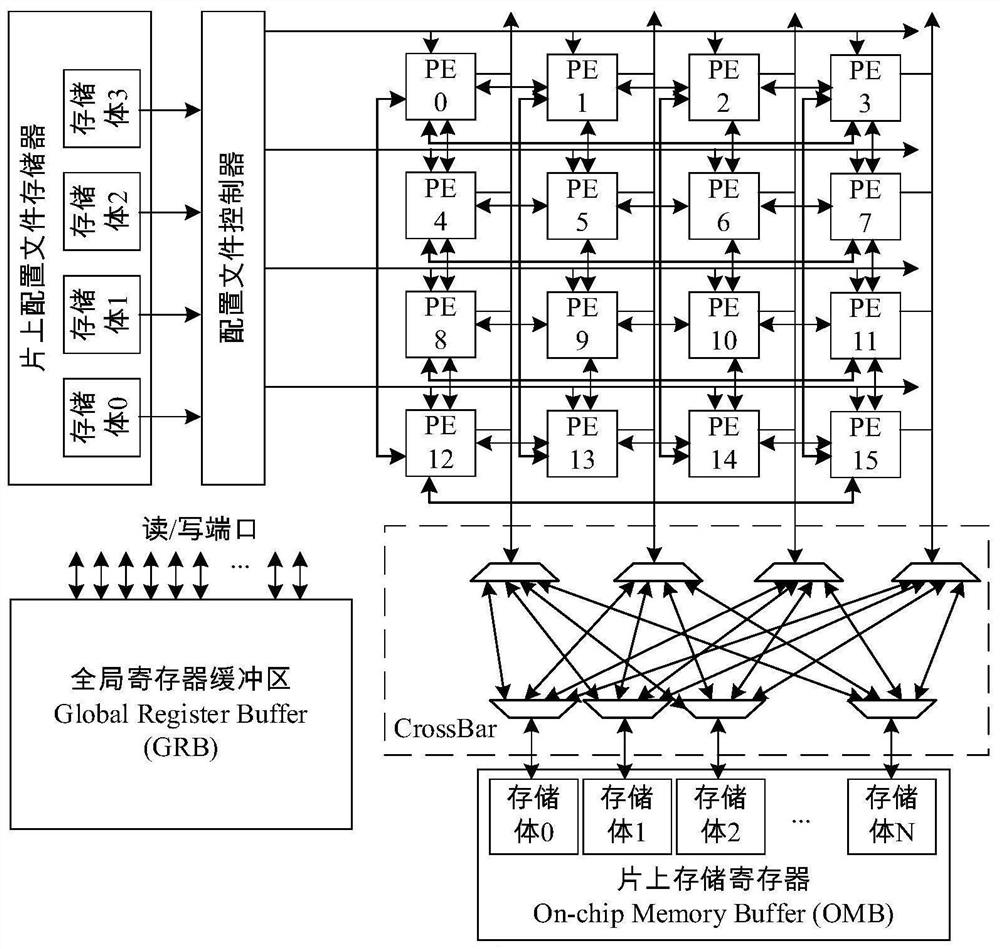

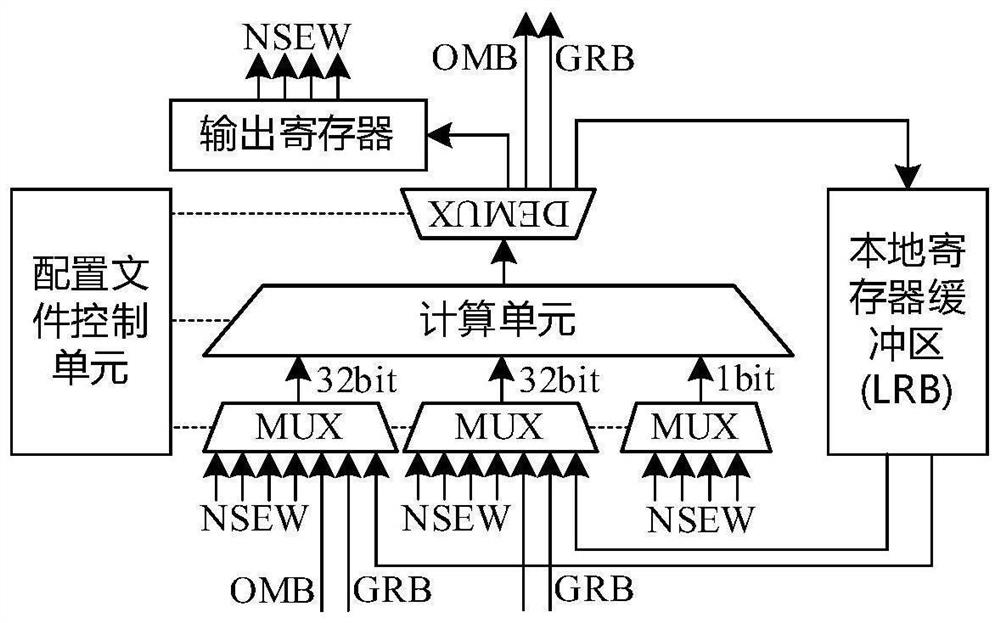

[0073] The hardware structure on which the invention is based

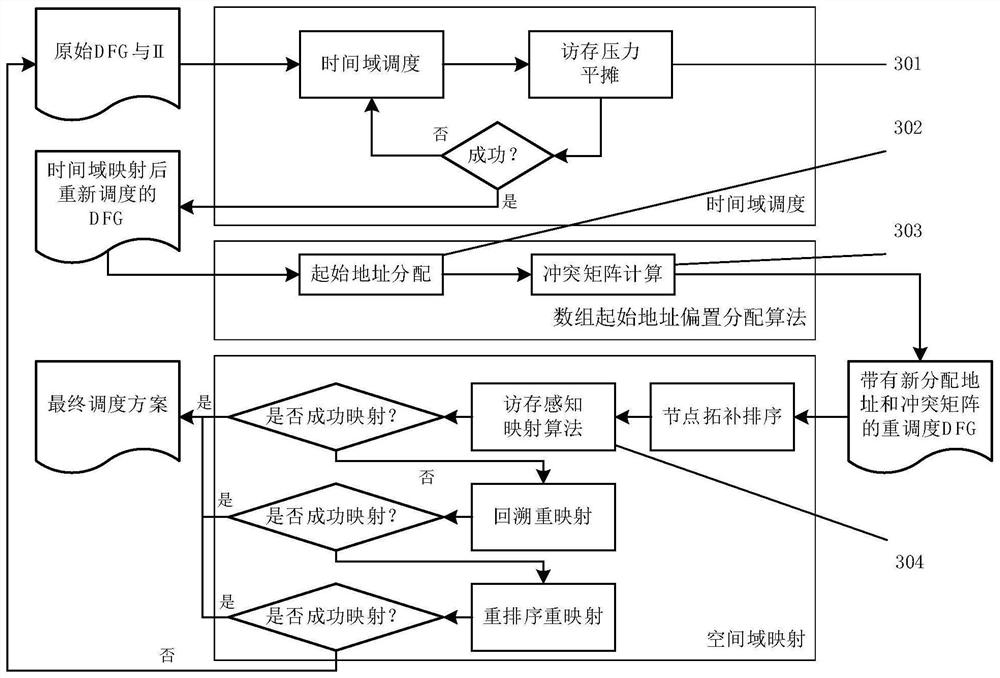

[0074] The invention aims to optimize the scheduling and mapping process of the reconfigurable processor compiler, comprehensively considers the multi-memory bank conflict and the interconnection conflict between the memory access operators, and proposes a method to reduce ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More