Three-dimensional memory and forming method of three-dimensional memory

A memory, three-dimensional technology, applied in electric solid state devices, semiconductor devices, semiconductor/solid state device components, etc., can solve problems such as memory cell programming interference, and achieve better heat insulation effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

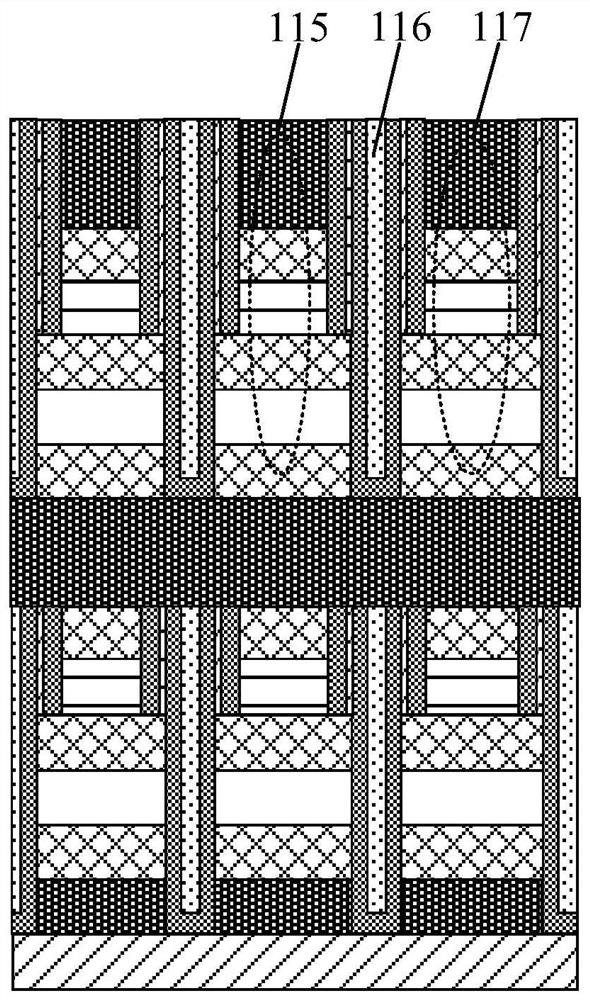

[0090] figure 2 A schematic diagram of an optional structure of the three-dimensional memory provided by the embodiment of the present application, such as figure 2 As shown, the three-dimensional memory 20 includes:

[0091] A plurality of first conductive lines 201 extend along a first direction.

[0092] Here, the first direction is the X-axis direction, and the material of the first conductive line 201 includes but not limited to tungsten (W), cobalt (Co), copper (Cu), aluminum (Al), polysilicon, doped silicon , silicide, or any combination thereof.

[0093] A plurality of second conductive lines 202 extend along a second direction, and the first direction and the second direction are perpendicular to each other.

[0094] In the embodiment of the present application, the second direction is the Y-axis direction, and the material of the second conductive line 202 includes but not limited to tungsten (W), cobalt (Co), copper (Cu), aluminum (Al), polysilicon , doped sil...

Embodiment 2

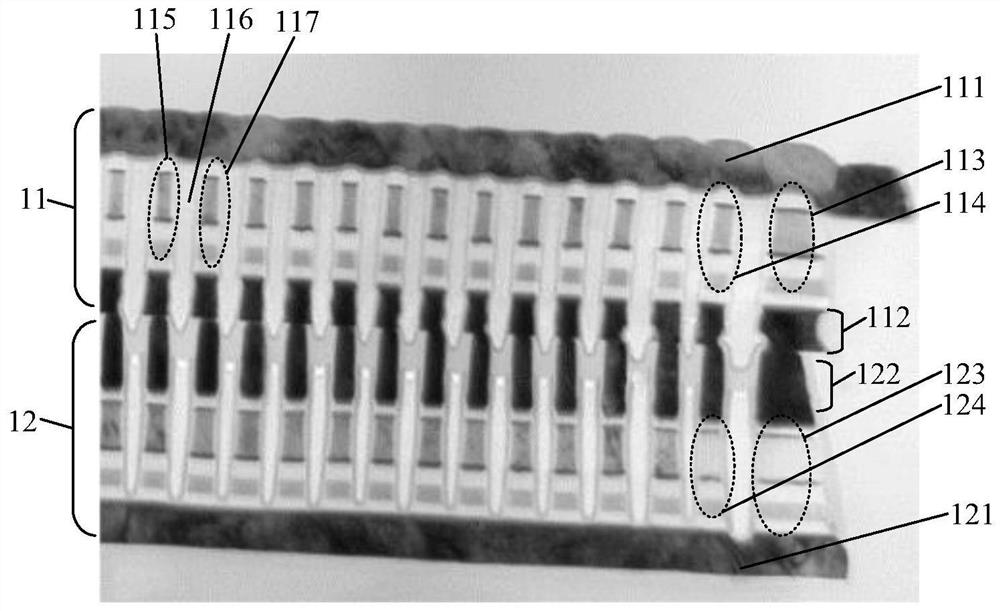

[0099] Figure 3A An optional structural schematic diagram of the three-dimensional memory provided by the embodiment of the present application, such as Figure 3A As shown, the three-dimensional memory 30 includes:

[0100] A plurality of first conductive lines 301 extend along a first direction.

[0101] A plurality of second conductive lines 302 extend along a second direction, and the first direction and the second direction are perpendicular to each other.

[0102] In the embodiment of the present application, the first direction is the X-axis direction, the second direction is the Y-axis direction, and the materials of the first conductive wire 301 and the second conductive wire 302 include but are not limited to tungsten (W ), cobalt (Co), copper (Cu), aluminum (Al), polysilicon, doped silicon, silicide, or any combination thereof.

[0103] In some embodiments, the three-dimensional memory 30 further includes: arranged between the first conductive line 301 and the s...

Embodiment 3

[0124] Figure 4A A schematic diagram of the implementation flow of the method for forming a three-dimensional memory provided in the embodiment of the present application, as shown in Figure 4A As shown, the method includes the following steps:

[0125] Step S401, forming a semiconductor stack structure.

[0126] The semiconductor stack structure 41 is a stack structure with a certain number of layers. In the embodiment of the present application, the semiconductor stack structure 41 can be formed by chemical vapor deposition (Chemical Vapor Deposition, CVD) or physical vapor deposition (Physical Vapor Deposition, PVD) Or atomic layer deposition (Atomic Layer Deposition, ALD) and other methods are formed on the surface of the substrate (not shown in the figure). Figure 4B A schematic cross-sectional structure diagram of a semiconductor stack structure provided in an embodiment of the present application, Figure 4B A schematic cross-sectional view of the semiconductor st...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thermal conductivity | aaaaa | aaaaa |

| Thermal stability | aaaaa | aaaaa |

| Surface area | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More