Decoupling capacitor placement method applied to system-in-package

A technology of system-level packaging and decoupling capacitors, which is applied in the direction of circuits, electrical components, and electrical solid-state devices, and can solve problems such as occupying space

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

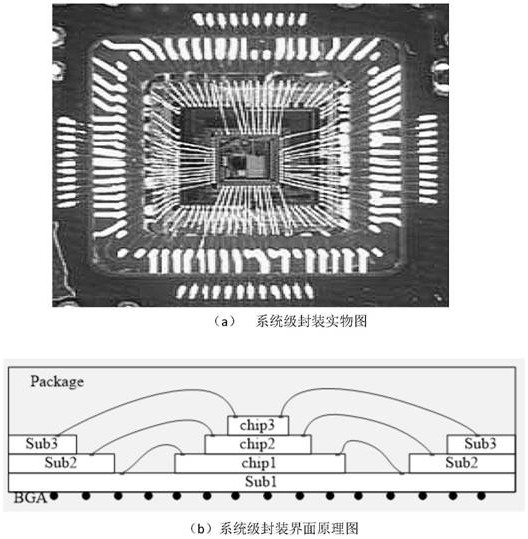

[0016] A decoupling capacitor placement method applied to system-in-package, specifically:

[0017] Step 1, according to the overall routing requirements, preset the substrates Sub1 and Sub2;

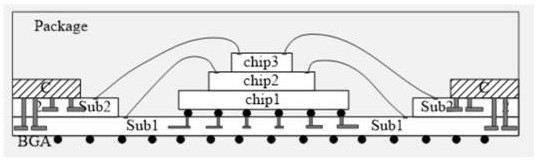

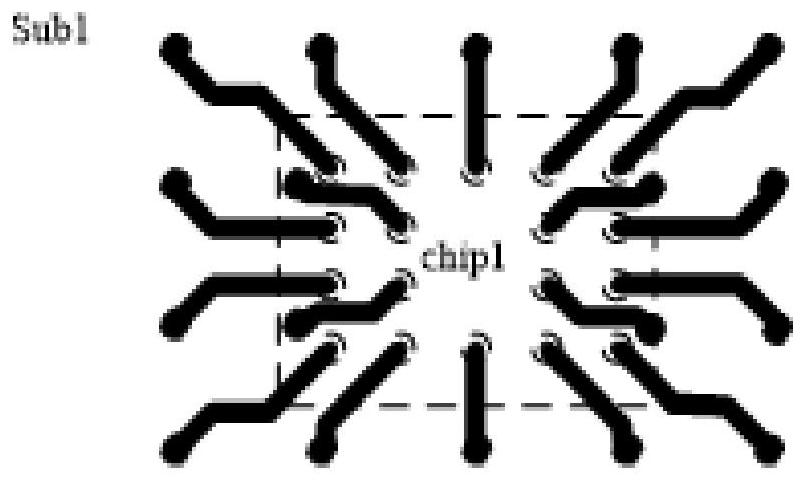

[0018] Step 2, flip the bottom chip1 over, discard the original gold wire interconnection, and use fan out interconnection, such as figure 2 , making full use of the space of the bottom substrate (Sub1); since the other two chips do not have fan-out interconnection conditions, the gold wire interconnection method is still used;

[0019] Step 3, adjust the original interconnection position of the gold wires so that chip2 is connected to Sub1, and chip3 is connected to Sub2; this adjustment can firstly vacate the space of Sub3, and the gold wire routing is steeper, reducing the waste of space;

[0020] Step 4, replace the original position of Sub3 with a ring capacitor, such as image 3 , according to the normal size of the chip, this capacitor will be sufficient for the decoupling nee...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com