Photoetching overlay mark and preparation method thereof

A lithography overlay and marking technology, which is applied in the field of lithography overlay marks and their preparation, can solve the problem of increasing the reject rate and production cost of power semiconductor devices, reducing the manufacturing process accuracy of power semiconductor devices, and the wear of lithography overlay marks, etc. problem, to achieve the effect of convenient metal peeling, clear metal marking points, clear and smooth contour lines

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

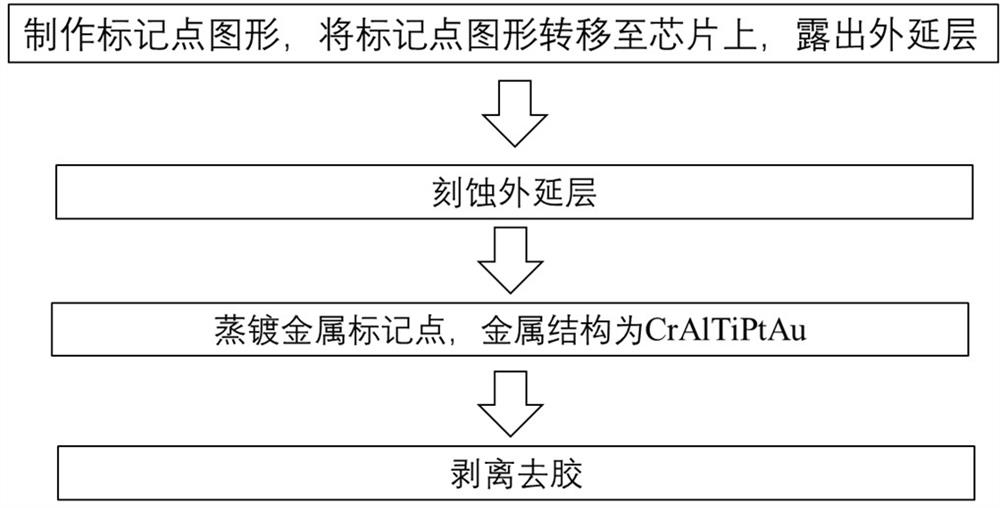

[0038] A photolithographic overlay mark is prepared by the following method:

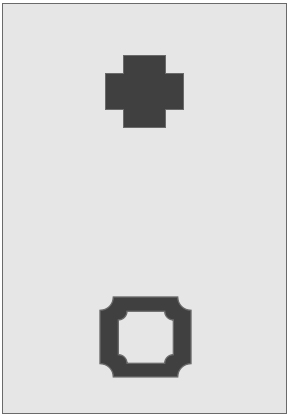

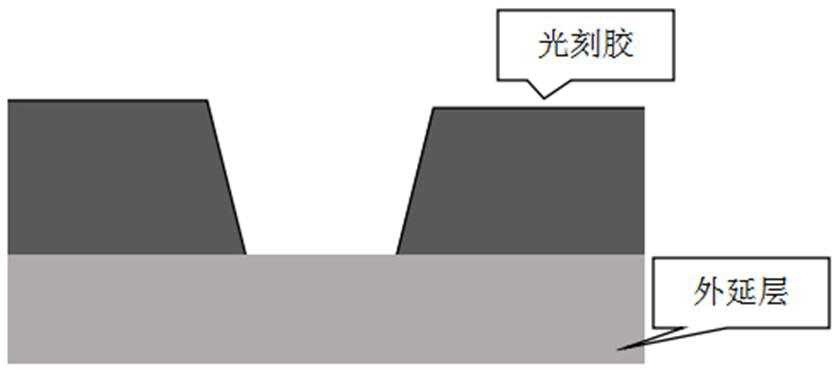

[0039] Step S1: Make a mark point pattern, the mark point pattern is the word "back"; transfer the mark point pattern to the chip by means of uniform glue, exposure, and development to expose the epitaxial layer; use positive photoresist for glue uniformity, and the thickness of the glue is 4μm;

[0040] Step S2: Etching the epitaxial layer; using inductively coupled plasma etching to etch the epitaxial layer, the etching gas is Cl 2 and BCl 3 , the etching depth is 8000A, and the etching angle is 80°;

[0041] Step S3: Evaporate metal marking points, the metal structure is CrAlTiPtAu; the thickness of the first layer of the metal structure is 50A; the thickness of the second layer of Al is 3000A; the thickness of the third layer of Ti is 2000A; the thickness of the fourth layer of Pt is 500A; the thickness of the fifth layer of Au 1000A.

[0042] Step S4: stripping and degumming; after soaking ...

Embodiment 2

[0044] A photolithographic overlay mark is prepared by the following method:

[0045] Step S1: Make a mark point pattern, the mark point pattern is "ten"; transfer the mark point pattern to the chip by means of uniform glue, exposure, and development to expose the epitaxial layer; use positive photoresist for glue uniformity, and the thickness of the glue is 3μm;

[0046] Step S2: Etching the epitaxial layer; using inductively coupled plasma etching to etch the epitaxial layer, the etching gas is Cl 2 and BCl 3 , the etching depth is 6000A, and the etching angle is 70°;

[0047] Step S3: Evaporate metal marking points, the metal structure is CrAlTiPtAu; the thickness of the first Cr layer of the metal structure is 20A; the thickness of the second Al layer is 1000A; the thickness of the third Ti layer is 500A; the thickness of the fourth Pt layer is 200A. The thickness of the fifth layer of Au is 3000A.

[0048] Step S4: stripping and degumming; after soaking in acetone for...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Etching depth | aaaaa | aaaaa |

| Etching depth | aaaaa | aaaaa |

| Etching depth | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More