Method for simultaneously preparing, packaging and using multiple chips

A chip and chip array technology, which is applied in the field of simultaneous preparation and packaging of multiple chips, can solve the problems of increased cost of SiC material devices, achieve increased process complexity, low design complexity and manufacturing process complexity, and enhance product application value Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

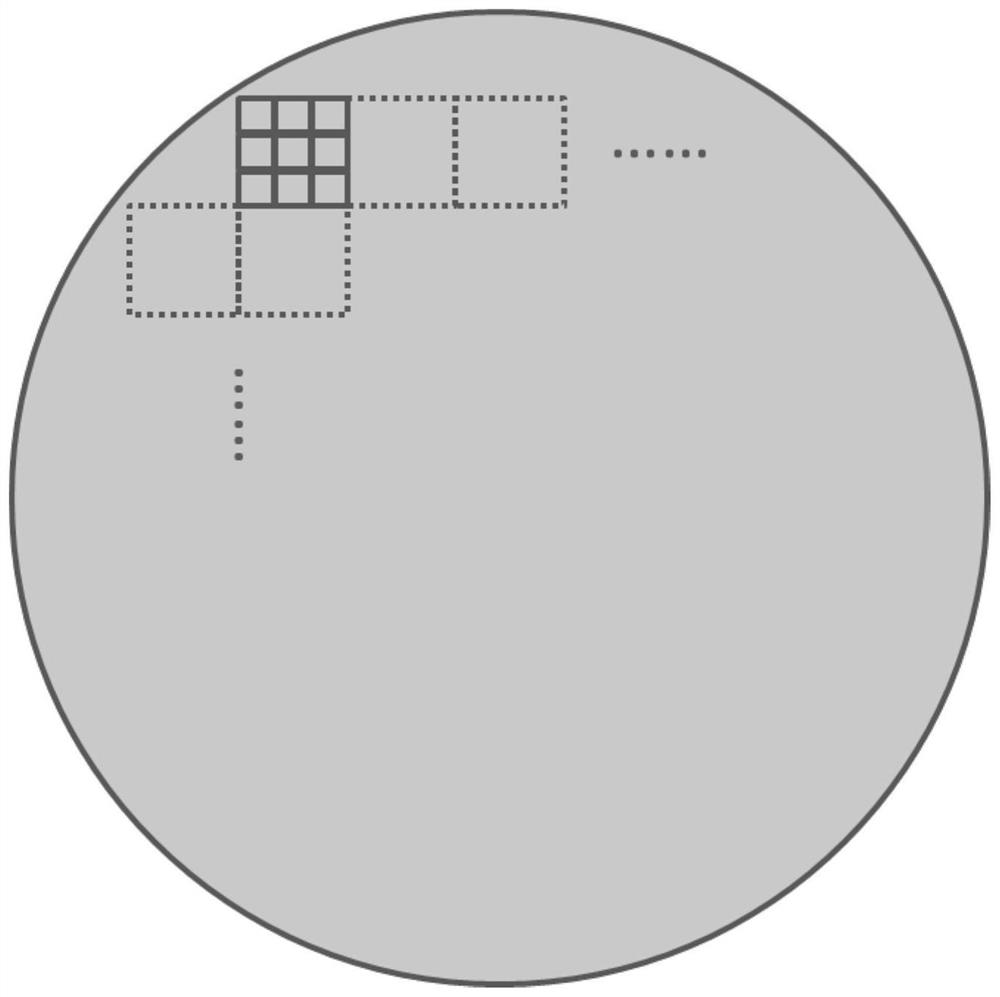

[0036] The invention discloses a method for preparing, packaging and using multiple chips at the same time. It is mainly suitable for small-volume, high-power silicon carbide devices. The application situation is mainly for array units. This invention is mainly but not limited to the following: Condition:

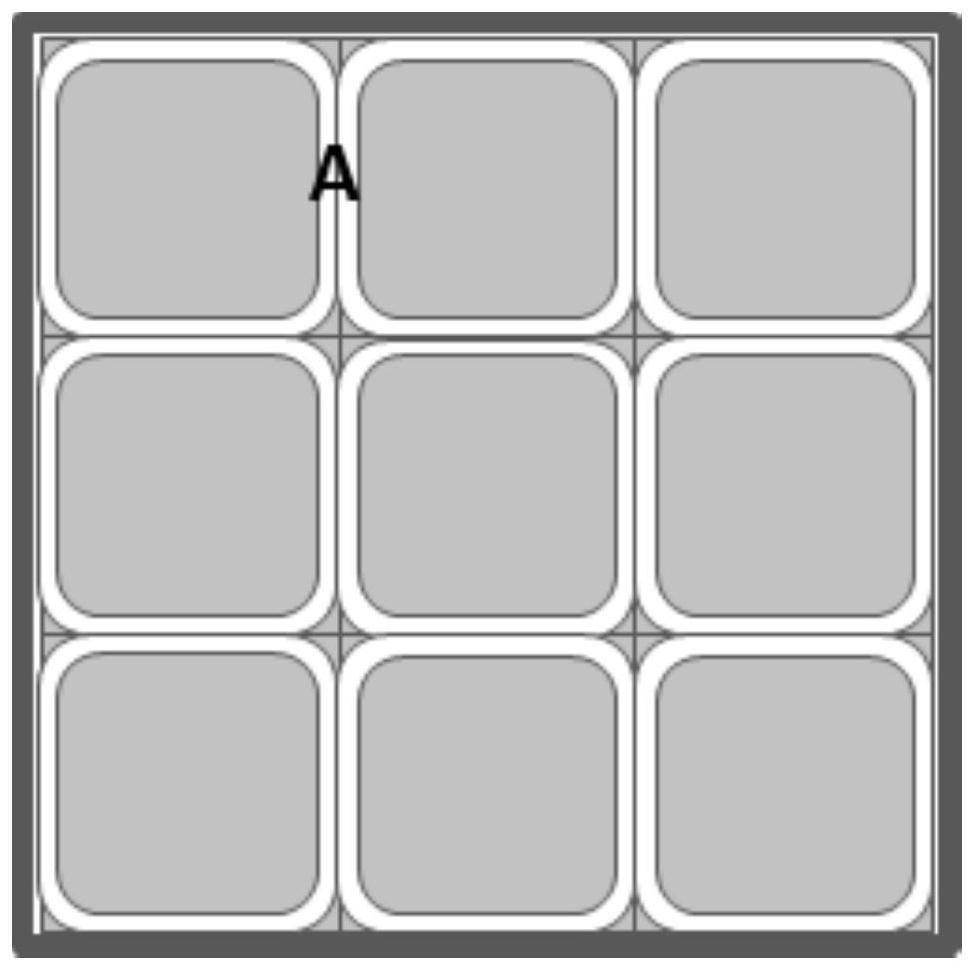

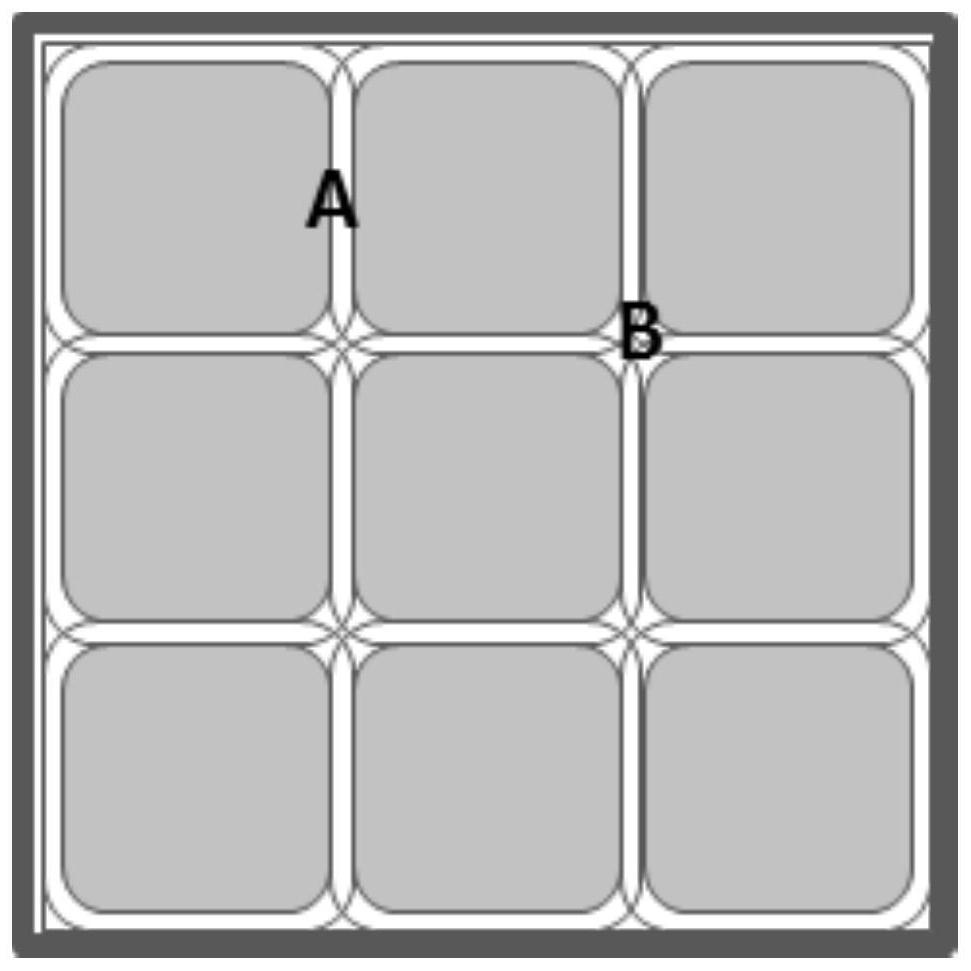

[0037] When used in module A, if multiple same low-current chips are required, the chips in the array can be used in different positions of the module through an external circuit;

[0038] B In circuits that require high reliability, since the chips in the array unit are taped out of the same batch and the same chip, the device consistency is high, and the devices can back up each other;

[0039] C Even only from the perspective of cost reduction, the different chips of the array unit are connected in parallel and independent of each other. Through testing and screening, waste chips in the array unit can be eliminated without wire bonding (or not used in the circuit after w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More