Joint simulation optimization method for on-chip power supply distribution network

A technology of power distribution and co-simulation, applied in the direction of design optimization/simulation, special data processing applications, etc., can solve the problems of discontinuous circuit design and optimization, time-consuming and time-consuming for researchers, and simplify the manual design process , The effect of promoting the process of industrialization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

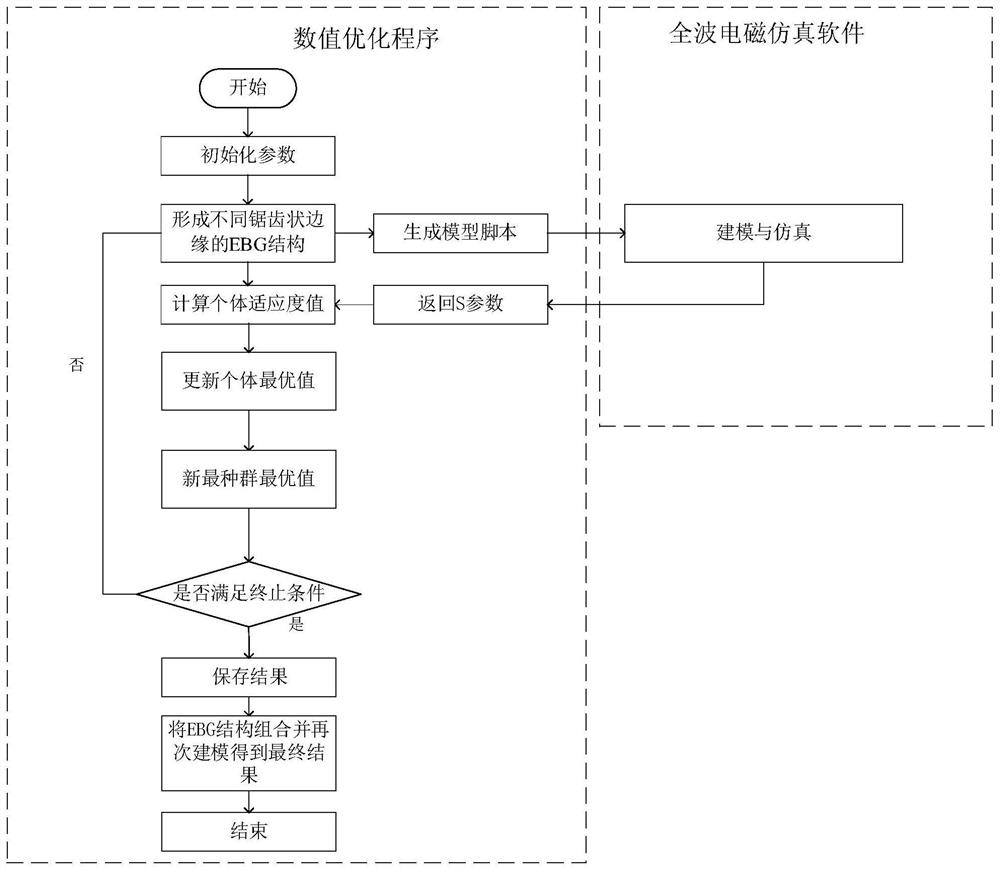

[0032] The present invention will be described in detail below in conjunction with the accompanying drawings and embodiments.

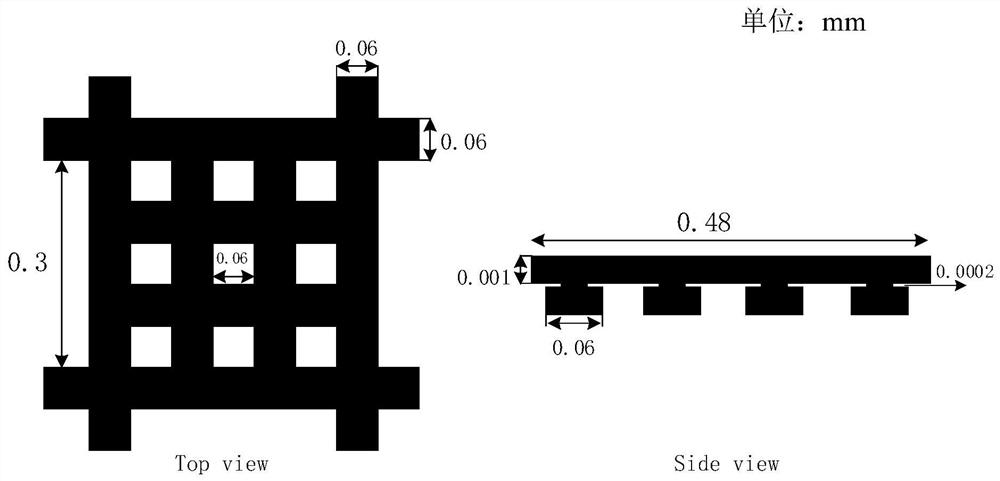

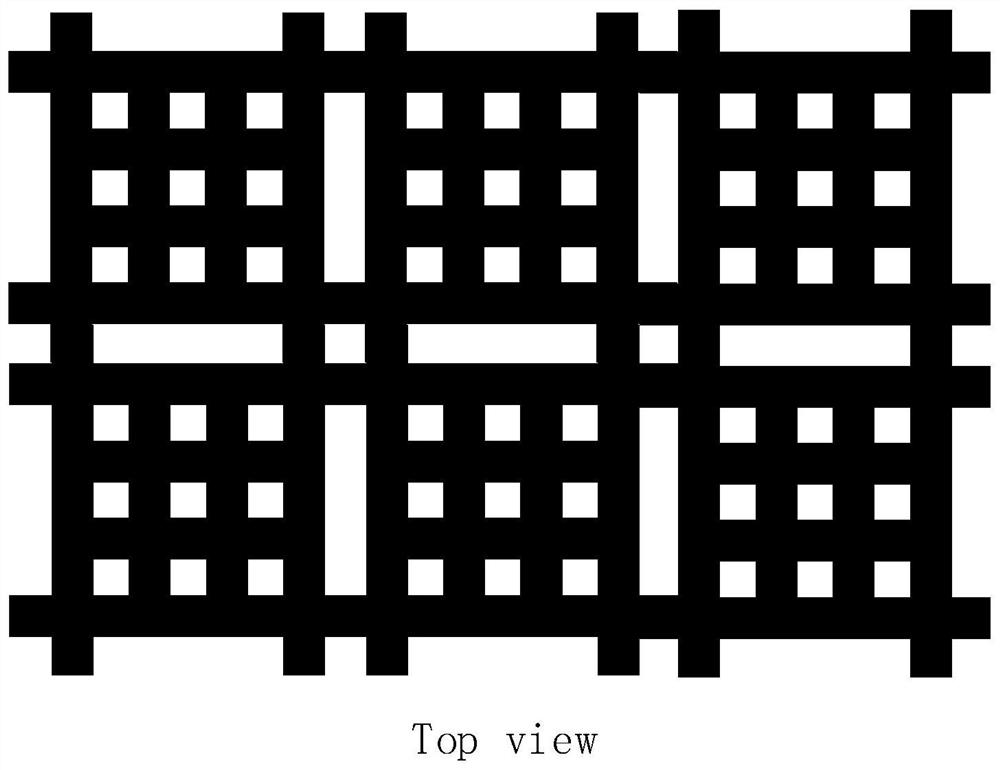

[0033] The present invention is based on the optimization and transformation of the existing Grid-type-PDN structure obtained by periodically cutting off the power line and the ground line. figure 1 It is a schematic diagram of the structure of the on-chip power distribution network according to the embodiment of the present invention. Due to the limitation of the process and the consideration of signal integrity, the co-simulation optimization method of the on-chip power distribution network of the present invention is only for figure 1 In the edge area of the power line and ground line, the structural variable parameter values of the rest of the on-chip power distribution network are in figure 1 Both have been identified, and their material is set to copper.

[0034] The length, width and depth of the pixel blocks in the area to be optimized in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More