Lookup table optimization for programming languages that target synchronous digital circuits

A technology of synchronous numbers and look-up tables, applied in visual/graphic programming, CAD circuit design, text database query, etc., can solve the problems of poor execution, wrong execution of electronic circuits, time-consuming, etc., and achieve the effect of wide optimization range

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

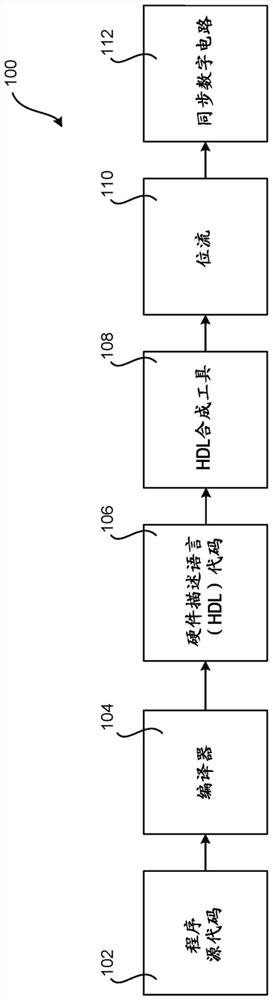

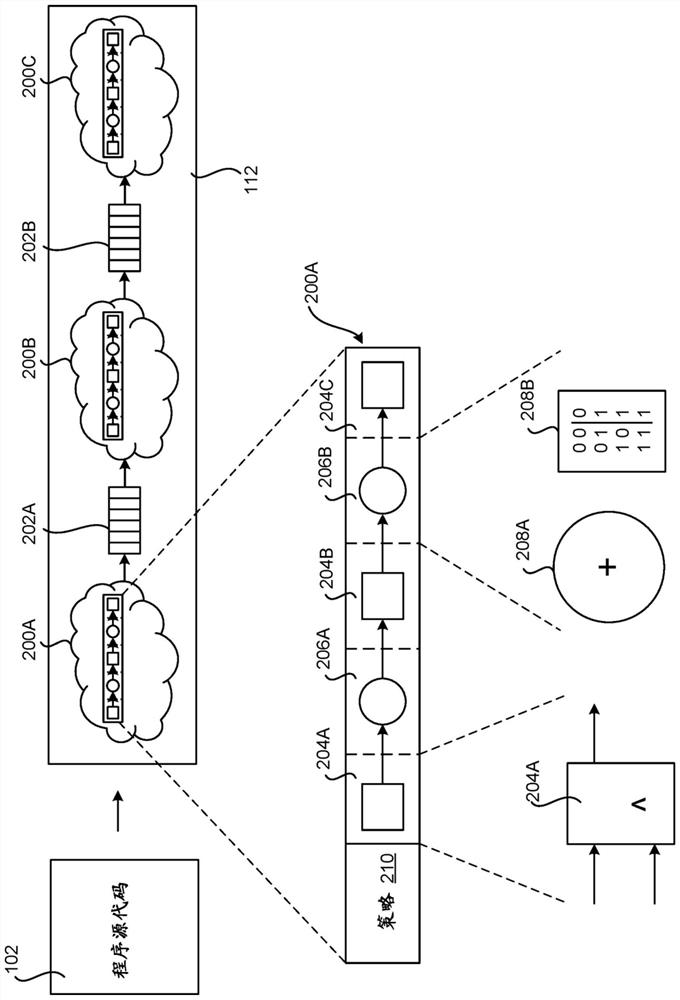

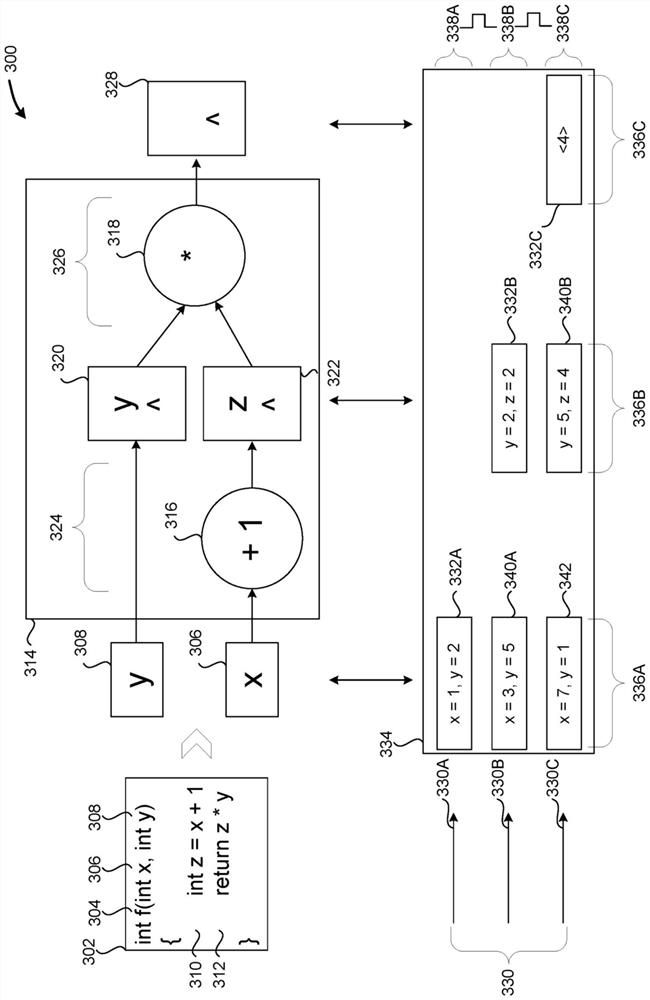

[0025] The following detailed description is directed to high-level languages and compilers that optimize the use of LUTs. As discussed briefly above, embodiments of the technology disclosed herein reduce the SDC area, the number of pipeline stages, the number of registers used to pass data between pipeline stages, and the number of clock cycles used to execute a given computational expression . These technical advantages are realized by reducing the number of LUTs, clock cycles, and registers used to perform a given function. Other technical benefits not specifically mentioned herein may also be realized by implementations of the disclosed subject matter.

[0026] Although the subject matter described herein is presented in the general context of an SDC executing on a personal computer, those skilled in the art will appreciate that other implementations can be implemented in conjunction with other types of computing systems and modules. Those skilled in the art will also ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More