Preparation method of gate dielectric layer

A gate dielectric layer and dielectric layer technology, which is applied in the manufacture of circuits, electrical components, semiconductors/solid-state devices, etc., can solve the problems of high time cost and removal of residues, so as to improve yield rate, shorten preparation time, and improve device reliability properties as well as the effect of device performance on

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach

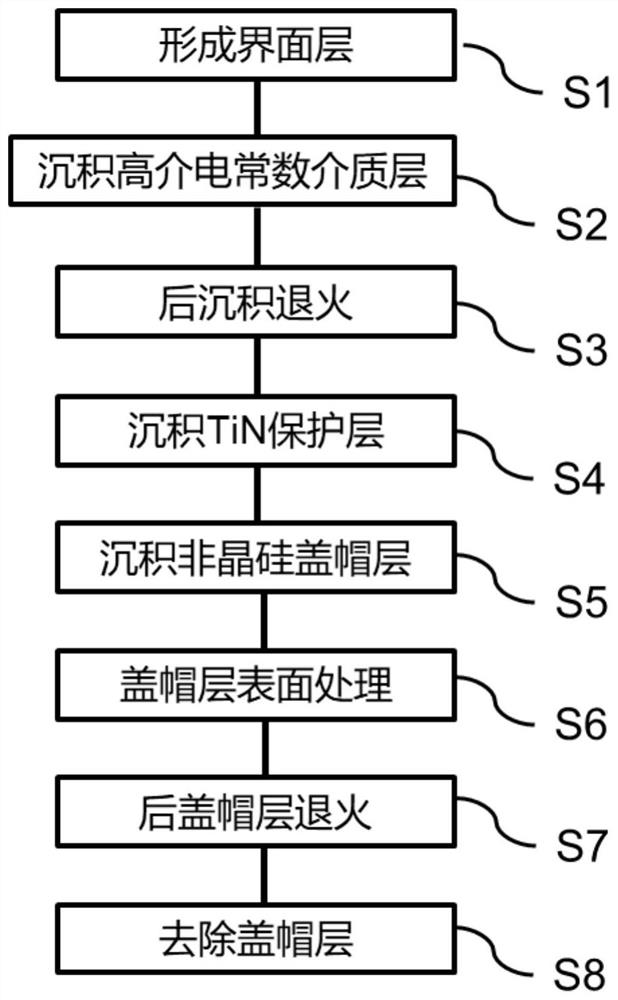

[0036] figure 1 It is a schematic diagram of the preparation method of the gate dielectric layer of the present invention, and the specific implementation method is as follows:

[0037] The method for preparing a gate dielectric layer in this embodiment includes:

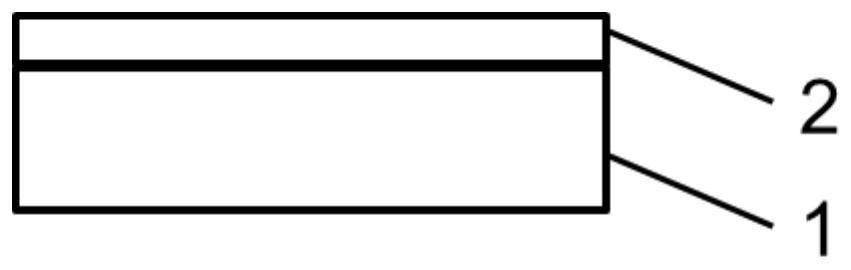

[0038] Step S1, such as figure 2 , provide a silicon substrate, form an ultra-thin interface layer 2 on the surface of the silicon substrate 1, the ultra-thin interface layer 2 is SiO 2 ; The interface layer is formed by means of wet ozone carrying or atomic oxygen thermal oxidation, the thickness of the interface layer is 6 to 10 angstroms, and the thickness of the interface layer in this embodiment is 8 angstroms.

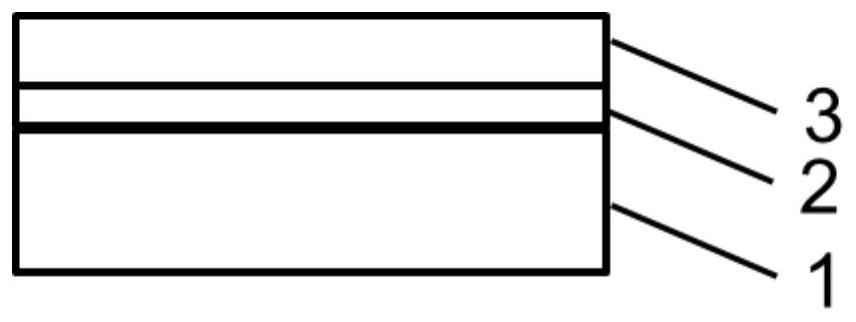

[0039] Step S2, such as image 3 , to deposit a layer of high dielectric constant dielectric layer 3; the high dielectric constant dielectric layer 3 is deposited by atomic layer deposition, and the material of high dielectric constant dielectric layer 3 is HfO 2 , the thickness of the high dielec...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com