Power device drain-source parasitic capacitance sub-circuit model and modeling method thereof

A technology for power devices and circuit models, applied in instruments, electrical digital data processing, calculations, etc., can solve problems such as large errors in drain-source capacitance modeling, modeling errors in drain-source capacitances, and inability to meet industry standards, to ensure accurate performance and reliability, increased precision, and increased flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

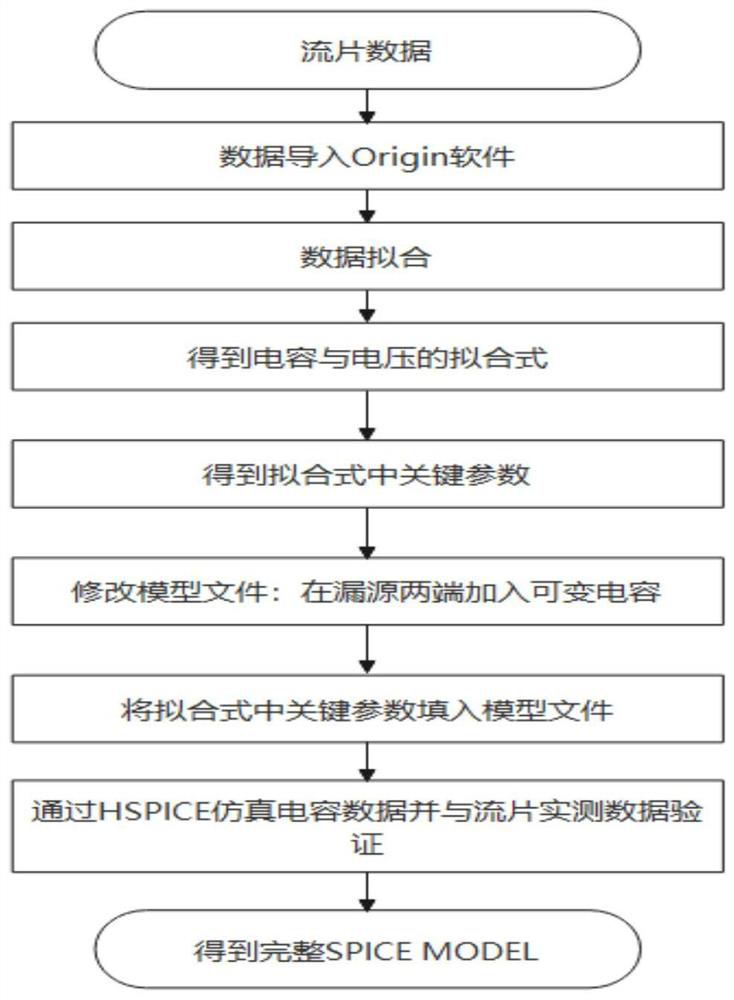

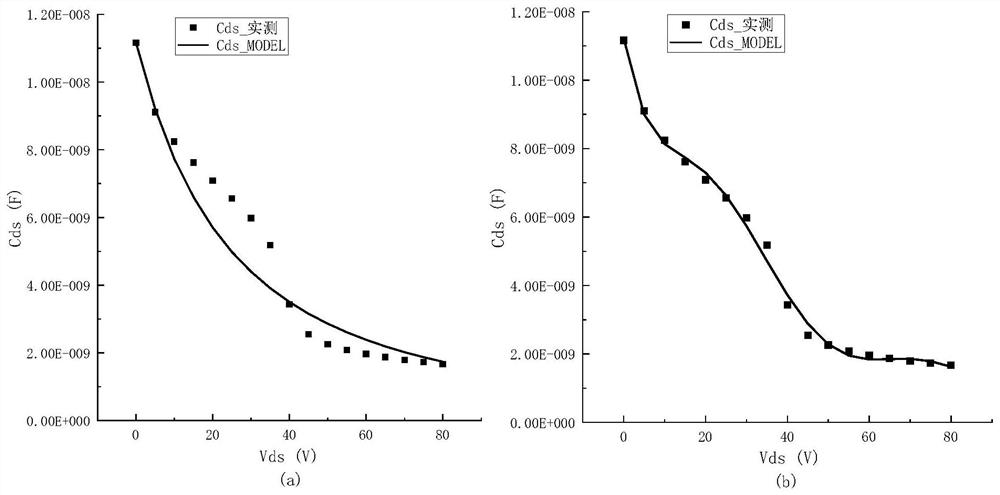

[0022] refer to figure 1 , the modeling process in this embodiment specifically includes:

[0023] 1. Data processing

[0024] Capacitance voltage data processing of tape-out: first, based on the actual test data of the drain-source capacitance voltage of the tape-out device, and import the actual test capacitance voltage data into the Origin software; then process the data in the Origin software, and use the fitting function to establish a drain The source voltage is the independent variable and the drain-source capacitance is the dependent variable sixth-order polynomial fitting formula, such as expression (1), and finally the key coefficients in the fitting formula are obtained, such as A and B in the expression (1) 1 , B 2 , B 3 , B 4 , B 5 , B 6 ;

[0025] Cds=A+B 1 *Vds+B 2 *Vds 2 +B 3 *Vds 3 +B 4 *Vds 4 +B 5 *Vds 5 +B 6 *Vds 6 (1)

[0026] In the formula, Vds is the drain-source voltage;

[0027] 2. Create a model file

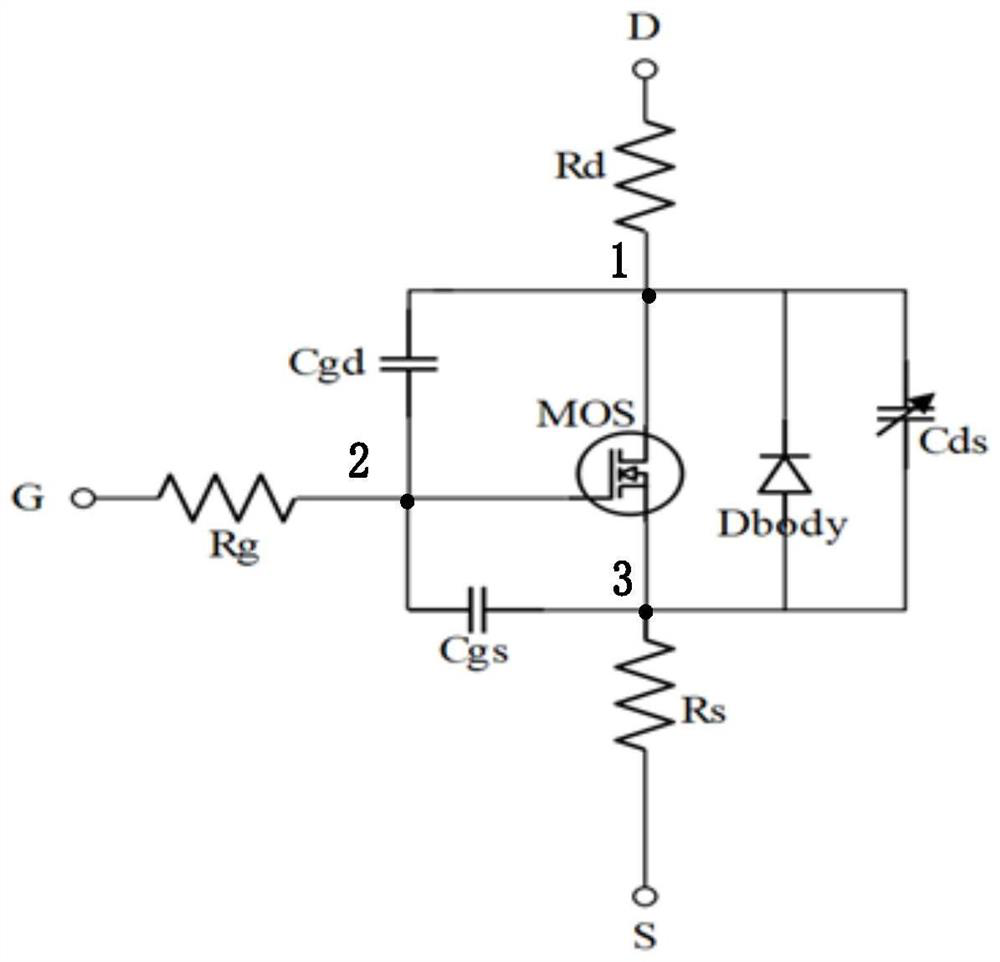

[0028] In the model file fo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More