Flip chip packaging unit and related packaging method

A technology of flip chip and packaging method, which is applied in the direction of electrical components, electric solid devices, circuits, etc., can solve the problems of increased risk of damage, etc., and achieve the effect of taking into account the heat dissipation requirements of the chip, not easy to deform, and not easy to fall off

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0010] In the following detailed description of the present disclosure, numerous specific details of circuits, elements, methods, etc. are described for a better understanding of the embodiments of the present disclosure. Those skilled in the art will understand that the present disclosure may be practiced without some of the details. In order to explain the present disclosure clearly, some details well known to those skilled in the art will not be repeated here.

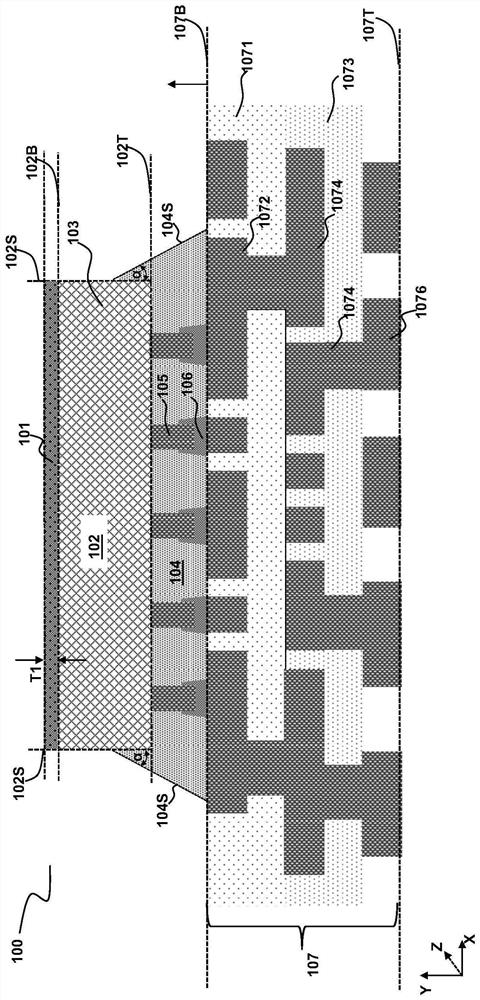

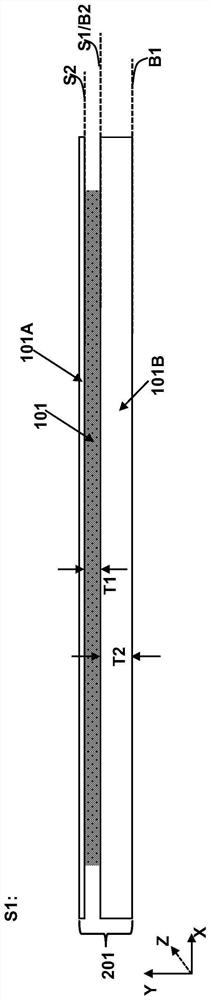

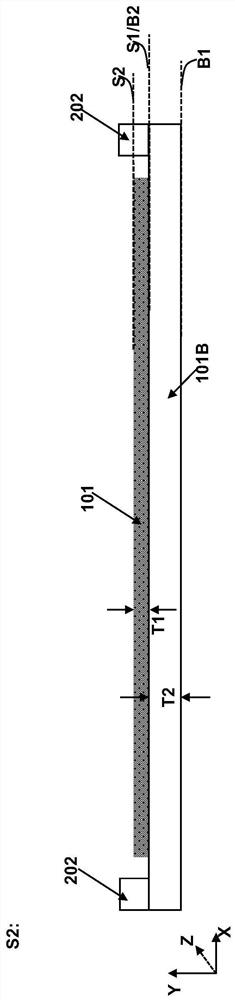

[0011] figure 1 A partial longitudinal (Z-axis direction) cross-sectional view of the flip-chip packaging unit 100 according to an embodiment of the present disclosure is illustrated. figure 1 It can be regarded as a cross-sectional view of the flip-chip packaging unit 100 on the X-Y plane in a vertical coordinate system defined by mutually perpendicular X-axis, Y-axis and Z-axis. Such as figure 1 As an example, the flip-chip packaging unit 100 may include at least one integrated circuit chip 102 packaged therein...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thermal conductivity | aaaaa | aaaaa |

| Thermal conductivity | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com