Power semiconductor characteristic parameter test system and method

A technology of power semiconductors and characteristic parameters, which is applied in the direction of single semiconductor device testing, measuring electricity, measuring devices, etc., can solve the adverse effects of power electronic devices, does not target and adapt to high-voltage SiC power devices, and cannot dynamic characteristics of high-voltage SiC power devices Problems such as parameter testing, to achieve the effect of improving the accuracy of parameter testing, avoiding electromagnetic interference, and realizing high current carrying

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0069] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0070] On the contrary, the invention covers any alternatives, modifications, equivalent methods and schemes within the spirit and scope of the invention as defined by the claims. Further, in order to make the public have a better understanding of the present invention, some specific details are described in detail in the detailed description of the present invention below. The present invention can be fully understood by those skilled in the art without the description of these detailed parts.

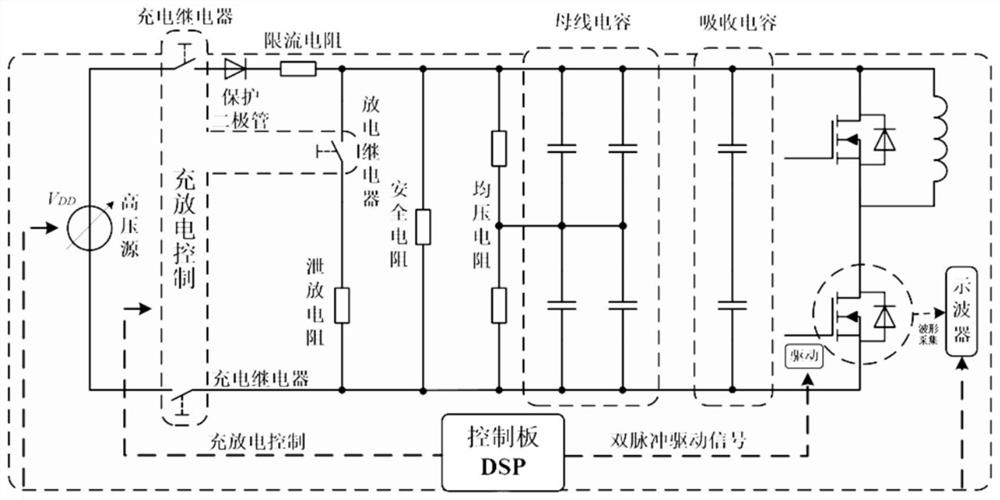

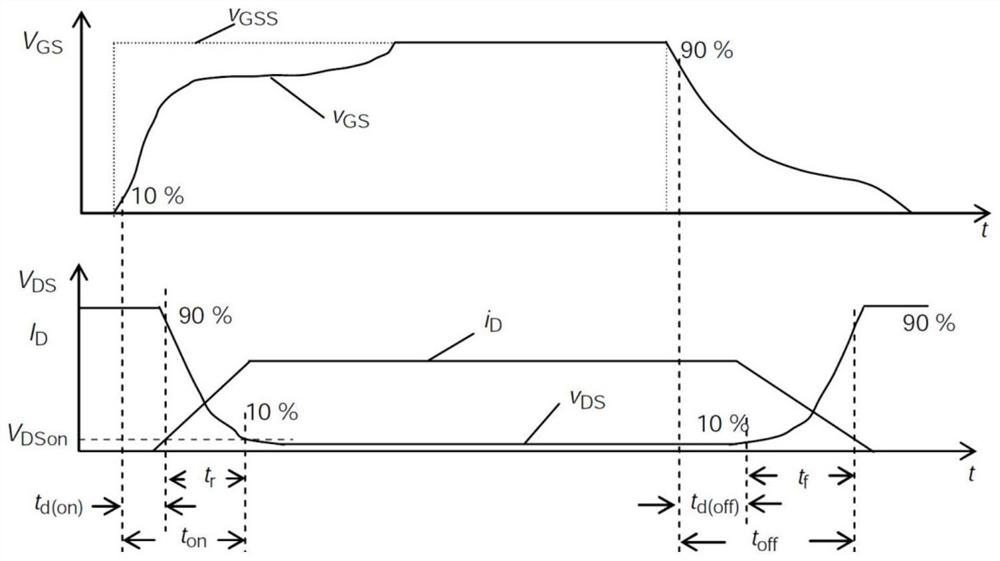

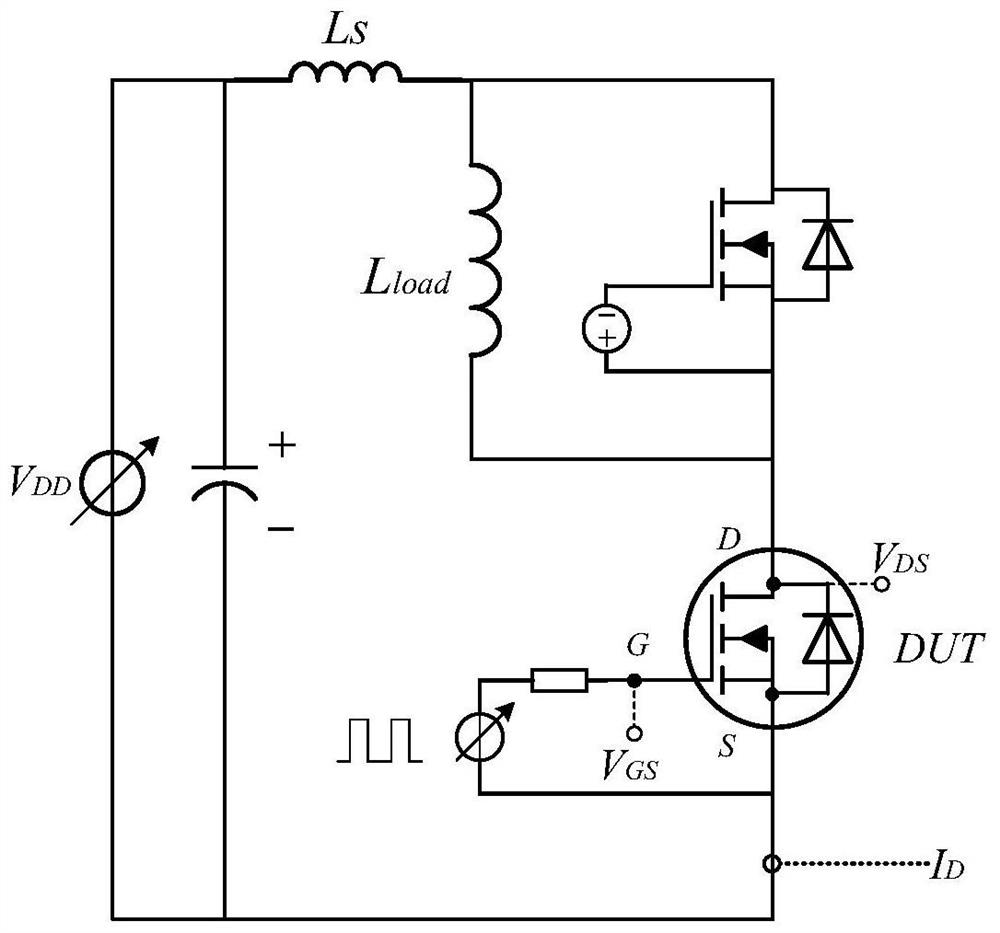

[0071] Such as Figure 1-Figure 3 As shown, a power semiconductor characteristic parameter test syste...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More