Three-dimensional integrated structure, preparation method and assembly method

A three-dimensional, hinged structure technology, applied in semiconductor/solid-state device manufacturing, electrical solid-state devices, semiconductor devices, etc., can solve the problem of limited applicability of vertical conductive interconnection structures, lack of rigid hard connections, low integration, etc. problems, to achieve the effect of micro-miniature field, good mechanical stability, and low technical difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0100] The specific preparation method of a three-dimensional integrated structure in Example 1 is as follows:

[0101] Step 1, such as Figure 4A As shown, a conductive blind hole 60 embedded in the silicon substrate 1 with an axial direction perpendicular to the surface of the silicon substrate 1 is prepared from one surface of the sheet silicon substrate 1, and filled with metal;

[0102] Step 2, such as Figure 4B As shown, the second and fourth metal rewiring layers 7a and 7b are prepared on the opening surface of the conductive blind hole 60 of the silicon substrate 1, as well as the pad on the top thereof;

[0103] Step 3, such as Figure 4C As shown, the surface of the above-mentioned process is temporarily bonded to the glass carrier 8, and the other surface of the silicon substrate 1 is thinned, polished, etched, etc., and the bottom of the metal filling material of the conductive blind hole 60 is exposed, forming TSV conductive via 6;

[0104] Step 4, such as ...

Embodiment 2

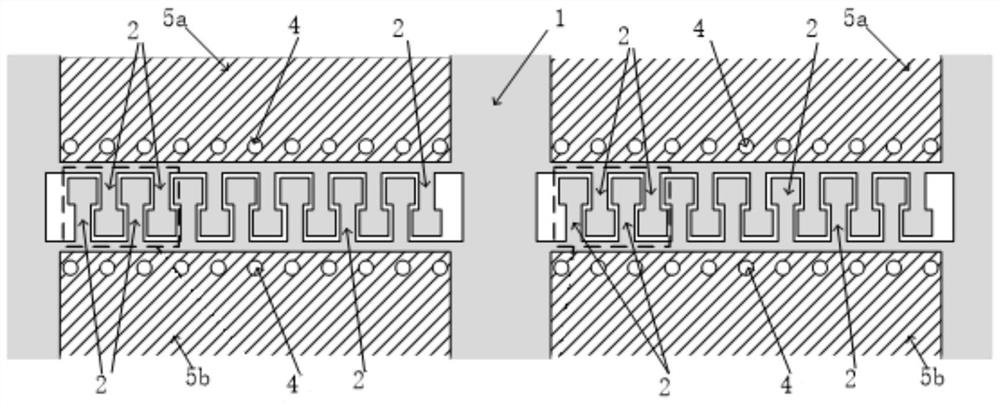

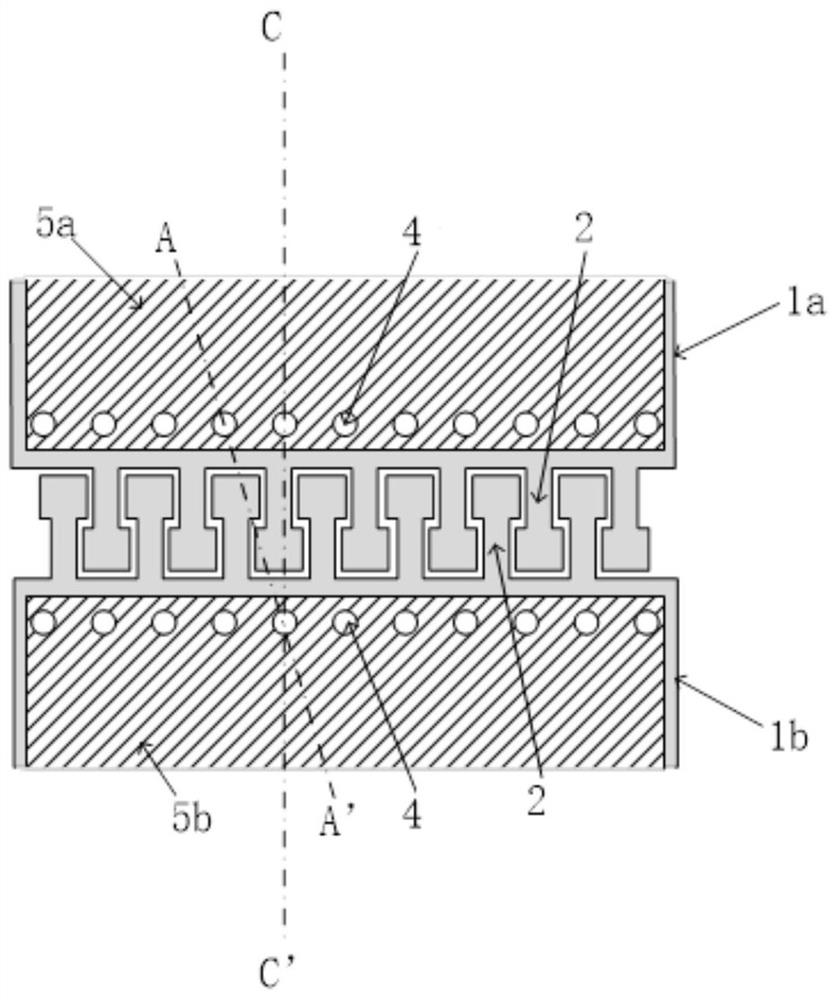

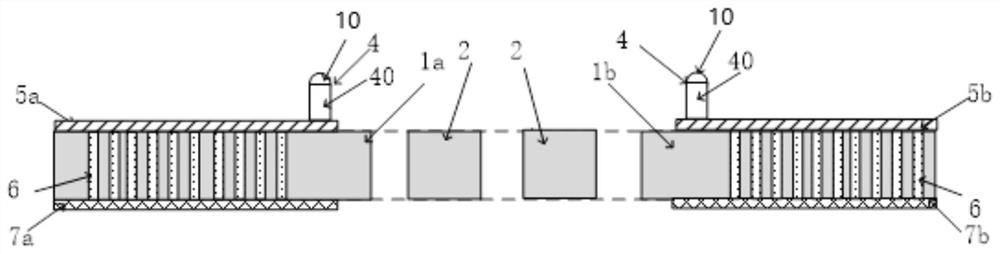

[0115] Such as Image 6 , shown in 7 and 8, the specific preparation method of a three-dimensional integrated structure in the present embodiment 2 is as follows:

[0116] Step 1, such as Figure 4A As shown, a conductive blind hole 60 embedded in the silicon substrate 1 with an axial direction perpendicular to the surface of the silicon substrate 1 is prepared from one surface of the sheet silicon substrate 1, and filled with metal;

[0117] Step 2, such as Figure 4B As shown, the second and fourth metal rewiring layers 7a and 7b are prepared on the opening surface of the conductive blind hole 60 of the silicon substrate 1, as well as the pad on the top thereof;

[0118] Step 3, preparing a flexible strip, which is a multi-layer dielectric film composed of the metal interlayer dielectric in the second and fourth metal rewiring layers 7a and 7b, arranged on the first substrate 1a and the second substrate 1b in half side;

[0119] Step 3, such as Figure 4C As shown, the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More