Super-radiation light-emitting diode chip integrated with lateral detector and preparation method of super-radiation light-emitting diode chip

A technology of superluminescent light-emitting diodes, which is applied in the direction of semiconductor devices, final product manufacturing, sustainable manufacturing/processing, etc., and can solve problems such as increased ripple coefficient of superluminescent light-emitting diodes, enhanced chip reflectivity, and unfavorable weak light detection. , to achieve the effects of low-light detection, improvement of ripple coefficient, and avoiding the increase of ripple coefficient

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

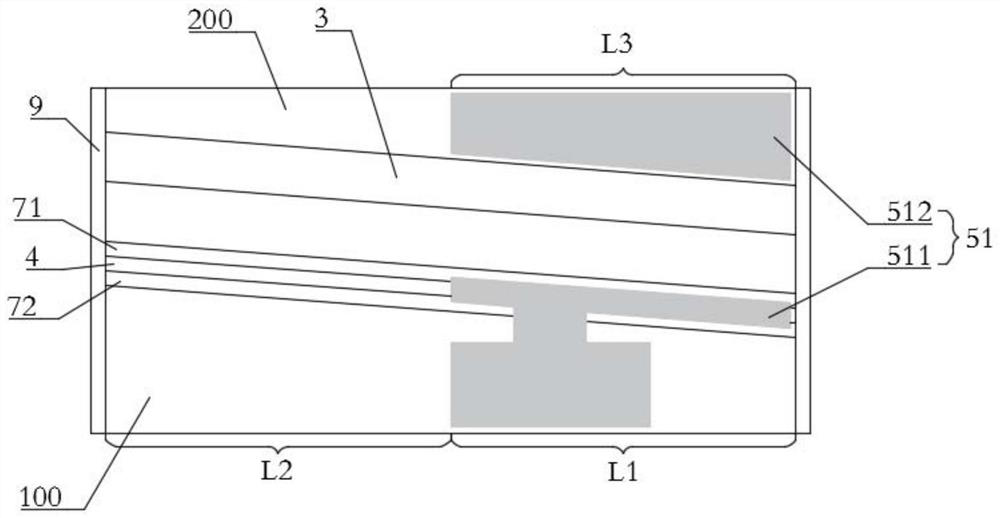

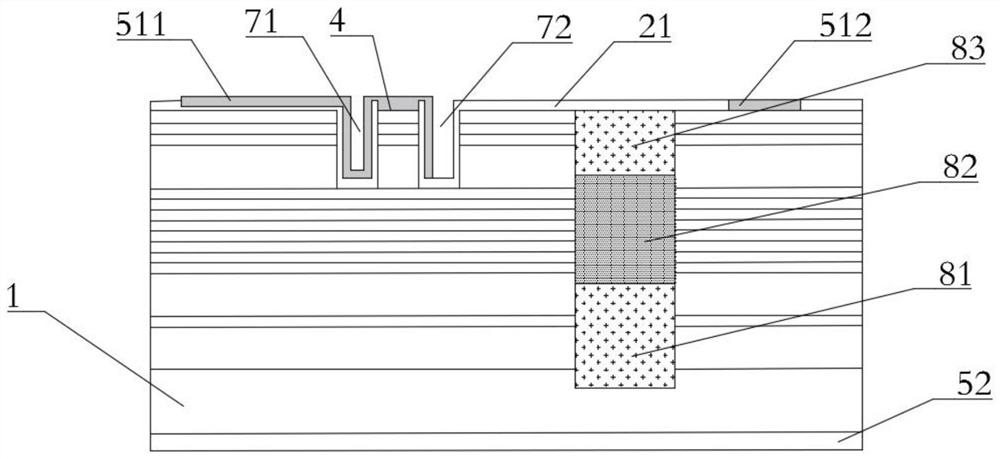

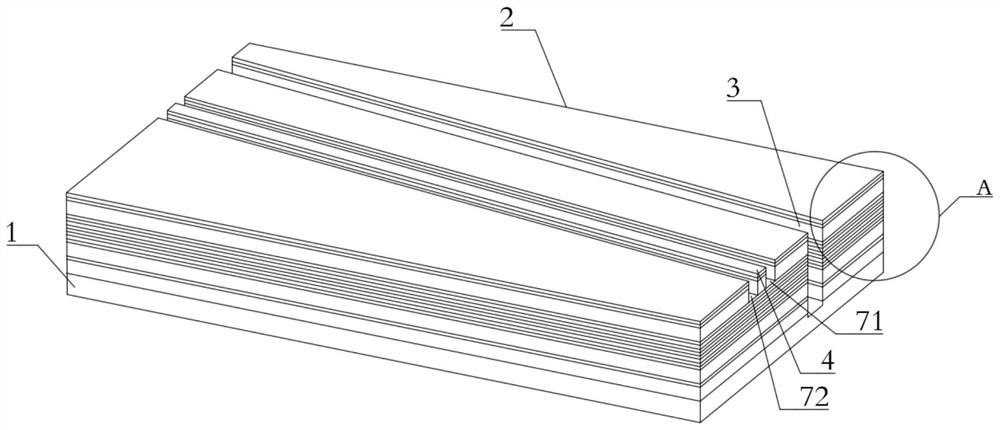

[0040] Such as figure 1 Shown is a schematic structural view of a superluminescent light-emitting diode chip integrated with a lateral detector according to Embodiment 1 of the present invention. The superluminescent light emitting diode chip with integrated lateral detector in this embodiment includes a superluminescent light emitting diode 100 and a lateral detector 200 integrated on the same chip. Specifically, this embodiment includes a substrate 1 and a substrate 1 formed on the same chip. The epitaxial wafer 2 on the substrate 1, the upper surface of the epitaxial wafer 2 is formed with an isolation groove 3 penetrating the epitaxial wafer 2 downward, and the isolation groove 3 can separate the epitaxial wafer 2 into an independent first part and The second part, the first part is used to form the SLED 100 , and the second part is used to form the lateral detector 200 . Specifically, the upper surface of the epitaxial wafer 2 of the first part is formed with a ridge waveg...

Embodiment 2

[0048] Such as Figure 5 Shown is a flow chart of a method for preparing a superluminescent light emitting diode chip integrated with a lateral detector in embodiment 2 of the present invention, which is used to prepare the superluminescent light emitting diode chip integrated with a lateral detector in embodiment 1. This embodiment specifically includes the following steps:

[0049] S100: Provide a substrate 1, and grow an epitaxial wafer 2 on the substrate 1.

[0050] Specifically, an n-InP substrate 1 is provided, and an n-InP buffer layer 201, an n-InGaAsP extended waveguide layer 202, an n-InP spacer layer 203, and an n-AlGaInAs transition layer are sequentially grown on the InP substrate 1. layer 204, n-AlInAs lower confinement layer 205, i-AlGaInAs lower waveguide layer 206, AlGaInAs active layer 207, i-AlGaInAs upper waveguide layer 208, p-AlInAs first upper confinement layer 209, p-InP second upper limit Value layer 210, p-InGaAsP etch stop layer 211, p-InP third up...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More