Rapid optimization method for half-space mapping of microstrip circuit in combination with Gaussian process

A microstrip circuit and Gaussian process technology, applied in CAD circuit design, special data processing applications, etc., can solve the problems of difficult optimal structure of neural network, high consumption of computer resources, and many initial training samples, and reduce the number of training samples. , the effect of less optimization parameters and faster convergence speed

- Summary

- Abstract

- Description

- Claims

- Application Information

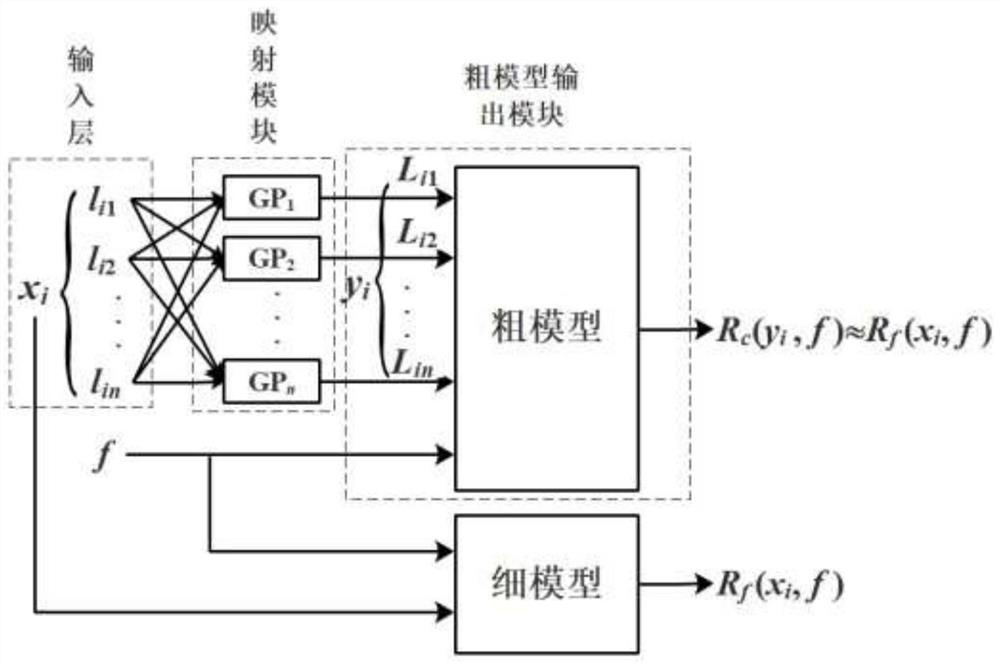

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

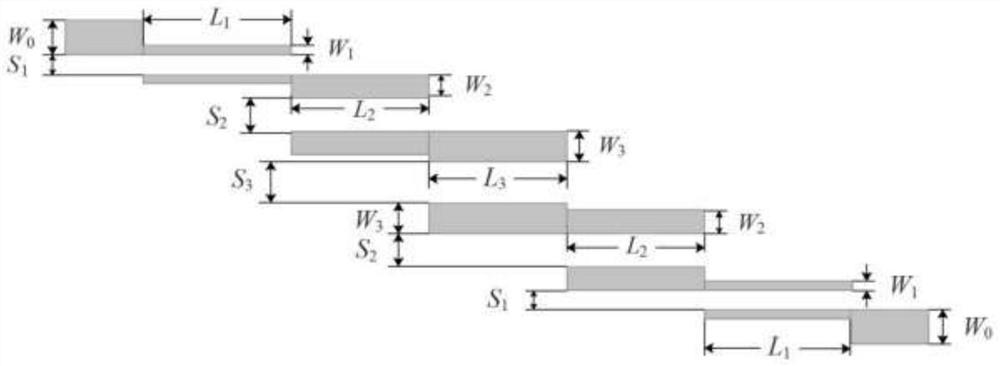

[0031] In order to show the technical scheme and beneficial effect of the present invention more clearly and clearly, now combine a image 3 The W-band microstrip parallel coupled filter design example shown is illustrated.

[0032] The dielectric substrate adopted by the filter of this embodiment has a relative permittivity of ε r =3.8 fused silica substrate with a thickness of 0.1 mm. The width of each microstrip line has been determined, respectively W 0 =0.211mm, W 1 = 0.1mm, W 2 = 0.16mm, W 3 = 0.18 mm.

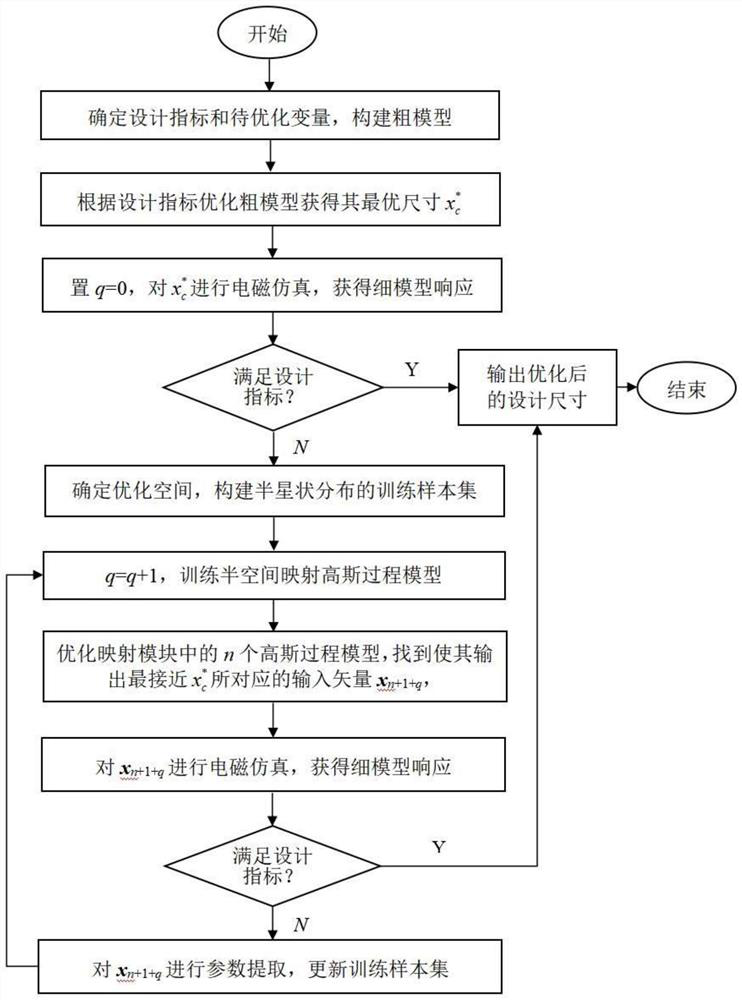

[0033] The optimization process of this embodiment is as follows:

[0034] Step 1: Build an equivalent circuit model in the ADS software, and determine the design index of the microstrip filter. The design index is:

[0035] S 11 ≤-15dB, for 79.2GHz≤f≤83.6GHz

[0036] S 21 ≤-30dB, for 70GHz≤f≤77.4GHz

[0037] S 21 ≤-30dB, for 85.8GHz≤f≤92GHz

[0038] There are six structural variables to be designed, namely L 1 , L 2 , L 3 , S 1 , S 2 , S 3 , written i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More