Method of forming a semiconductor device

A semiconductor and device technology, which is applied in the field of semiconductor device formation, can solve the problems of limited improvement effect, increase the difficulty of chemical mechanical polishing of copper, and high cost, so as to optimize the high and low fluctuation state, improve copper butterfly defects, and prolong the service life Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

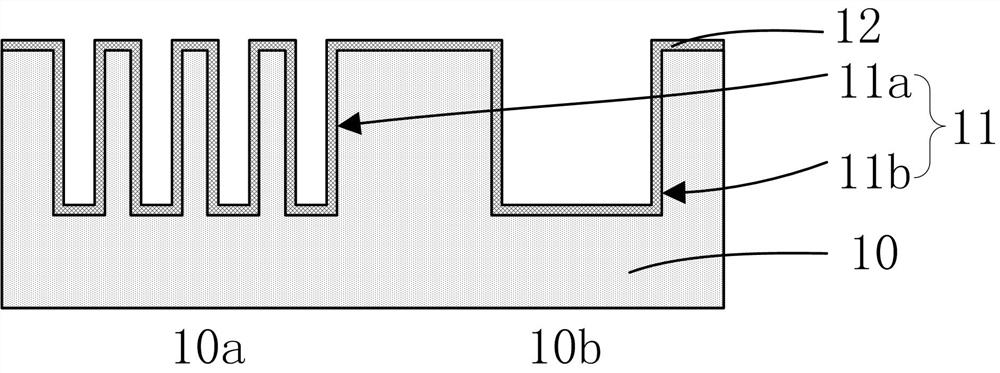

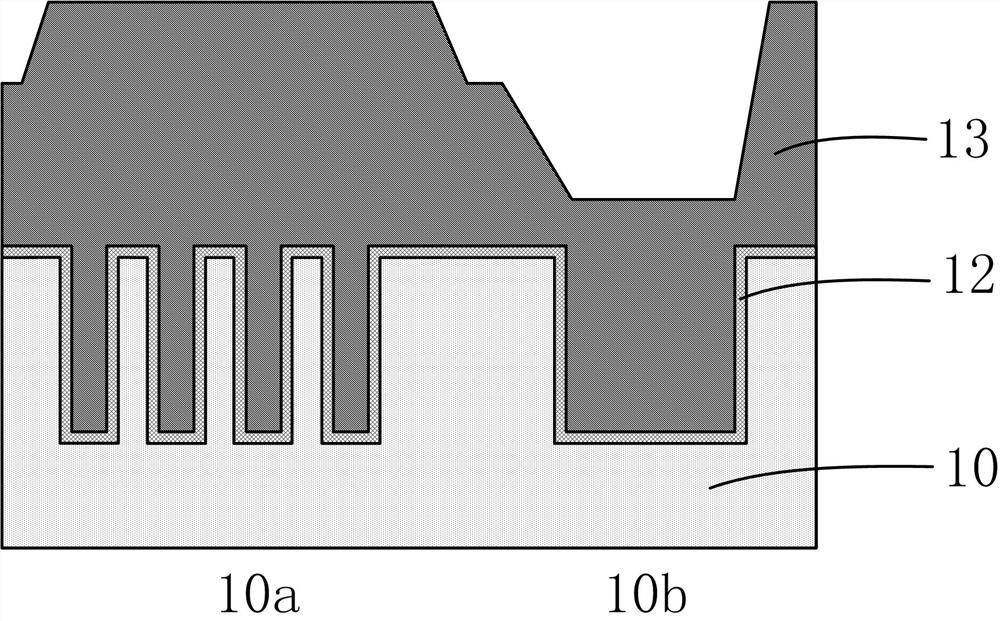

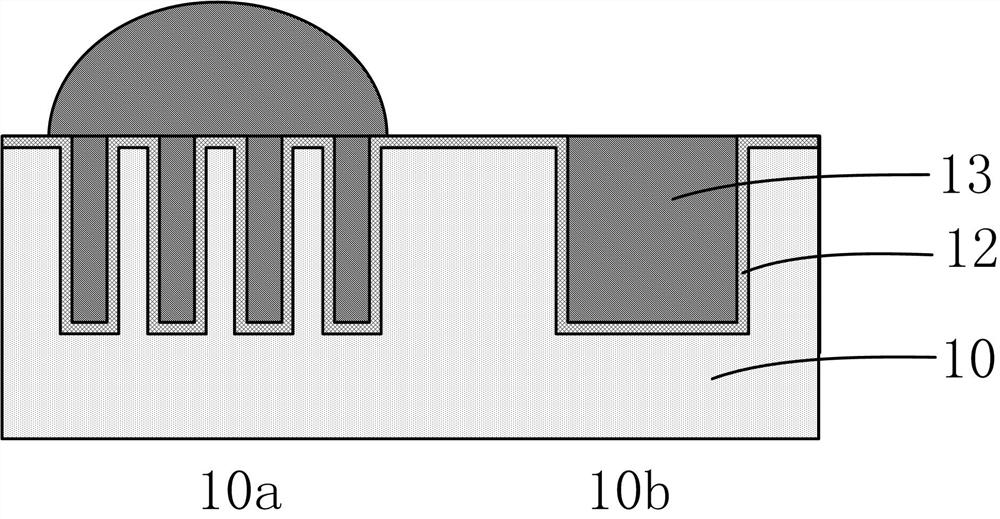

[0035] figure 1 is a schematic diagram of the structure after the grooves are formed on the substrate, figure 2 It is a schematic diagram of the structure after electroplating copper in the groove, image 3 is a schematic diagram of the structure after the copper is planarized, Figure 4 It is a schematic diagram of the structure after the copper has been ground. Please refer to figure 1 As shown, a substrate (not shown) is provided on which a dielectric layer 10 is formed, the dielectric layer 10 including high-density patterned regions 10a and low-density patterned regions 10b. Grooves 11 are formed in the dielectric layer 10. The grooves 11 include a first groove 11a located in the high-density pattern area 10a and a second groove 11b located in the low-density pattern area 10b. The cross-sectional width of the groove 11b is larger than the cross-sectional width of the first groove 11a. Next, a copper seed layer 12 is formed, and the copper seed layer 12 covers the si...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More