FPGA-based high-speed Delay-FxLMS filter design method

A filter design and filter technology, applied in advanced technology, climate sustainability, sustainable communication technology, etc., can solve problems such as excessive adaptive delay m, system output lag, and algorithm convergence decline

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0074] The technical solutions in the embodiments of the present invention will be described clearly and in detail below with reference to the drawings in the embodiments of the present invention. The described embodiments are only some of the embodiments of the invention.

[0075] The technical scheme that the present invention solves the problems of the technologies described above is:

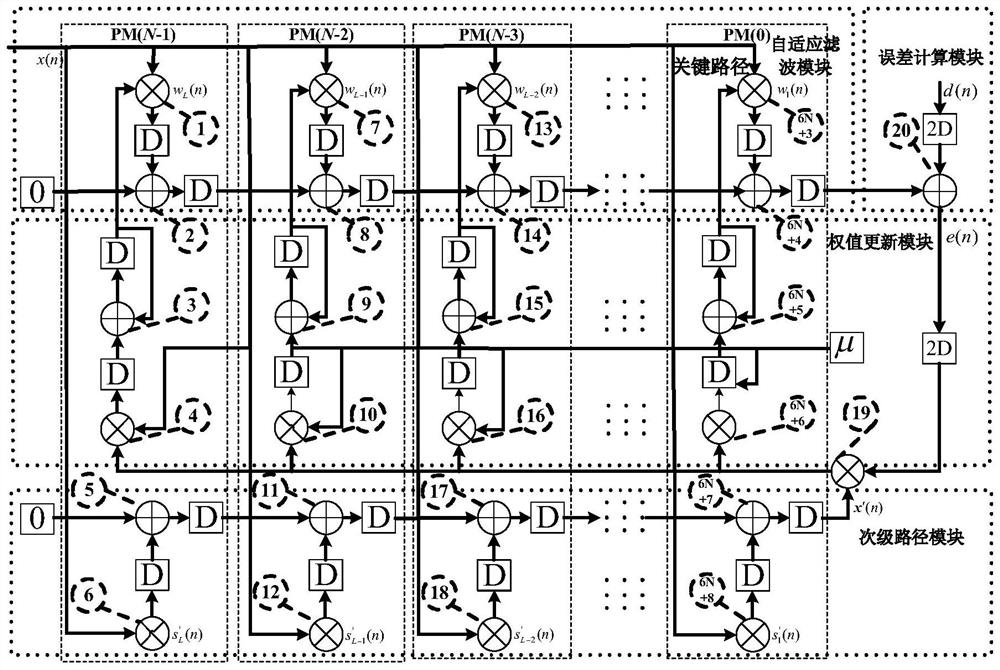

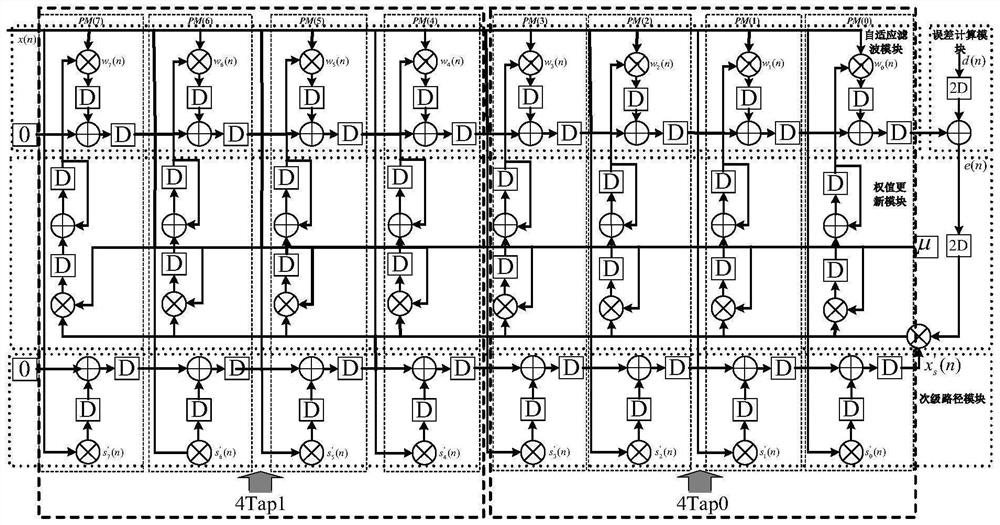

[0076] The invention discloses a FPGA-based high-speed Delay-FxLMS filter design method. It mainly includes three parts (1) DF-DFxLMS filter design (2) TF-RDFxLMS filter design (3) HS-TF-RDFxLMS filter design.

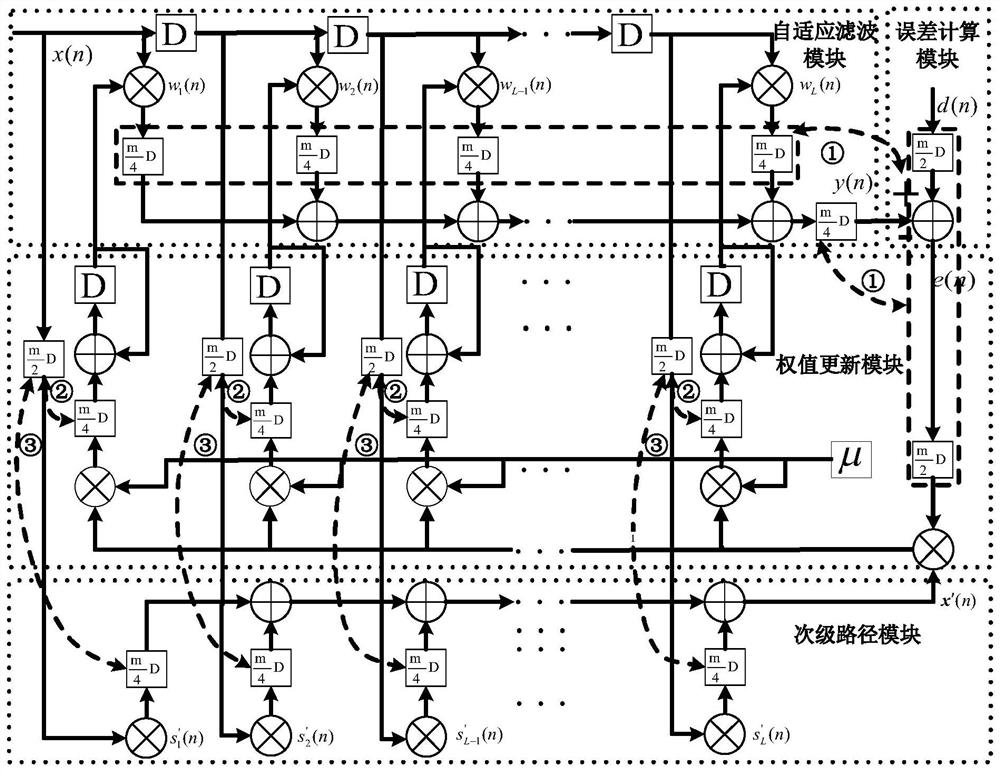

[0077] as attached figure 1 As shown, a kind of FPGA-based high-speed Delay-FxLMS filter design method proposed by the present invention is characterized in that, the DFxLMS filter specifically includes:

[0078] The adaptive filtering module is used to realize the multiplication operation of N weight coefficients and N input signals, and the DF-DFxLMS filter iteration formula is ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More