SOI LIGBT device with planar combined auxiliary electrode structure and preparation method of SOI LIGBT device

A technology for auxiliary electrodes and auxiliary electrode layers, which is applied in semiconductor/solid-state device manufacturing, electrical components, semiconductor devices, etc., can solve the problems of difficult breakdown voltage and low forward conduction voltage drop, and achieve the optimization of lateral electric field and longitudinal Effect of electric field distribution, reduction of forward voltage drop, and increase of device power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

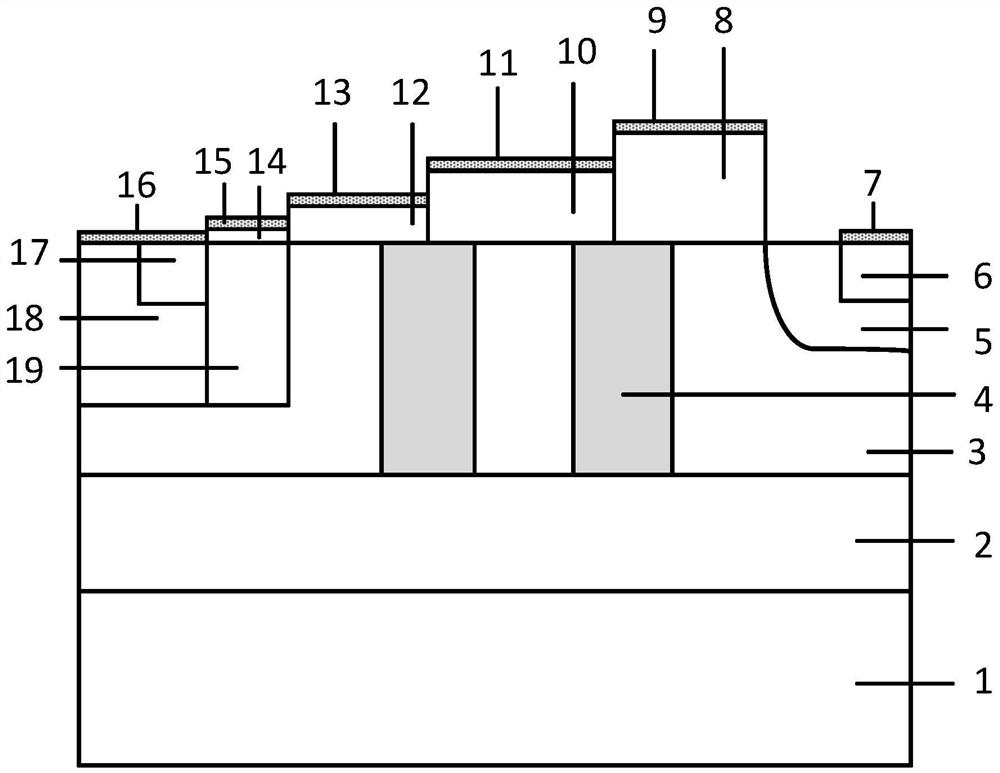

[0052] In the present embodiment, "up", "down" is along the P-type semiconductor material substrate 1 to N type drift zone 3 direction for bottom to top, "thickness" is measured in the direction perpendicular to the N type drift zone 3, "width" is measured in the direction of the gate oxide layer 14 to N type buffer layer 5.

[0053] See Figure 1 , the present embodiment provides a SOI LIGBT device having a planar combination auxiliary electrode structure, the SOILIGBT device comprising a sequentially cascaded P-type semiconductor material substrate 1, SOI base 2 and N-type drift region 3, wherein the thickness of the P-type semiconductor material substrate 1 is 5 to 20μm; The doping concentration of P-type semiconductor material substrate 1 is 5×10 13 cm -3 ~5×10 14 cm -3 ; The thickness of SOI base 2 is 2~4μm; The thickness of N-type drift zone 3 is 2~5μm; The doping concentration of N-type drift zone 3 is 1.0×10 14 ~1.0×10 16 cm -3 。

[0054] N-type drift zone 3 from one side t...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More