Multi-order memory unit

A multi-level storage and polysilicon technology, applied in electrical components, electrical solid-state devices, circuits, etc., can solve the problems of complex peripheral circuits and excessive storage unit size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0013] In order to make the above-mentioned purpose, features and advantages of the present invention more obvious and easy to understand, a preferred embodiment is specifically cited below, together with the accompanying drawings, and described in detail as follows:

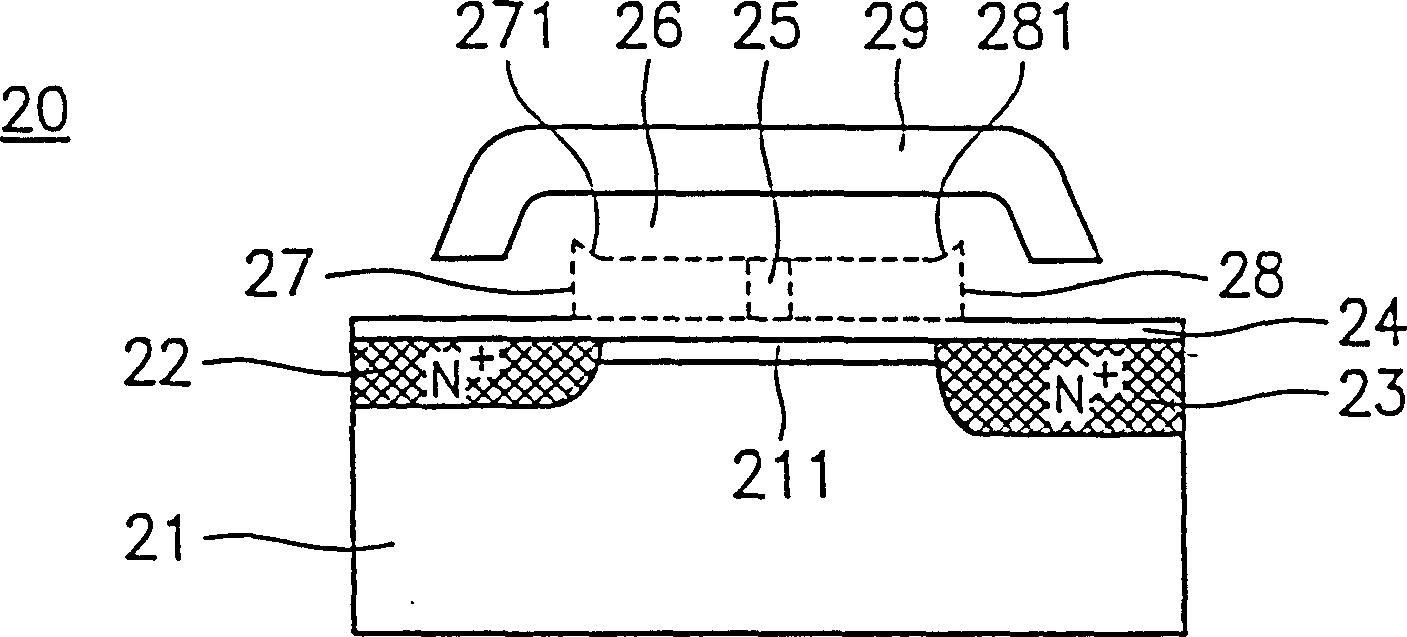

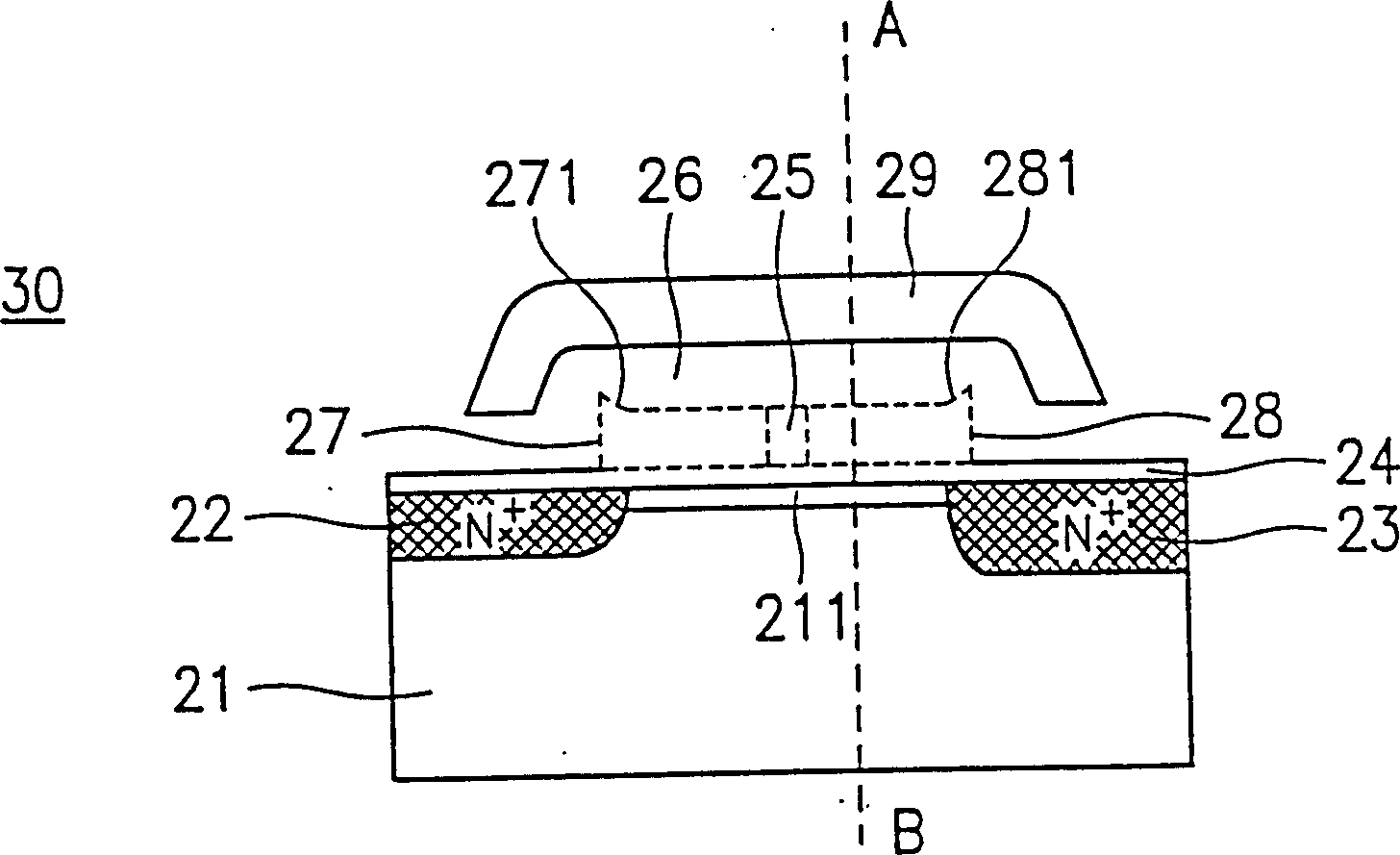

[0014] figure 2 is a cross-sectional view of a multi-level unit 20 according to an embodiment of the present invention. The multi-level memory cell 20 uses an N channel, which has a substrate 21, two doped regions 22, 23 located in the substrate 21 with different doping concentrations and used as source / drain electrodes, a channel region 211, a Gate oxide layer 24 , an insulating layer 25 isolating two floating gates 27 , 28 , a tunnel oxide layer and bird's beak insulating layer 26 , and a control gate 29 . The floating gates 27 and 28 are, for example, polysilicon layers; the insulating layer 25 is, for example, an oxide layer; the bird's beak insulating layer 26 is, for example, a bird's beak oxide layer; a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More