A CMOS circuit structure situated on SOI substrate and manufacturing method thereof

A technology of circuit structure and fabrication method, applied in circuits, electrical components, electrical solid devices, etc., can solve the problem that bulk silicon technology is no longer applicable, and achieve the effects of flexible circuit layout design, reduced length, and high scalability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

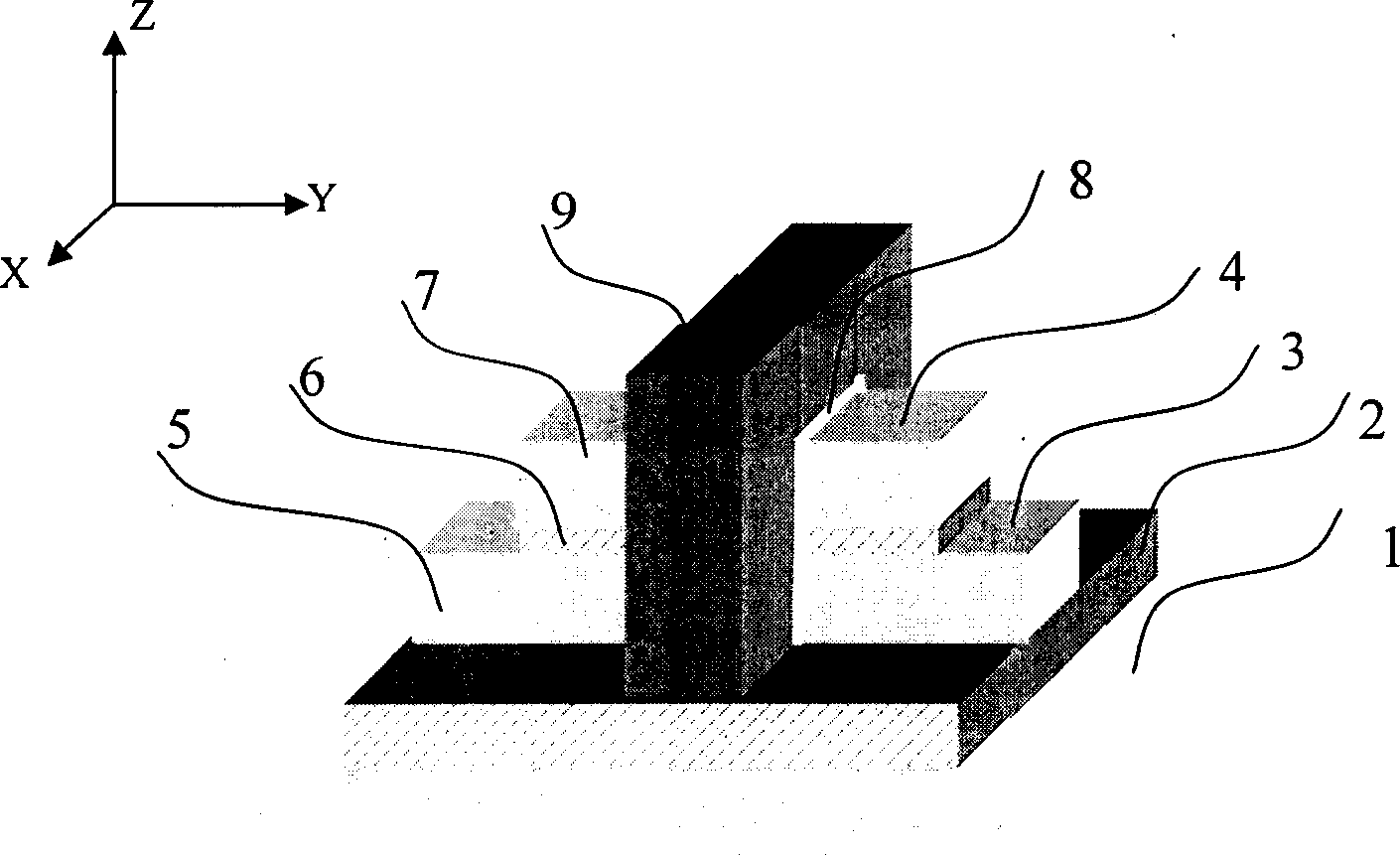

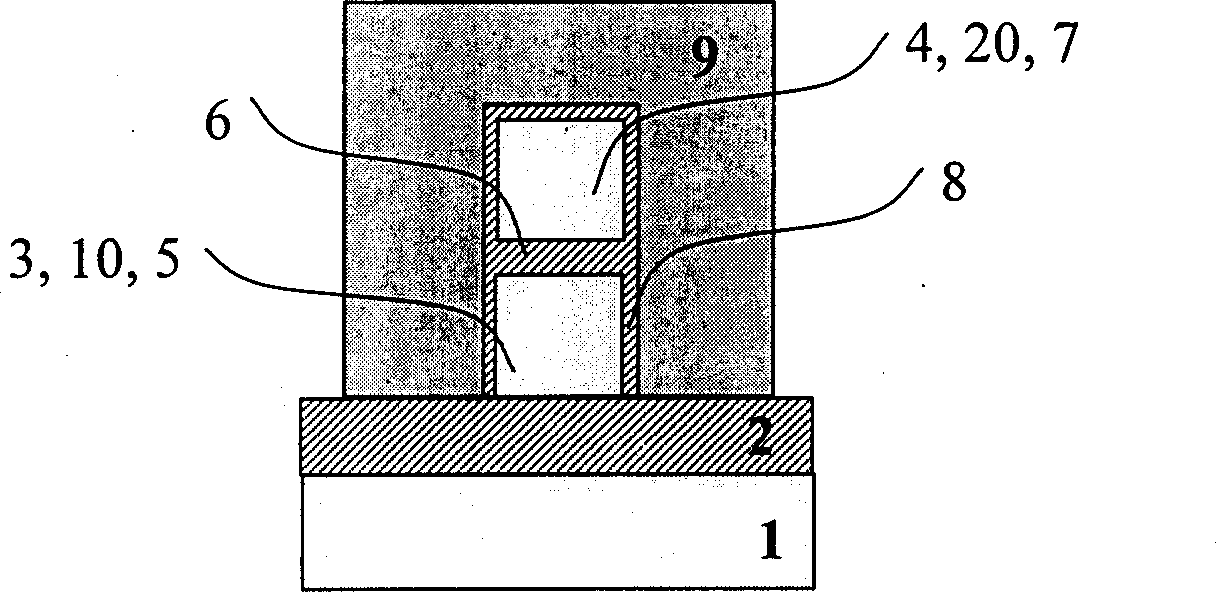

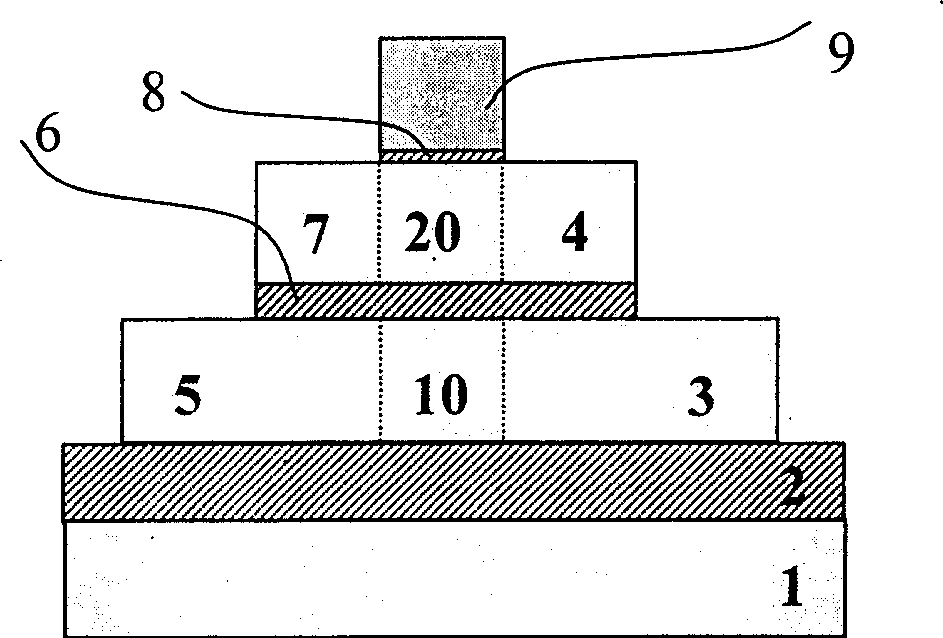

[0044] The CMOS structure proposed by the present invention consists of figure 1 , figure 2 and image 3 shown. in figure 1 is a three-dimensional structure, figure 2 and image 3are the corresponding cross-sectional structures.

[0045] The CMOS structure is formed on a single crystal silicon substrate 1 and is isolated from the substrate 1 by a buried oxide layer 2 .

[0046] The CMOS structure is composed of a polysilicon electrode 9 , a gate dielectric layer 8 , an upper silicon ingot (4+20+7), a lower silicon ingot (3+10+5) and an insulating layer 6 between silicon ingots. Wherein, the lower silicon ingot (3+10+5) is located on the buried oxide layer 2 , the insulating layer 6 is located on the lower silicon ingot, and the upper silicon ingot (4+20+7) is located on the insulating layer 6 . The gate dielectric layer 8 is located on the top and both sides of the upper silicon ingot (4+20+7) and on both sides of the lower silicon ingot (3+10+5). The polysilicon ele...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More