Multilayer stacked storage and manufacture method thereof

A multi-layer stacking and memory technology, which is applied in static memory, read-only memory, semiconductor/solid-state device manufacturing, etc., can solve the problems of unoptimized performance, high cost, and cost reduction, and achieve cost and performance advantages , performance improvement, and the effect of reducing types

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

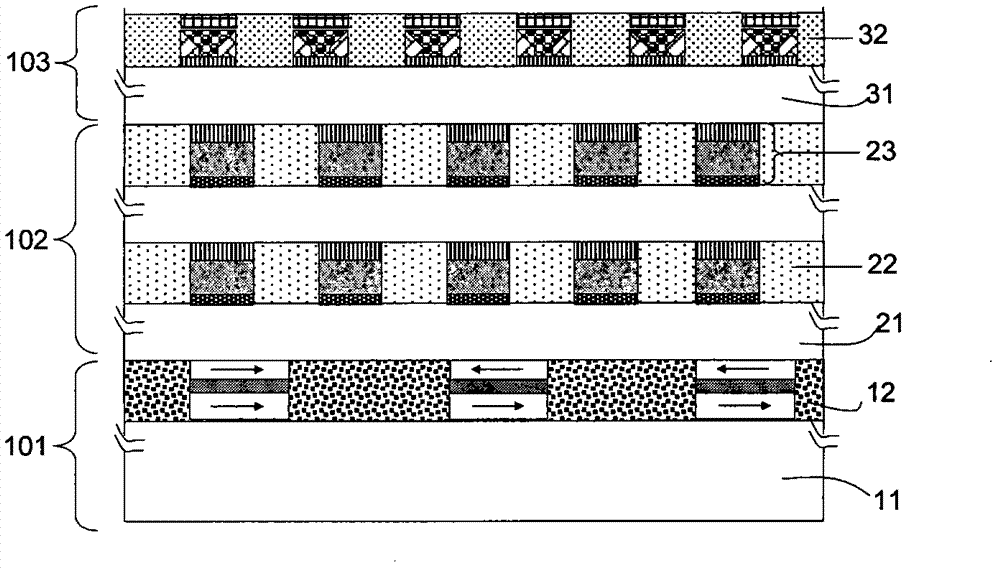

[0042] Figure 1A The schematic diagram of the structure of the resistive switching memory with multi-layer stacking structure is shown, which is better explained, but it does not mean that the present invention is exactly as Figure 1A As shown in this structure, the number of layers, type, size, arrangement and structure of the memory can now be changed, and these are not limiting elements of the present invention.

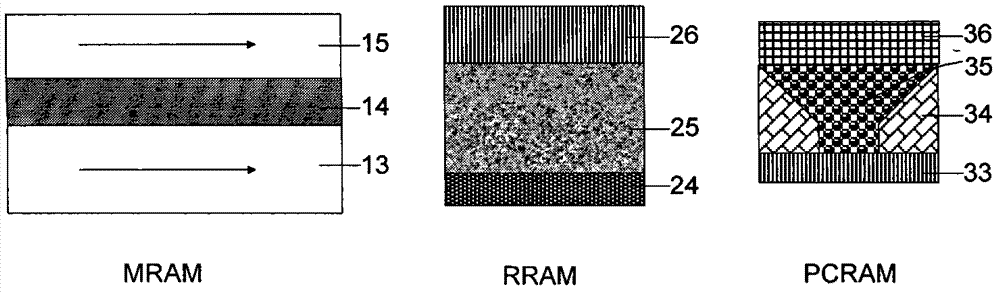

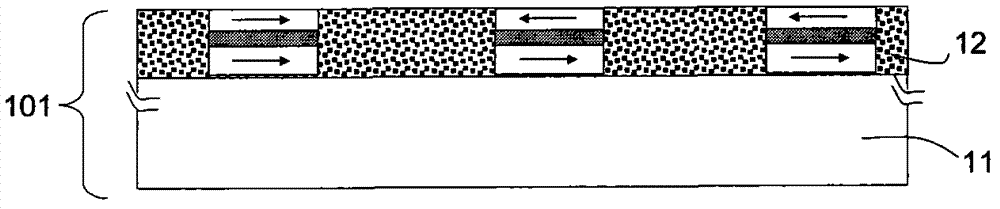

[0043] From Figure 1A It can be seen that the device has a multilayer stack structure, including one MRAM layer 101 , two RRAM layers 102 and one PCRAM layer 103 . Each of the above-mentioned layers not only includes resistive memory cells, but also includes corresponding gate cells (although not shown in the figure, it does not mean that there are none). In addition, layer 101 not only includes magnetoresistive memory units and gating units, but also generally includes peripheral circuits, which are shared by all layers, and play the role of gating and operatin...

Embodiment 2

[0063] In this embodiment, the manufacturing method of the multilayer stacked resistance switching memory of the present invention includes the following steps:

[0064] [Step 1] Manufacture peripheral circuits and two layers of DRAM storage layers on wafer A. These two layers of DRAM cells will be used as high-speed memory.

[0065] [Step 2] Manufacture polysilicon on wafer A using a low-temperature process, manufacture polysilicon diodes and corresponding phase-change memory arrays through semiconductor processes, and obtain polysilicon diode-gated phase-change memory through filling and planarization of dielectric materials layer, the polysilicon diode can be a PN diode or a Schottky diode.

[0066] [Step 3] Continue to deposit polysilicon on the multi-layer memory wafer obtained above to manufacture subsequent storage layers until the desired number of layers is reached.

[0067] 【Step 4】Lead package.

[0068] [Step 5] Practical application. Compared with phase change m...

Embodiment 3

[0070] The invention discloses a method for manufacturing a multi-layer stacked resistance switching memory, comprising the following steps:

[0071] [Step 1] Firstly, the peripheral circuit and the RRAM array are manufactured on the silicon substrate A, wherein the peripheral circuit not only includes the read, write, and erase circuits, but also includes the judgment and sending instruction circuit parts, and the RRAM array is composed of RRAM memory cells and gate transistors. Planarization is achieved after fabrication.

[0072] [Step 2] After doping the silicon substrate B, a PN junction or Schottky barrier is formed, and the PN junction or Schottky barrier will be used to manufacture gate units in subsequent steps.

[0073][Step 3] Transfer the surface layer silicon with a PN junction or Schottky barrier on the surface of the silicon substrate B to the above-mentioned array obtained on the silicon substrate A by bonding, and remove the redundant silicon substrate (can be...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com