Method for reducing software load of system-on-chip (SoC)

A system-on-chip and software technology that is applied in the computer field to achieve strong versatility, reduce the number of interruptions, and solve the effect of increasing software load

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] The present invention will be further described below in conjunction with accompanying drawing:

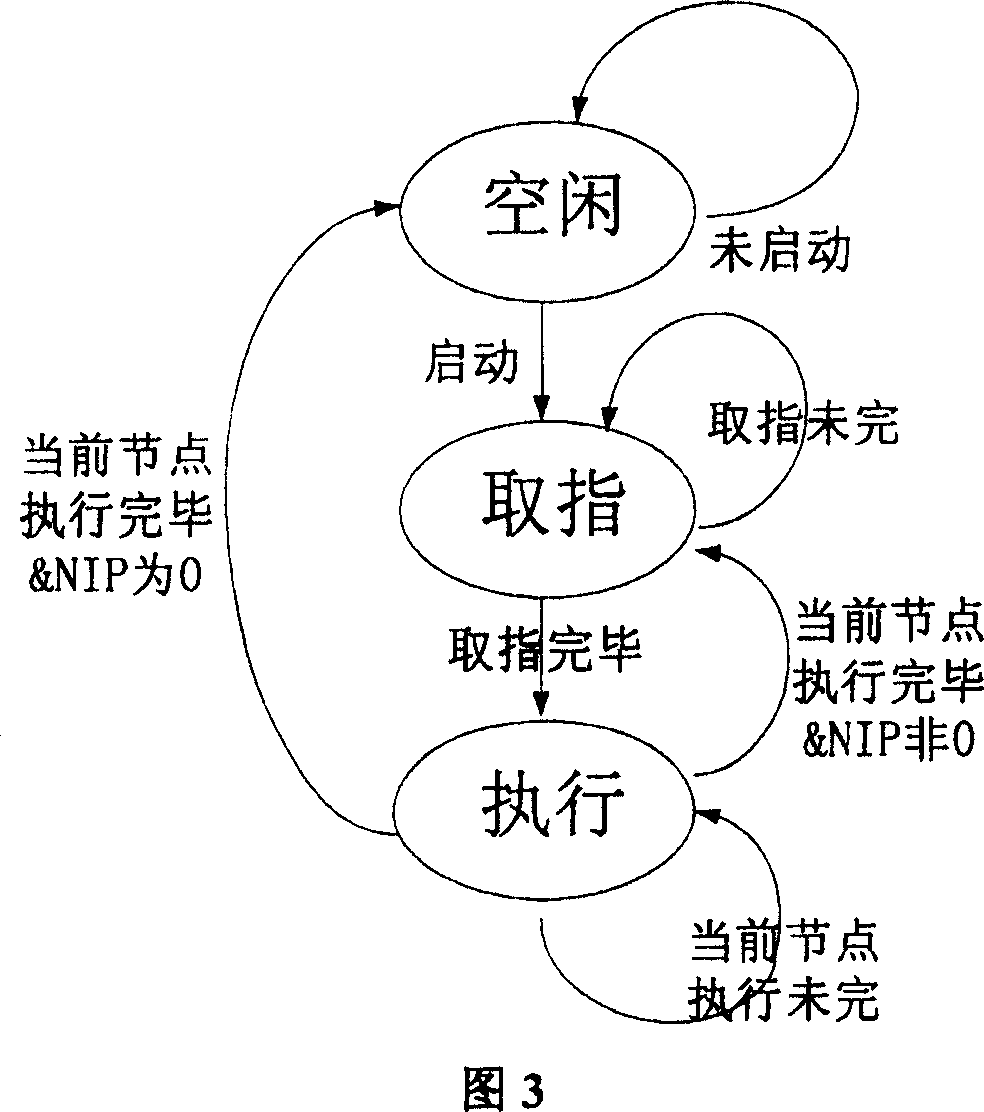

[0017] The present invention is accomplished jointly by software and hardware. The software is responsible for organizing the instructions into a linked list and controlling the startup and reset of the hardware.

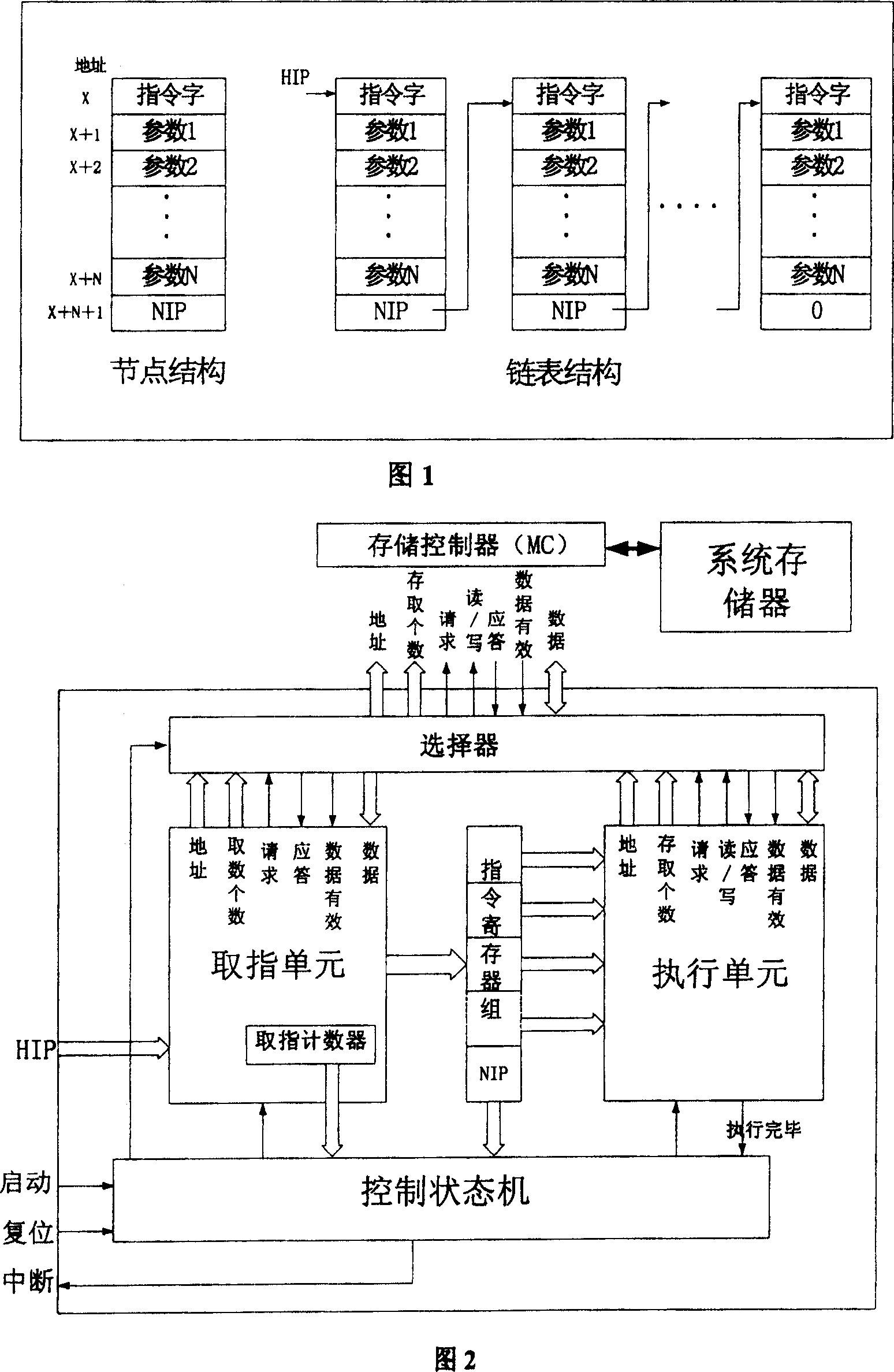

[0018] As shown in Figure 1, the instruction linked list is organized as follows: an instruction node is composed of an instruction word, all parameters and NIP (used to store the starting memory address of the next node), and they are stored continuously in the memory, assuming the address of the instruction word is X, and there are N parameters in total, then their addresses are X, X+1, X+2...X+N+1 in turn. The last NIP is a pointer to the next node, and it is agreed that if the value of this unit is 0, it means that this node is the last node of the linked list. One node corresponds to one operation, multiple nodes form an instruction linked list, and the NI...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More