Memory with two-stage read-out amplifier carrying extra load unit

A load unit and memory technology, applied in the field of memory, can solve the problems of transient time extension, long time, operating margin, and reading speed.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

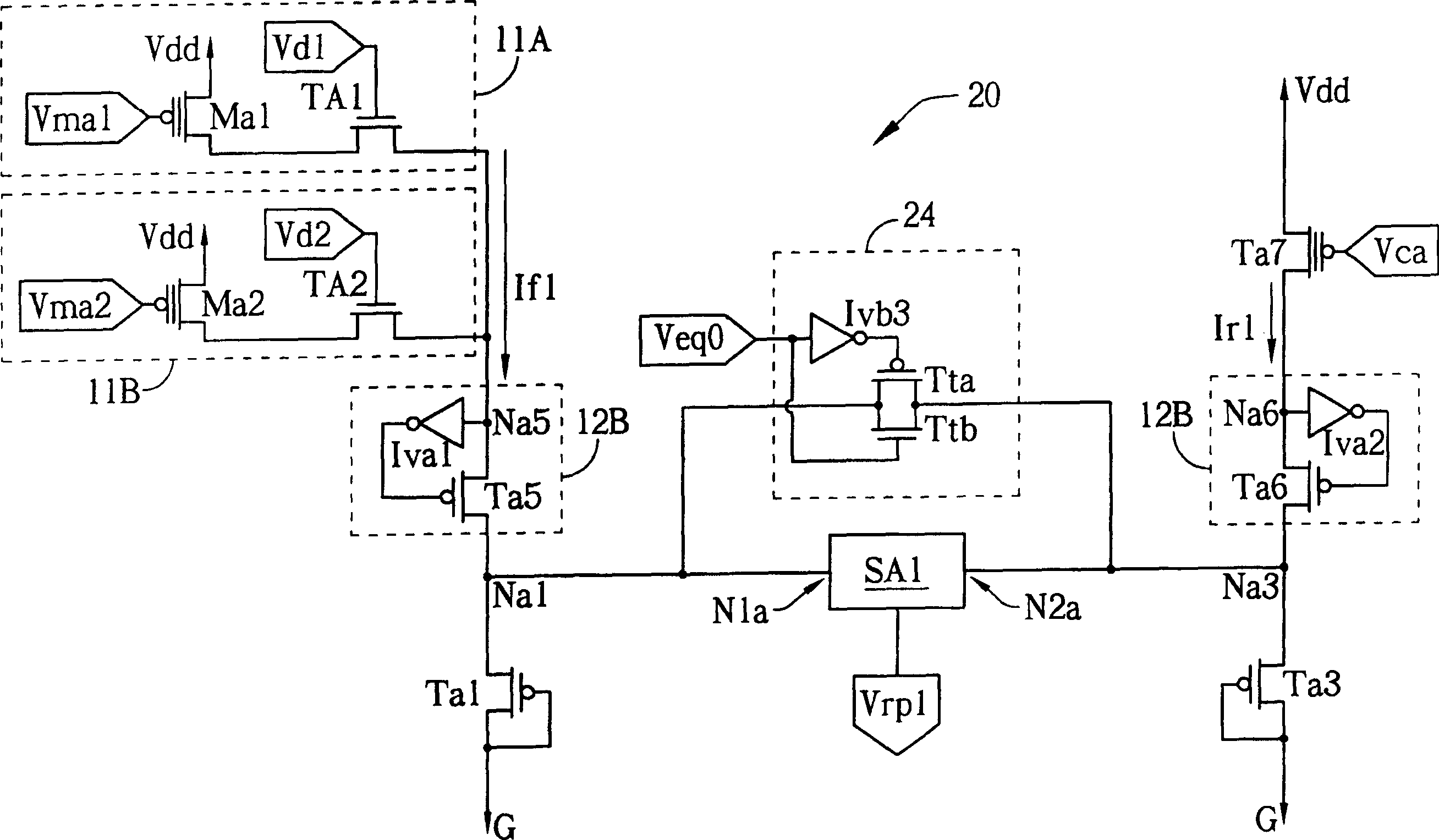

[0049] refer to Figure 5 . Figure 5 It is a schematic circuit diagram of the memory 30 in the present invention. The memory 30 is biased with a DC power supply Vdd, and is provided with a plurality of memory cells ( Figure 5Two memory cells 31A, 31B are depicted in the figure), load isolation cells 32A and 32B, metal oxide semiconductor transistor M1 as the first load cell, second load cell 36A, readout unit SA, equalization unit 34, The metal-oxide-semiconductor transistor M3 as the third load unit, the fourth load unit 36B, and the metal-oxide-semiconductor transistor M7 as a reference unit. The memory cells 31A and 31B use metal-oxide-semiconductor transistors Mm1 and Mm2 with floating gates to store data. The transistors MA1 and MA2 respectively control the data access of the memory cells 31A and 31B. The gates of the transistors Mm1 and Mm2 are respectively controlled by the control voltages Vm1 and Vm2 to bias voltages; the gates of the transistors MA1 and MA2 are ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More