Semiconductor device with high structure reliability and low parasitic capacitance

A semiconductor and device technology, applied in the field of semiconductor devices, can solve the problems of reducing mechanical strength, damaging the semiconductor area, and reducing the pass rate, so as to achieve the effect of easy alignment margin and avoiding crack damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

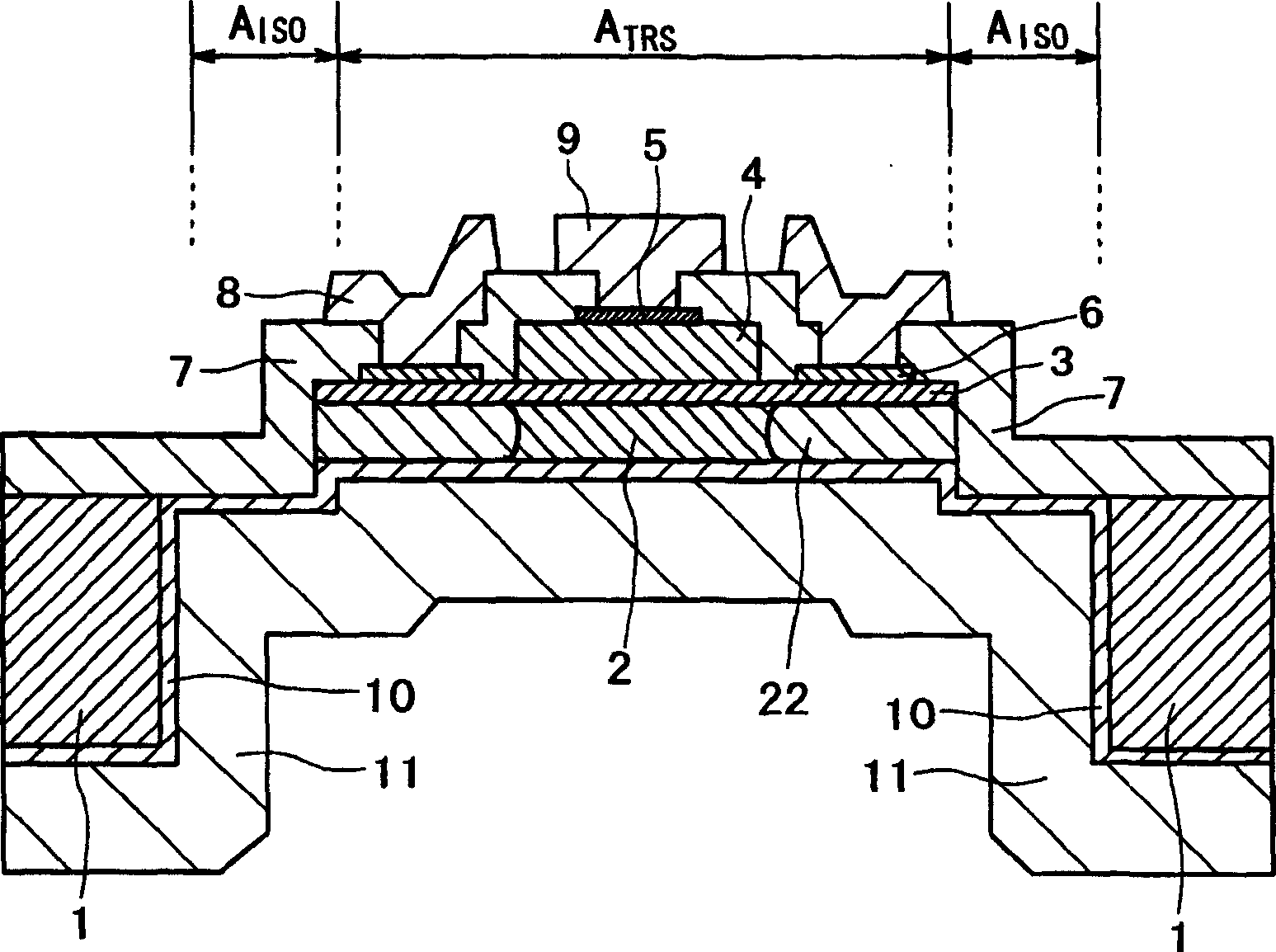

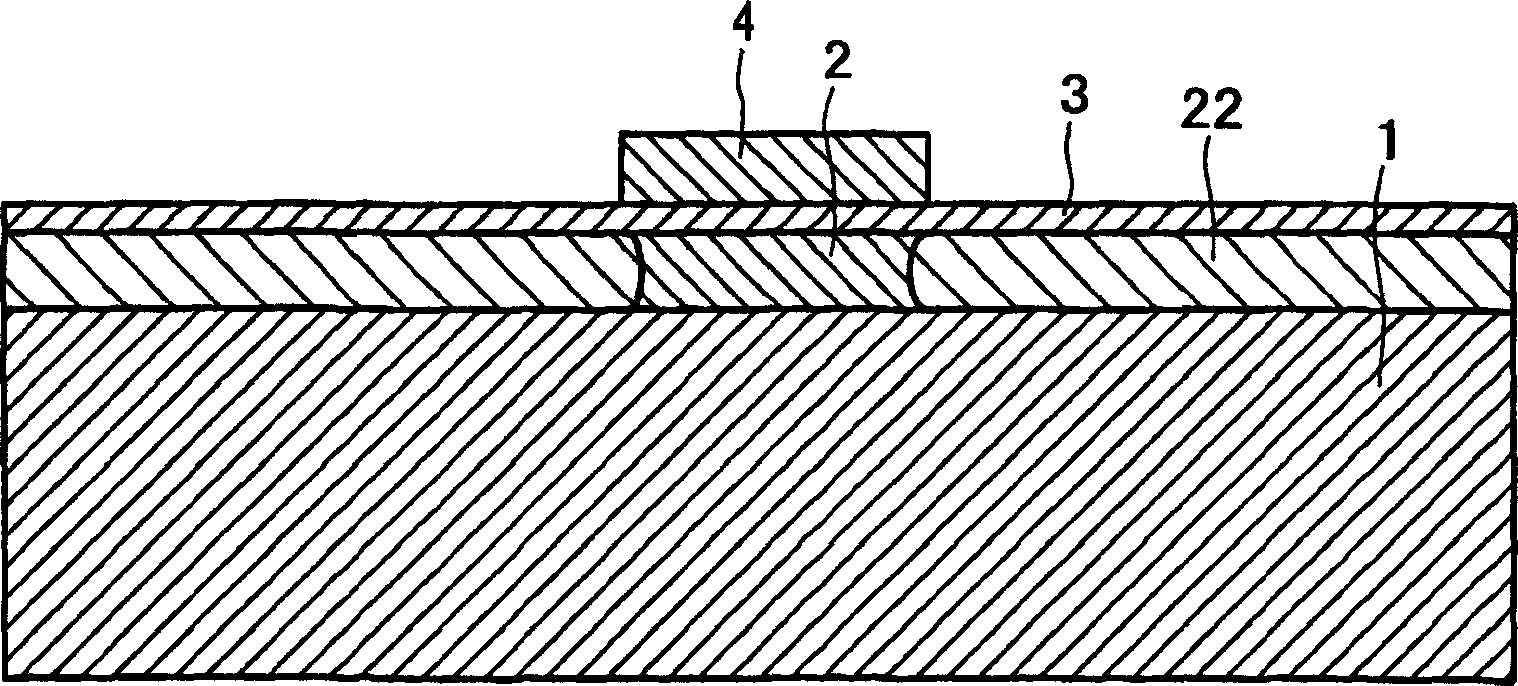

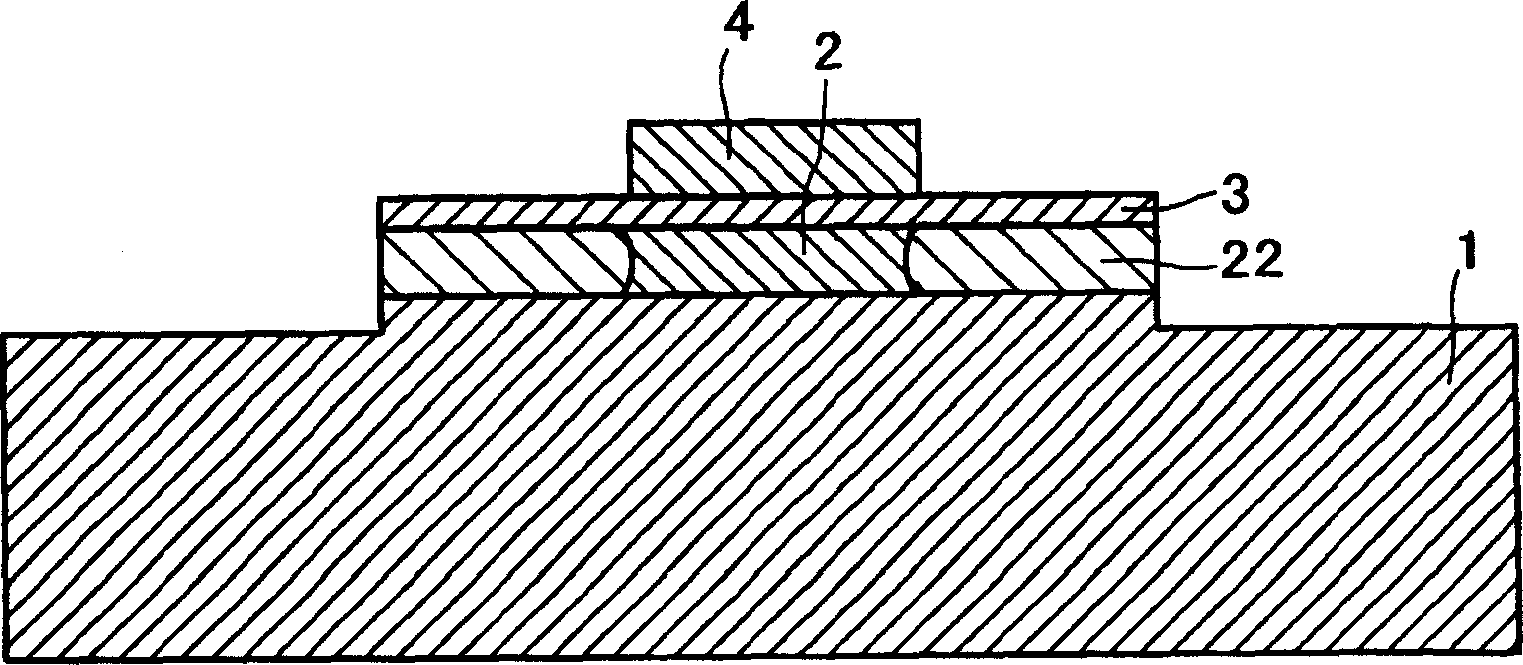

[0036] figure 1 An example of the semiconductor device according to the first embodiment of the present invention is shown. figure 1 The semi-insulating GaAs substrate 1, the emitter layer 2, the base layer 3, the collector layer 4, the collector electrode 5, the base electrode 6, the SiO 2 Surface protective insulating film 7, base wiring metal 8, collector wiring metal 9, emitter electrode 10, emitter wiring metal 11, and emitter damaged region 22 are formed on the entire back surface. figure 1 Medium, A TRS is the transistor region occupied by the emitter layer 2 . Transistor area A TRS A damaged area 22 is also included.

[0037] In this embodiment, the opening of the via from the back to the substrate 1 is larger than the transistor region A TRS , the emitter region 2 and the substrate 1 are isolated and connected by the surface protection insulating film 7 , the emitter electrode 10 and the emitter wiring metal 11 .

[0038] Below, refer to the attached Figure 2 ...

Embodiment 2

[0064] Figure 10 is a schematic cross-sectional structure diagram of a semiconductor device according to this embodiment. The difference from Embodiment 1 above is that during the crystal growth in step (1), an InGaP emitter contact layer 30 is provided between the GaAs substrate 1 and the emitter layer 2, and this layer is doped until the electron concentration reaches 5 ×10 18 cm -3 , a GaAs collector contact layer 20 is provided on the collector layer 4, which is doped until the electron concentration also reaches 5×10 18 cm -3 . The process of manufacturing a transistor was performed in the same manner as in Example 1.

[0065] Due to the provision of highly doped contact layers 20 and 30, the emitter and collector resistances are reduced, i.e. for a collector size of 2×20 μm 2 For the device, the collector resistance is reduced from 10Ω to 2.5Ω, and the emitter resistance is reduced from 20Ω to 4Ω. Thus, the cut-off frequency of the device is increased to 20GHz-30...

Embodiment 3

[0067] FIG. 11 shows a schematic cross-sectional structure of the semiconductor device of this embodiment. It differs from Embodiment 1 above in that the emitter layer 2, the base layer 3, and the collector layer 4 are arranged in the reverse order so that the emitter is on the upper side during the crystal growth in step (1). That is, an upper emitter type transistor is formed. The process of manufacturing a transistor was performed in the same manner as in Example 1.

[0068] Due to the upper emitter type, only the emitter mesa area A E The part directly below forms the active region of the transistor, so there is no need to increase the resistance of the passive region through ion implantation, which can simplify the process. Moreover, since the collector electrode 5 that directly contributes to heat dissipation and the collector wiring 9 of the metal layer are in contact with the collector that causes power dissipation in the transistor with a large area, the thermal res...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More