Method for forming self-alignment metal silicide

A metal silicide, metal layer technology, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., to solve problems such as short circuits, conductive impurities, and component failures

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

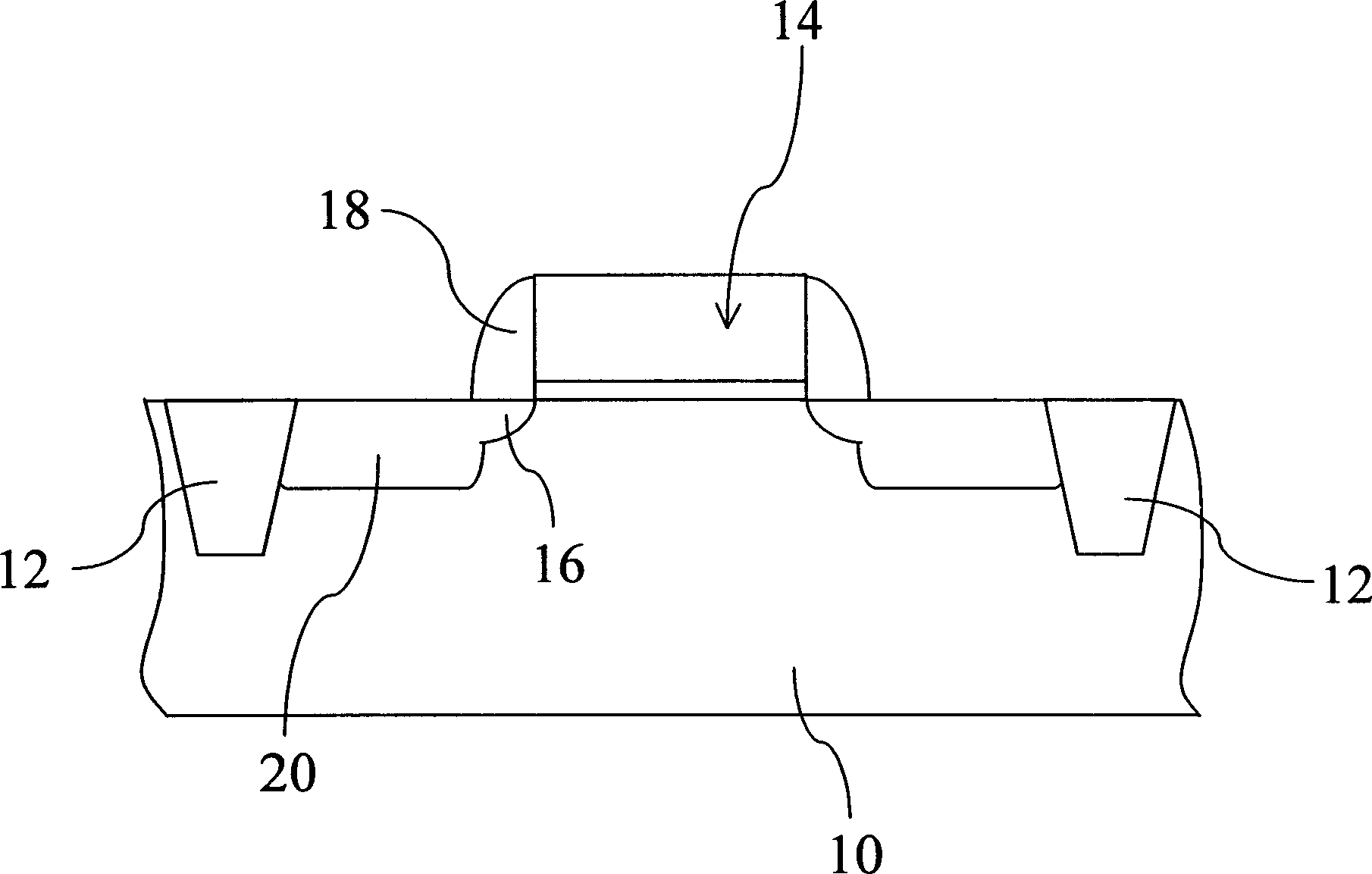

[0012] In the conventional manufacturing process of self-aligned metal silicide, it is very easy to cause conductive non-deposits on the sidewall of the gate spacer between the gate structure and the source / drain region, which will cause a short circuit. lead to component failure, and the method proposed by the present invention can effectively overcome these deficiencies in the prior art.

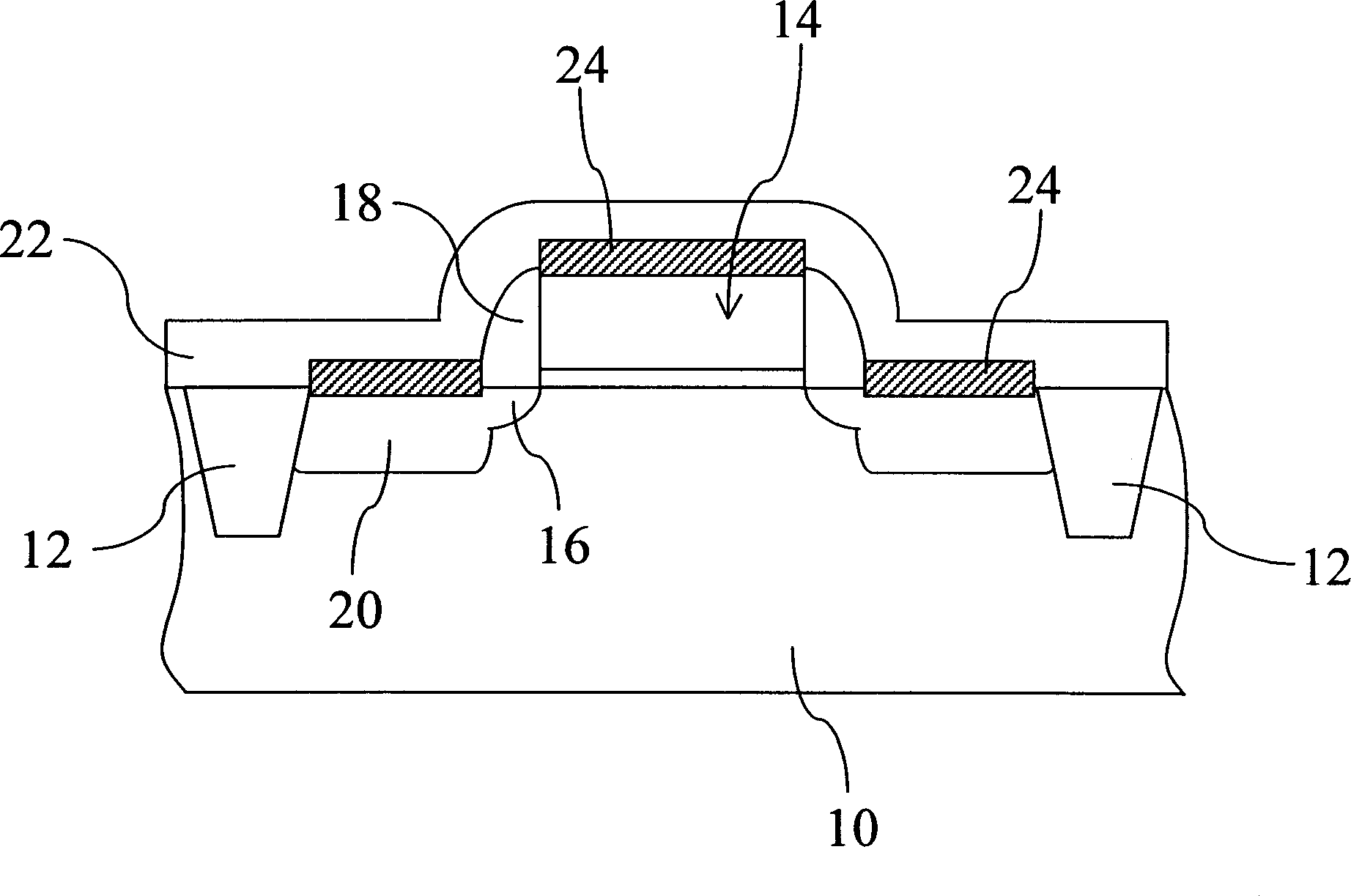

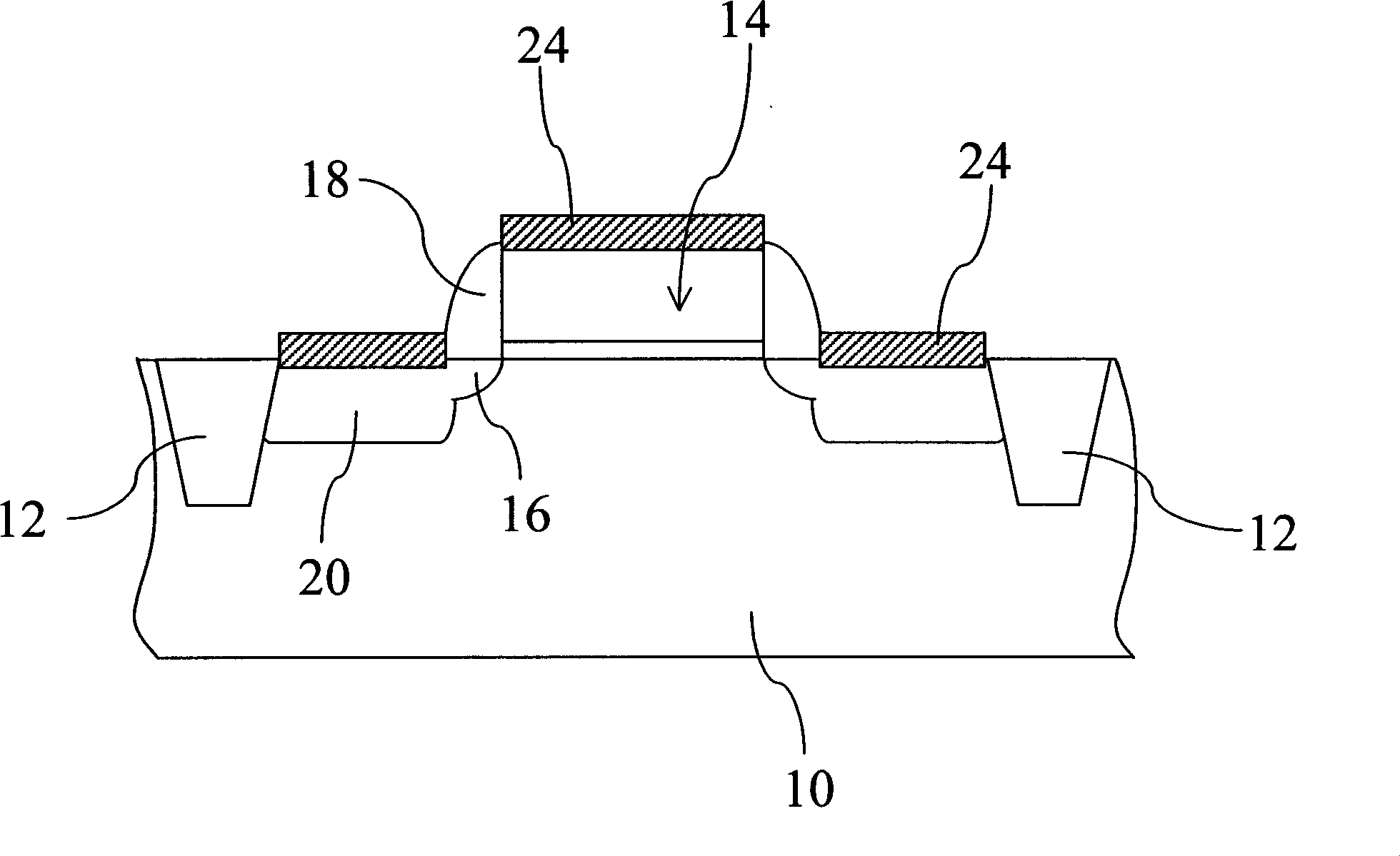

[0013] 2( a ) to FIG. 2( d ) are cross-sectional views of each step in the fabrication of self-aligned metal silicide in a preferred embodiment of the present invention. First, as shown in FIG. 2( a), a shallow trench isolation region (shallow trench isolation, STI) 32 is first formed in a semiconductor substrate 30 to isolate active components and passive components in the semiconductor substrate 30; A transistor gate structure 34 is formed on the surface of the substrate 30, which is composed of a gate oxide layer 342 and a polysilicon layer 344 thereon; and then the semiconductor substr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More