Delay locking loop having acceleration mode and controlled by register

A technology of delay-locked loop and acceleration mode, which is applied in the direction of automatic power control, static memory, digital memory information, etc., and can solve the problems of reducing accuracy and complex execution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

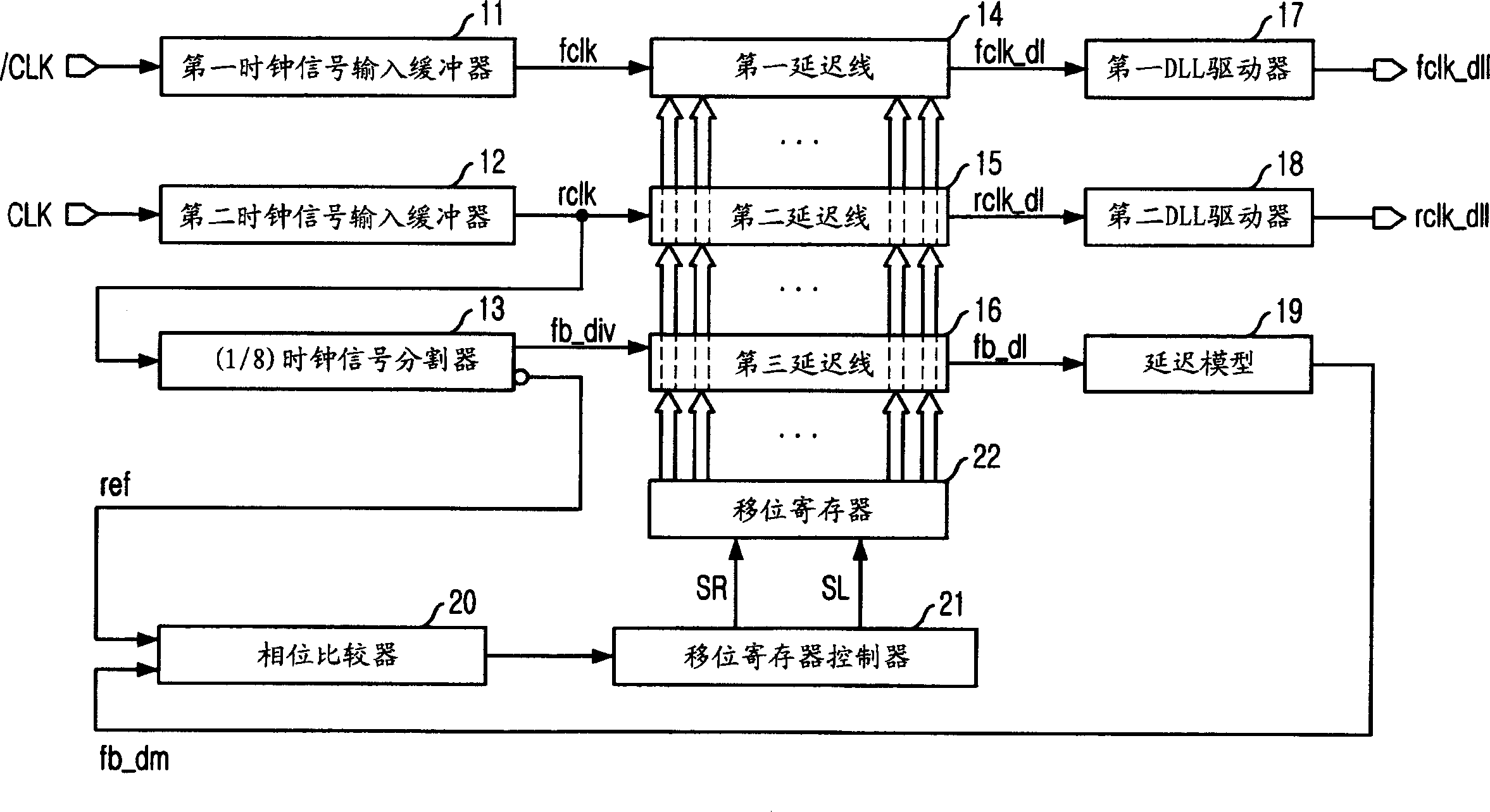

Embodiment Construction

[0036] The present invention relates to a method for controlling an acceleration mode using a technique that does not use two clock signals supplied to a phase comparator and compares them with each other by using the phase comparator.

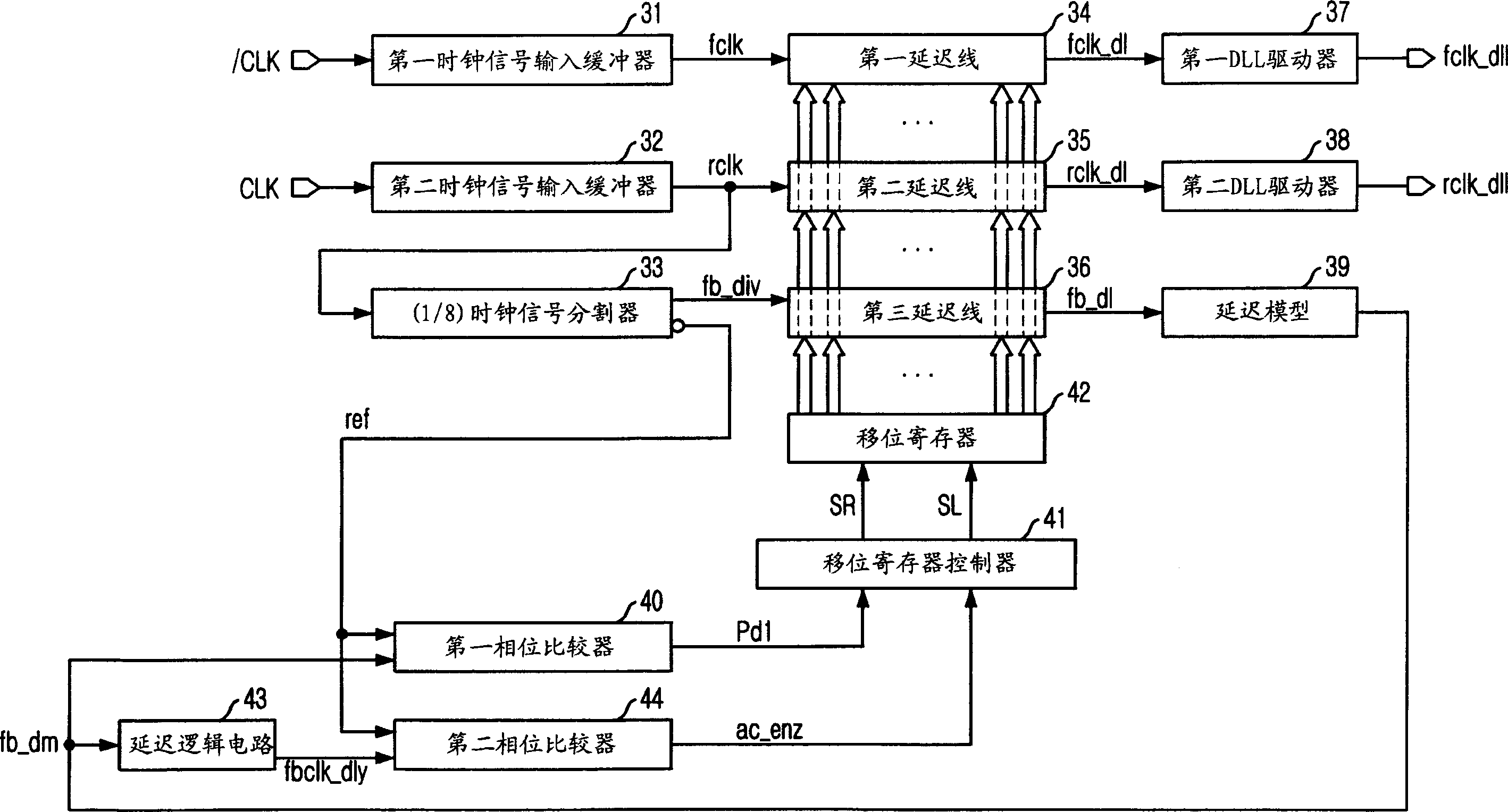

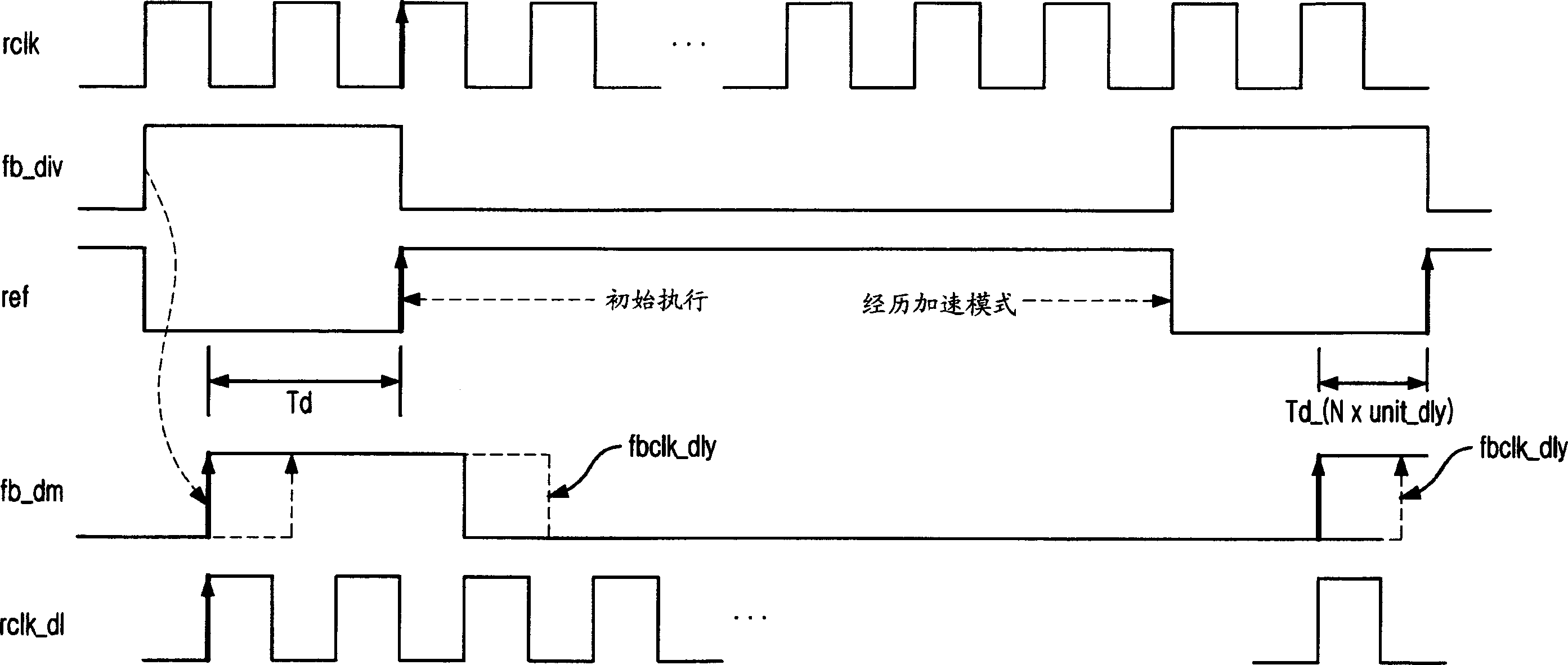

[0037] The present invention uses an input clock signal without delay as the clock signal source. A first phase comparator compares the undelayed input clock signal to the output from the delay model, and a second phase comparator compares the undelayed input clock signal to the clock signal output from the delay logic circuit. The outputs of the first and second phase comparators determine whether the overdrive mode is implemented on the mode decision logic. What is important is that by doing this in the speedup mode, N delay element units jump and shift in the shift register immediately, and the shifted delay value must be the same as the delay value N×unit_delay of the delay logic circuit.

[0038] Hereinafter, a semiconductor memory devic...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More