Method for handling electroplating lead layout of IC packaging base plate and electroplating lead structure

A technology of electroplating lead wires and packaging substrates, which is applied in the direction of circuits, electrical components, and electrical solid devices, which can solve problems such as signal loss, increase the difficulty of wiring, and interference, so as to ensure the improvement of signal and electrical performance and reduce the wiring area. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

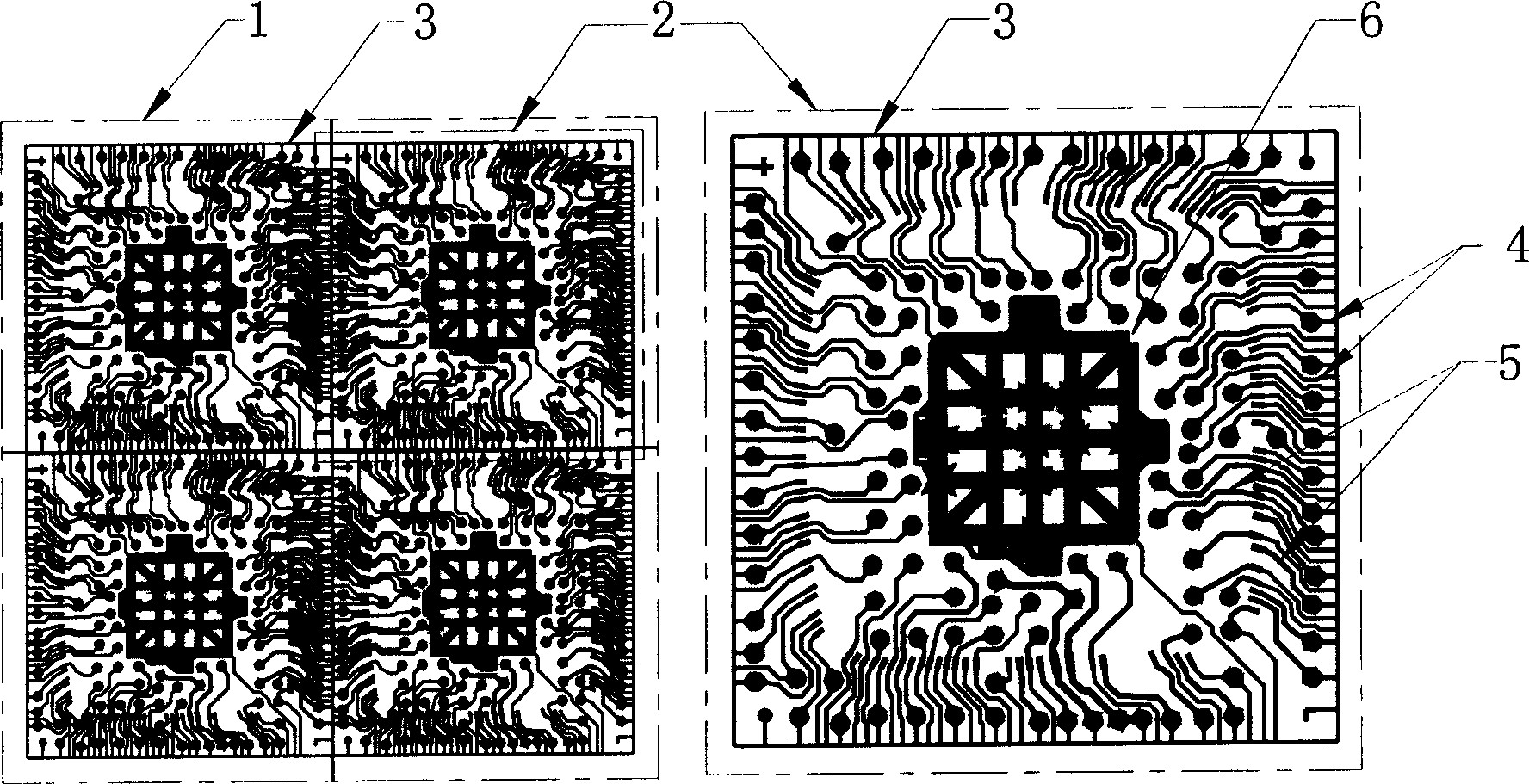

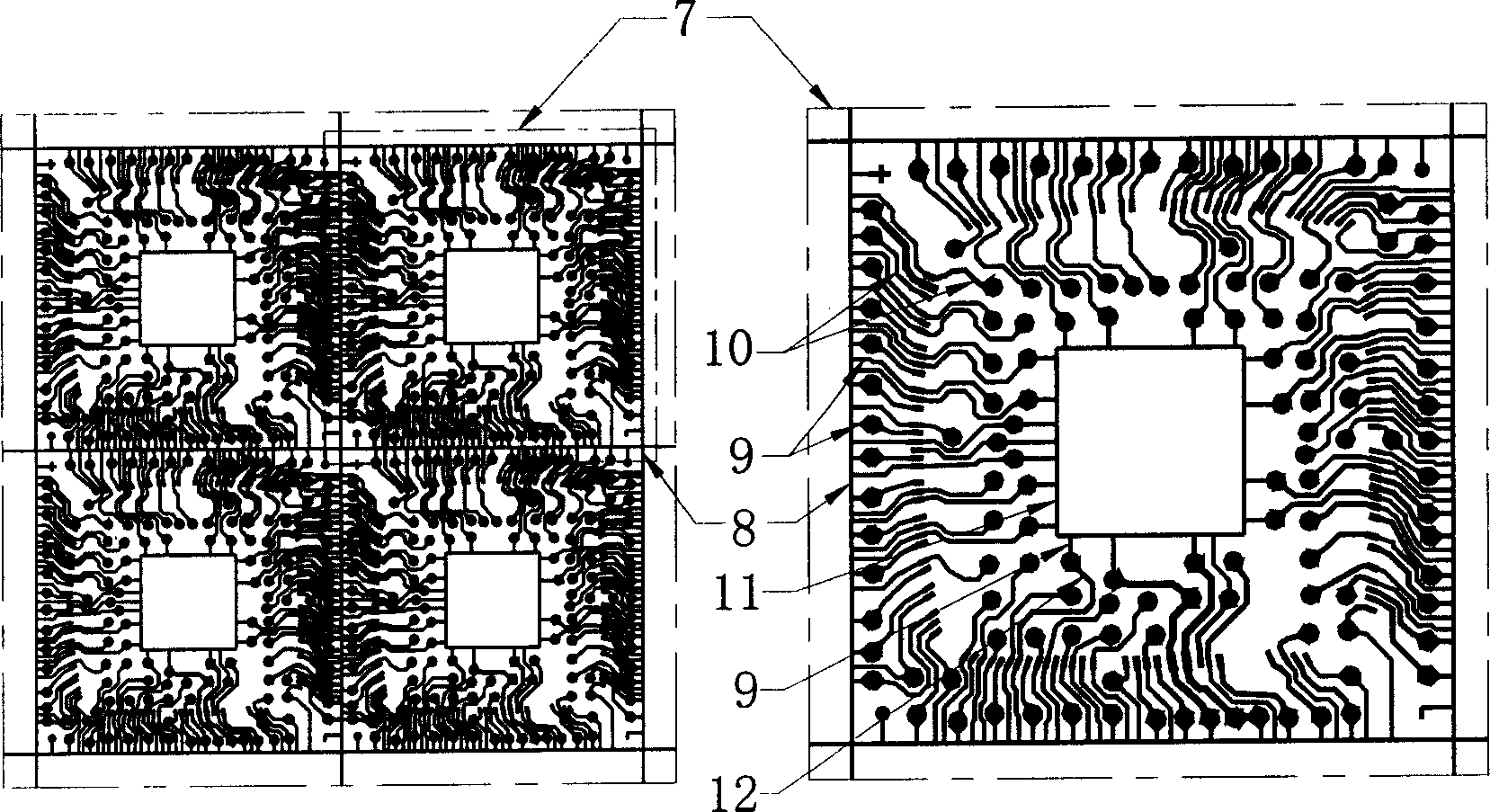

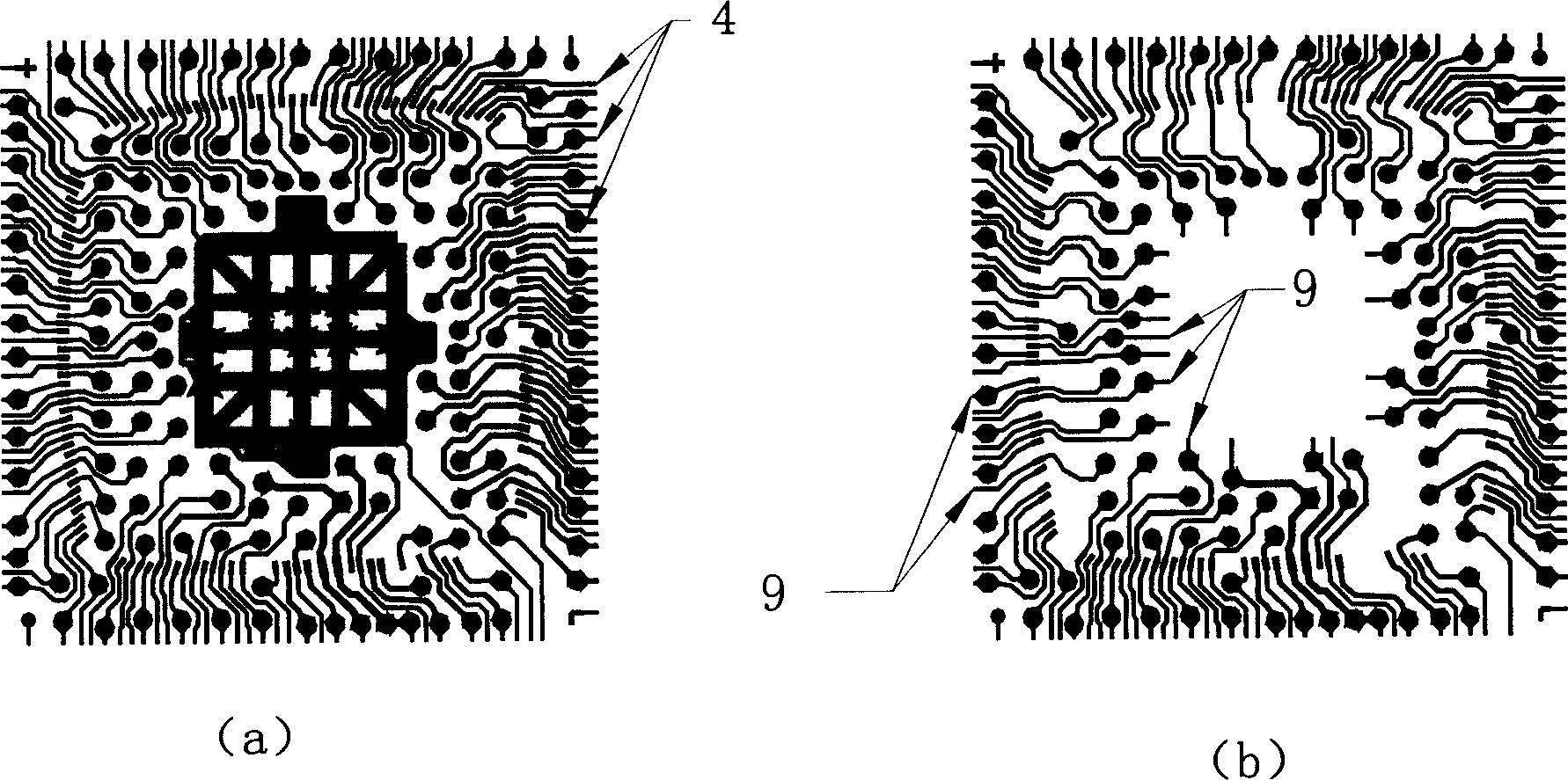

[0029] Further description below in conjunction with accompanying drawings.

[0030] Figure 4 It is a schematic diagram of the circuit structure of the packaging substrate unit applying the present invention, Figure 5 yes Figure 4 A partial enlarged view of the electroplating lead in the packaging substrate unit, a partial enlarged view of the connection between the electroplating lead and the metallized micro-via hole, and a cross-sectional view of the metallized via hole. The electroplating lead structure in the schematic integrated circuit package substrate unit includes the IC package substrate unit (13), and the electroplating lead (15) is set between the wire patterns (14) in the package substrate unit (13), and the wire pattern (14) Each wire is connected to the electroplating lead (15) nearby, and the electroplating lead (15) passes through the metallized micro-via hole (16) and passes through the insulating medium layer (17) to communicate with the metal power su...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com