Method for testing a circuit which is under test, and circuit configuration for carrying out the method

A circuit unit and circuit structure technology, applied in the direction of measuring electricity, measuring electrical variables, digital circuit testing, etc., can solve the problems of not allowing parallel testing, increasing the cost of the circuit unit to be tested and the overall cost of testing, etc., to save terminal units , reduce test cost, increase the effect of parallelism

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

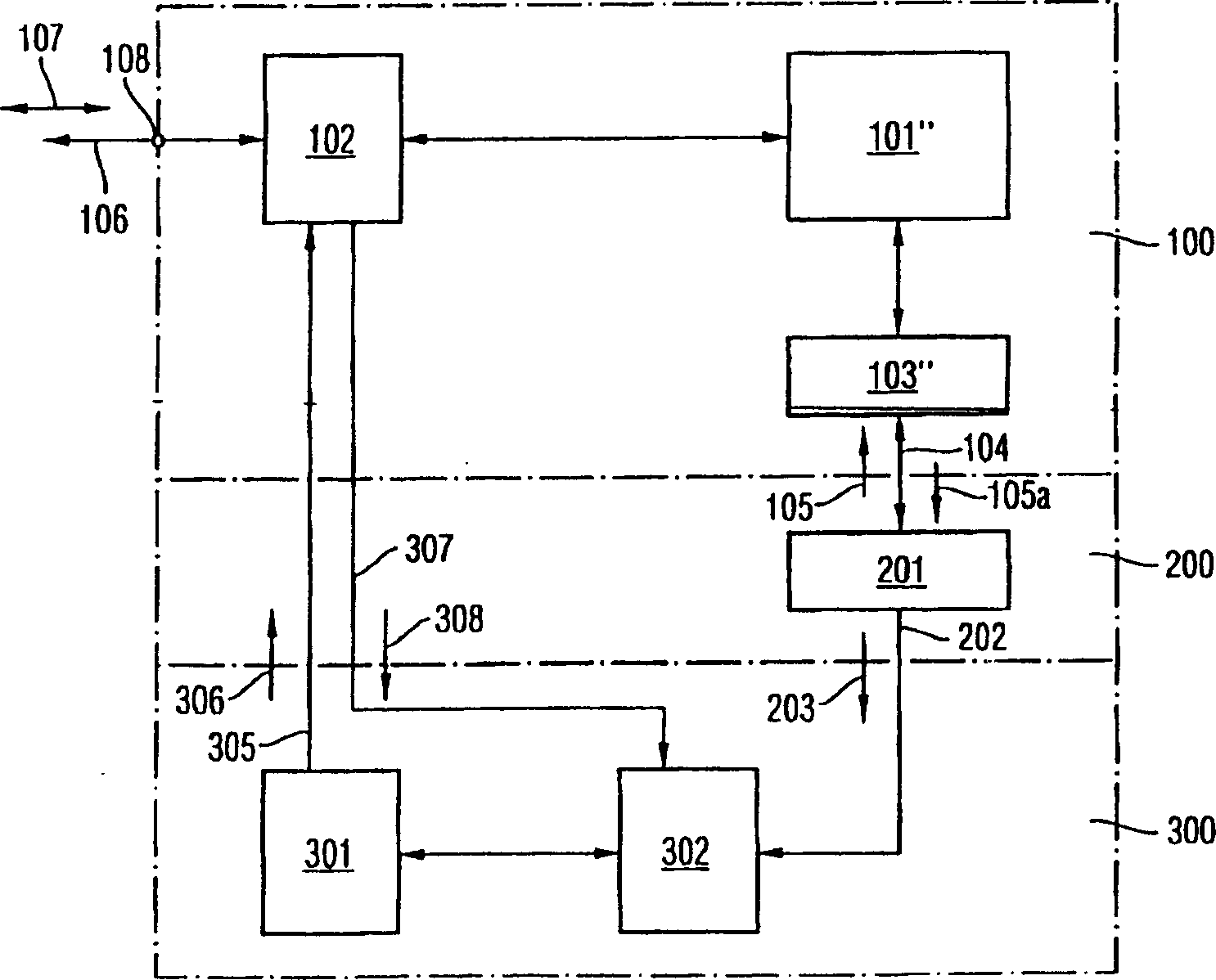

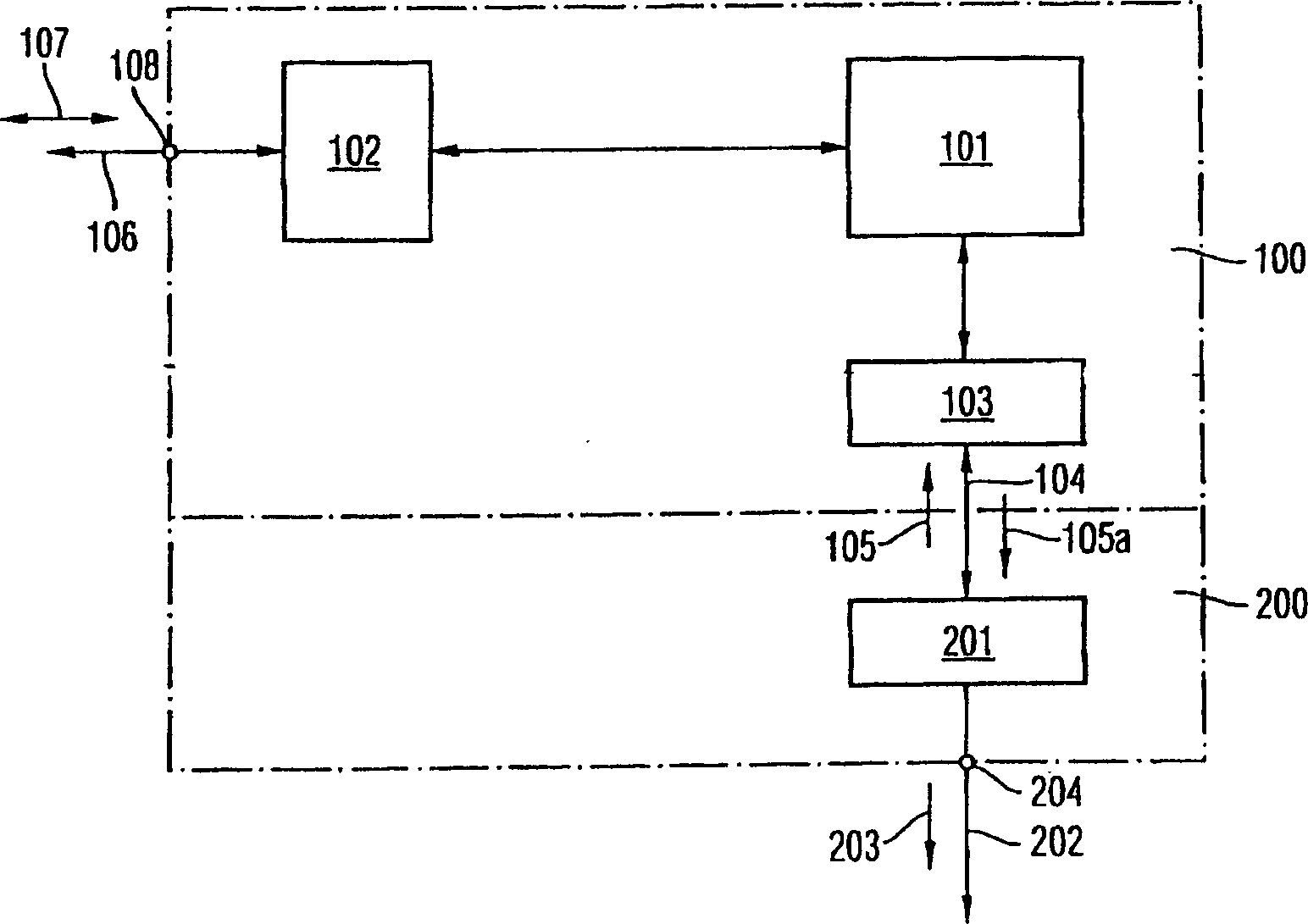

[0041] figure 1 The circuit structure shown includes three basic modules, namely, a circuit unit under test 100 , a testing device 200 and a combinational logic device 300 . It should be noted that the circuit unit 100 under test, the testing device 200 and the combinational logic device 300 in the following exemplary embodiments are arranged on a single circuit chip to form a single circuit unit.

[0042] That is to say, the circuit unit 100 under test is extended by the test device 200 and the combinational logic device 300, and only one addressing and control terminal unit 108 is required as an external connection.

[0043] It should be noted that although it is shown that the circuit unit under test 100, the testing device 200 and the combinational logic device 300 are arranged on a single chip, the circuit unit under test 100, the testing device 200 and the combinational logic device 300 may also be designed It is a discrete circuit unit.

[0044] The circuit unit 100 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More