Junction field effect transistor

A field effect transistor and junction gate technology, applied in the field of microelectronic semiconductors, can solve the problems of high driving current electrical characteristics, low leakage current, etc., and achieve the effects of good heat dissipation efficiency, cost saving, and suitable for large-scale integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

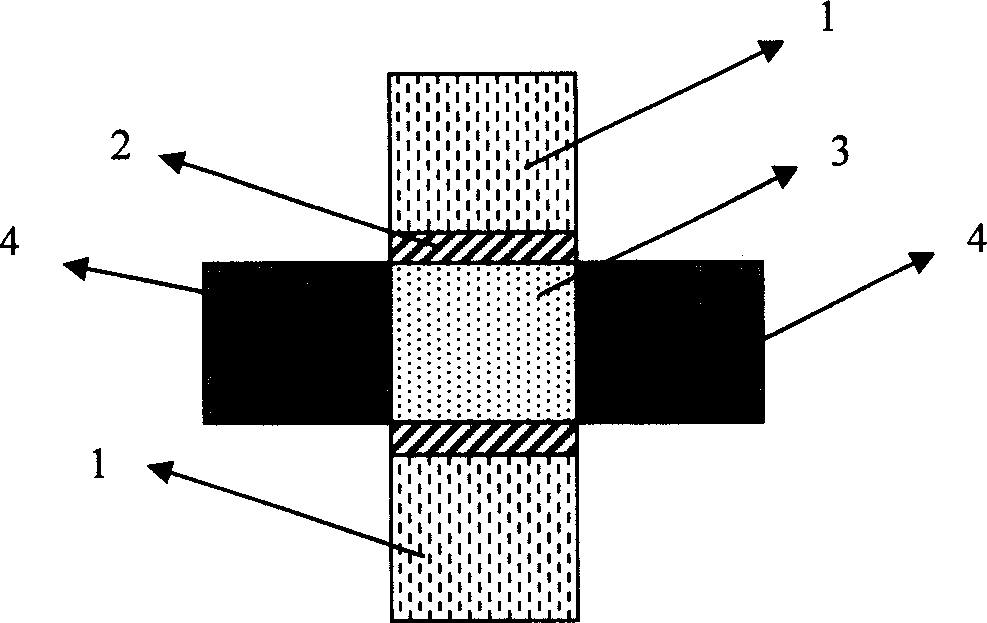

[0019] Specific implementation examples

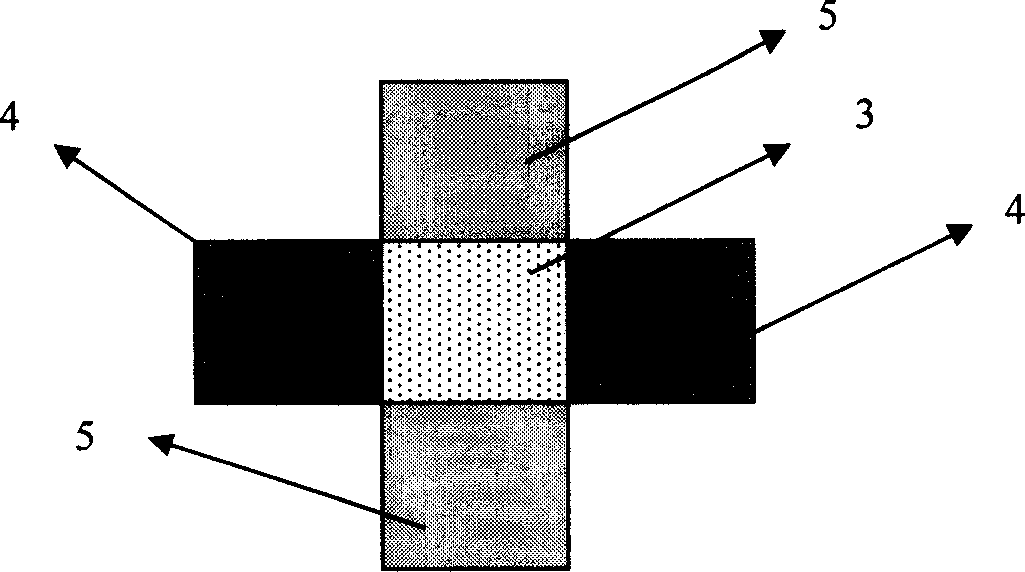

[0020] refer to figure 2 , the dual gate junction gate field effect transistor of the present invention comprises: source region 4, drain region 4, double control gate 5 and body 3, body 3 is square, control gate 5 is doped monocrystalline silicon, control gate and body are directly connected Form a P-N junction, the body is a square. It can be seen from the figure that the dual-gate junction gate field effect transistor of the present invention is a completely symmetrical structure, so as long as the connecting electrodes between the control gate and the source and drain are changed, the n-type double gate junction gate field effect transistor and the p-type double gate field effect transistor.

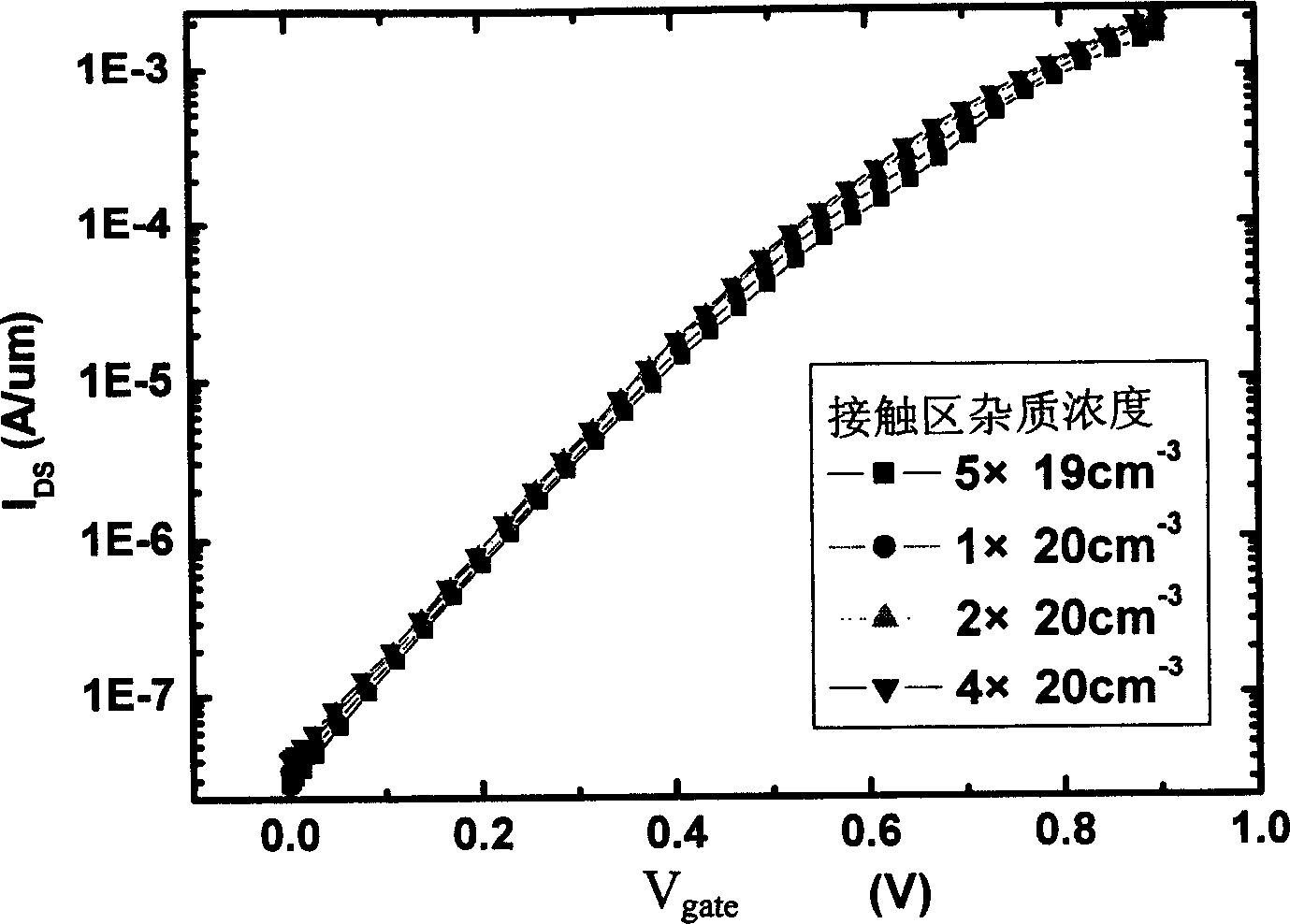

[0021] The specific implementation example of the double-gate junction gate field effect transistor of the present invention, taking the side length of the body as an example, its specific design structural parameters are as follows: the l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com