Electronic circuit, system, nonvolatile memory and operating method thereof

A volatile memory and electronic circuit technology, applied in the field of semiconductor storage elements, can solve problems such as hindering process reduction in size and cost, low program efficiency, high operating voltage, etc., to achieve reduced programming and erase distribution, increased efficiency, The effect of accuracy optimization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] Table 1

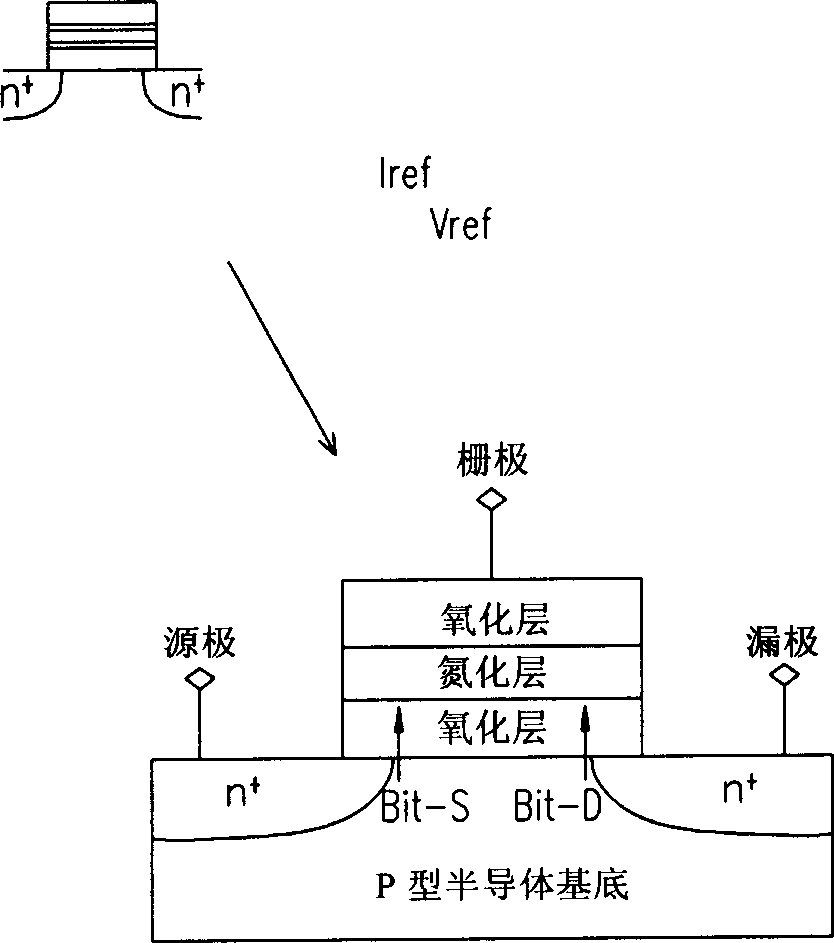

[0051] exist figure 1 As in Table 1, when the first bit (bit D) is erased, electrons are injected into the gate of the non-volatile memory 10 programmed by hot hole injection nitride electron storage. Likewise, electrons are injected at the gate of the non-volatile memory when the second bit (bit S) is erased. And when the first bit (bit D) is programmed, holes are injected at the drain of the non-volatile memory, or electrons are reduced at the drain side. When programming the second bit (bit S), holes are injected at the source of the non-volatile memory, or electrons are dropped on the source side.

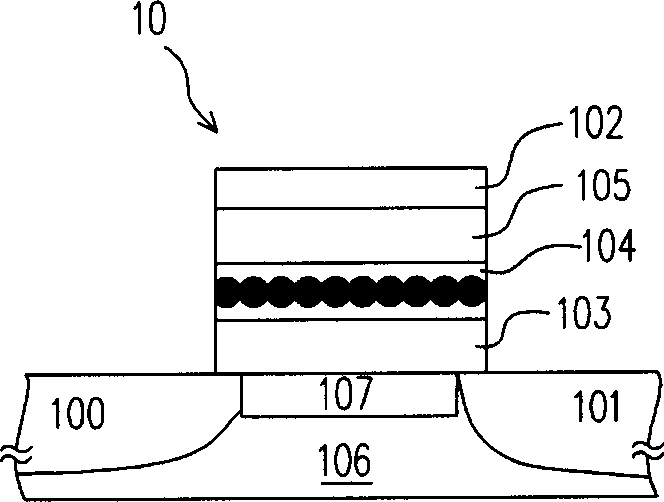

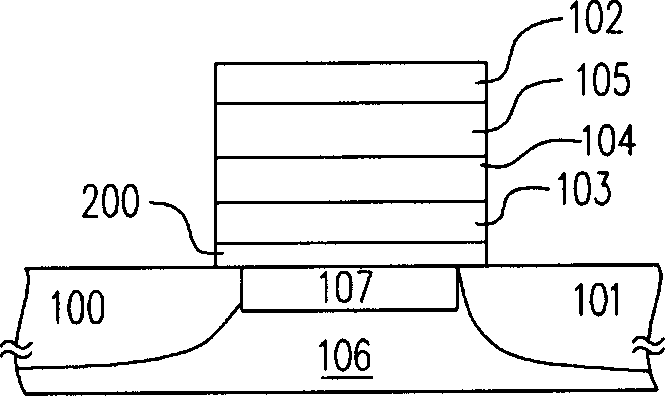

[0052] The trapping layer in at least one bit of the non-volatile memory is operable to retain electrons in an erased state, enabling the non-volatile memory to have a threshold voltage and a read current during a read operation. In addition, the comparator is used to receive the first input information generated by the read curren...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More