Crystal-covering package method and structure for covering crystal

A technology of flip-chip packaging and flip-chip, which is applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., and can solve problems such as limiting the application range of flip-chip packaging, high cost, and complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] In order to have a more in-depth understanding and recognition of the features, purposes, and effects of the present invention, the preferred embodiments are listed as follows with accompanying drawings:

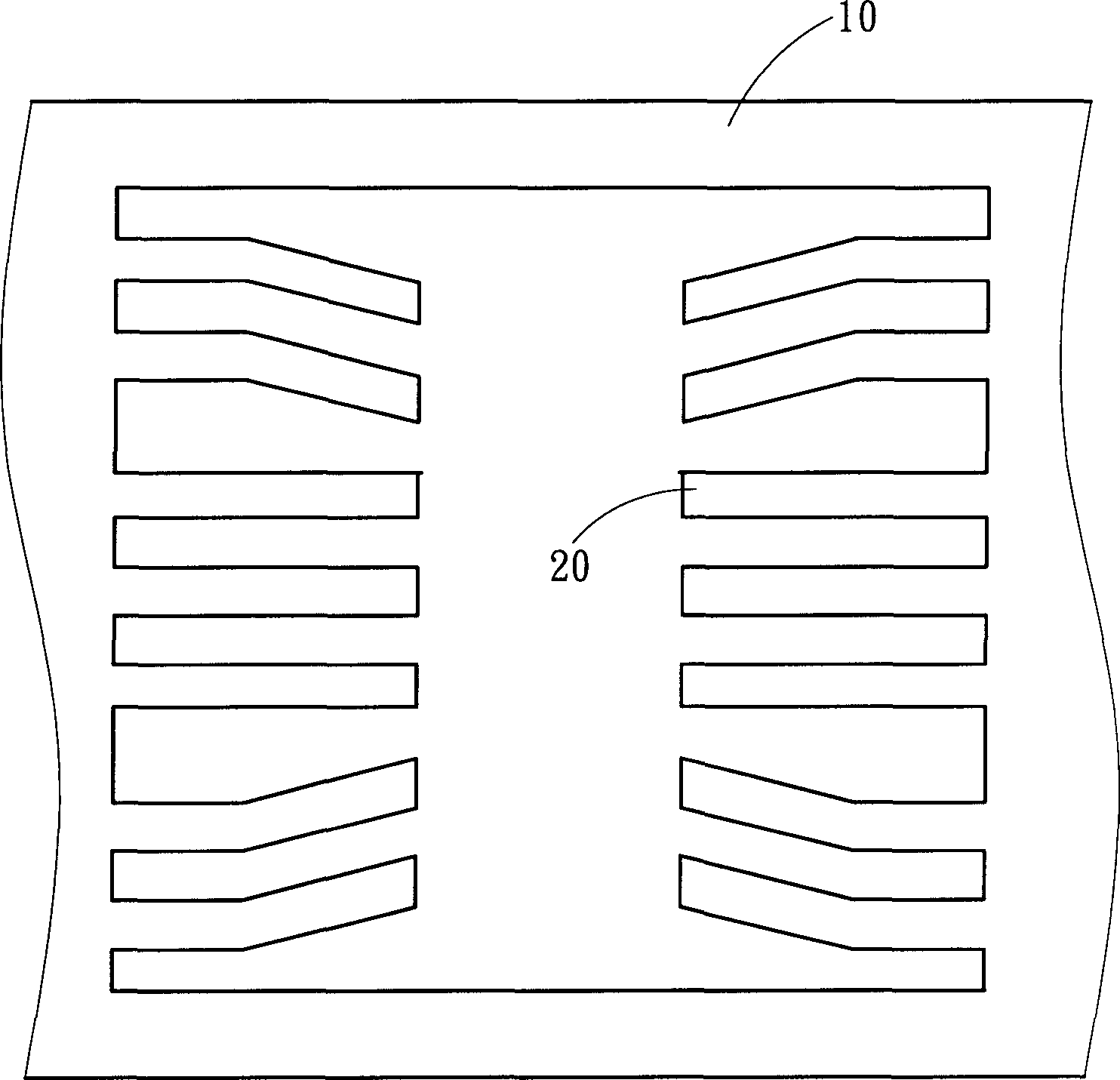

[0018] See figure 1 , Is a lead frame 10 made by etching, which has a plurality of flip-chip regions 20, which are used to connect with the die pads 70 of the wafer 80 (see Figure 5 ).

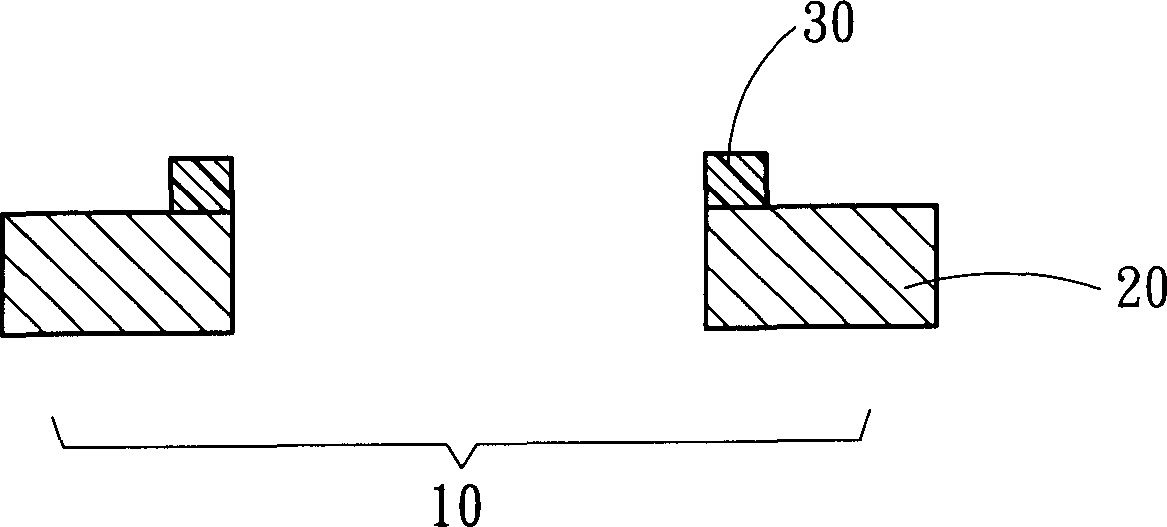

[0019] See picture 2-1 , Figure 2-2 , Figure 2-3 ,versus Figure 2-4 , Is a schematic diagram of the half-etching process, a lead frame 10 with multiple flip-chip regions 20, such as picture 2-1 Shown; use the method of exposure and development to form a photoresist layer 30 on a specific area of the flip chip area 20, such as Figure 2-2 As shown; using the etching solution again, the flip chip area 20 has not covered the photoresist layer 30 area contact with the etching solution for etching, and the etching time is controlled, so that the flip chip area 20 is formed with flip c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More