Method and device for measuring time interval through delay line in cascaded two stages

A time interval and time measurement technology, applied in the field of optical disc readout signal analysis and detection, can solve the problems of high cost, complex design process, long design and processing cycle, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

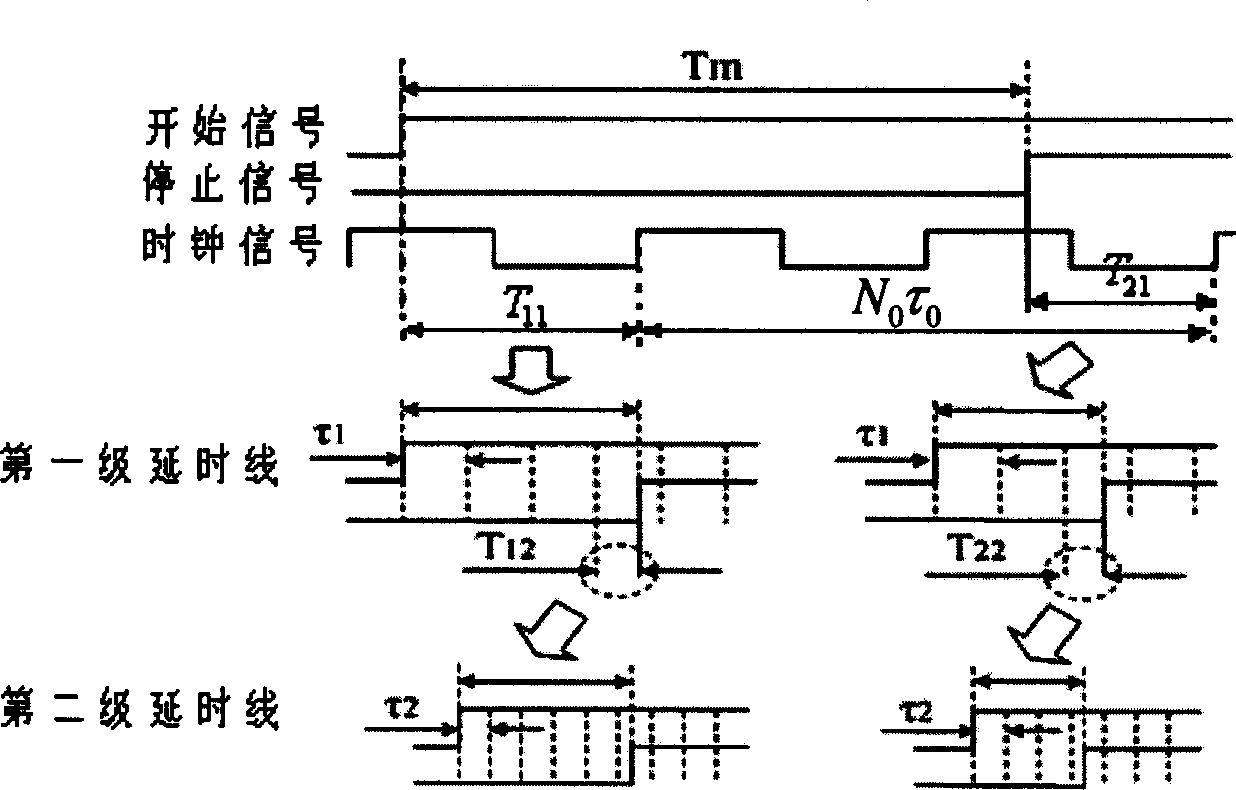

[0051] Figure 5 The device circuit shown as the two-stage cascaded delay line method is realized in an XC2V80-6-fg256 chip, which is a Virtex II series FPGA chip of Xilinx Company. The basic clock operating frequency of the system is 200MHz, and it is used as the counting clock signal of the 18-bit binary counter. Resolution τ of the first stage delay line 1 About 800 picoseconds. Since the logic unit delay or path delay that can be obtained in the FPGA chip is basically hundreds of picoseconds, if you want to obtain a resolution below 100ps, the second-level delay line can no longer be designed according to the first-level delay line method . The design method adopted in the present invention makes the resolution τ of the second stage delay line 2 The resolution is 75ps, which breaks through the limitation of circuit physical delay and obtains higher resolution. In order to ensure that the measurements do not interfere with each other and measure continuously, before ea...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More