Method and apparatus employing integrated metrology for improved dielectric etch efficiency

A technology of equipment and measurement values, applied in semiconductor/solid state device testing/measurement, circuits, electrical components, etc., to solve the problem of inability to monitor wafer etching uniformity by interferometric sensors, interferometric sensors that cannot be monitored or corrected, and improper chip etching And other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

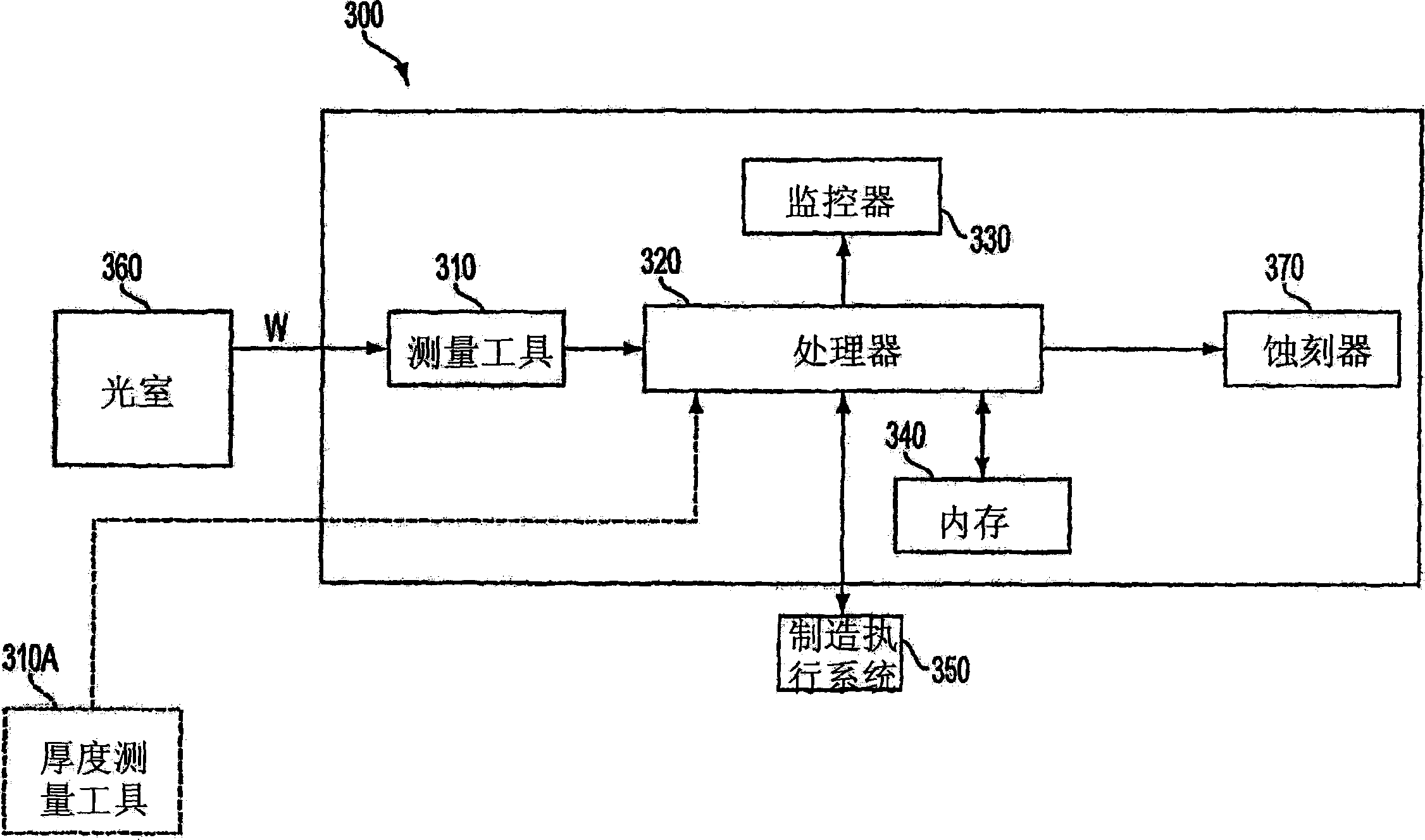

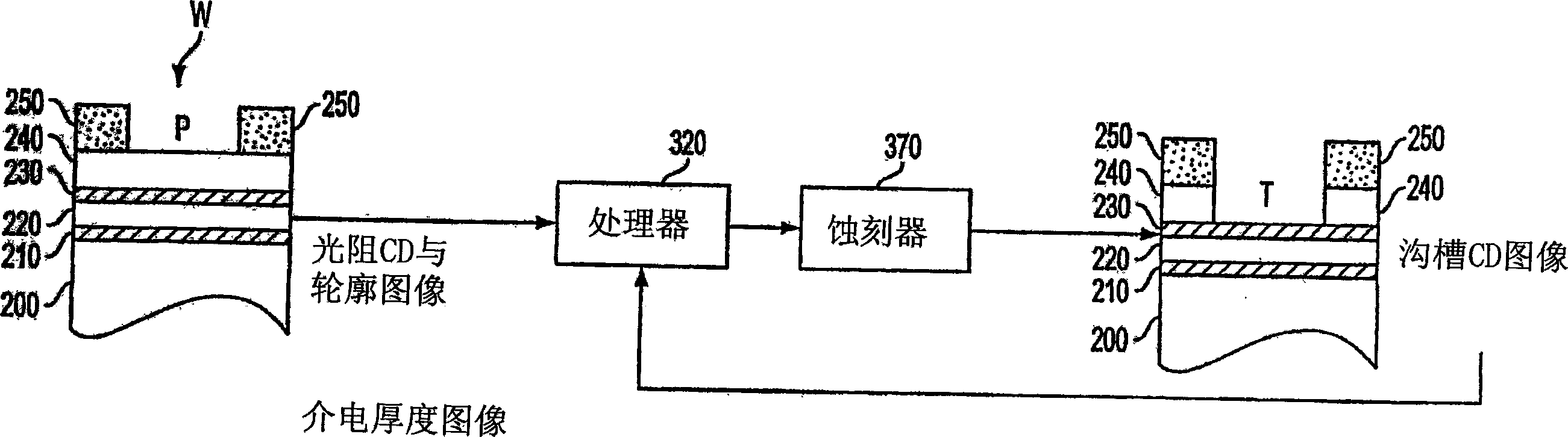

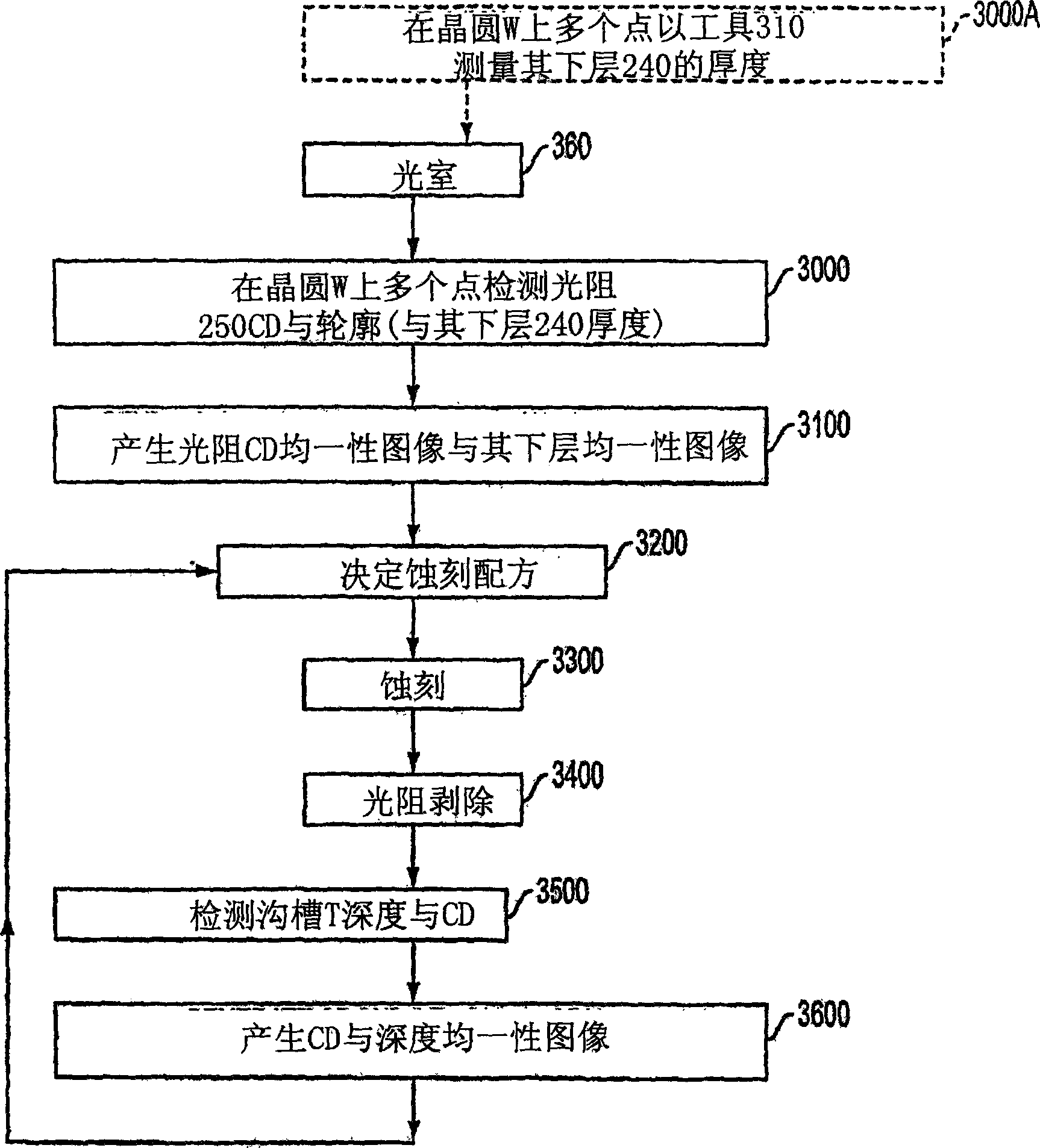

[0040] The traditional measurement method for detecting the features formed on the surface of the semiconductor wafer during the manufacturing process cannot effectively analyze the error between the CD and / or the outline and the design rules, so as to provide early information for positively identifying the source of the defect, or to carry out the process control to reduce size variation. The present invention solves the CD control problem by reducing the CD variation by feeding back information about the CD and profile of the photoresist mask, and measuring the thickness of the underlying layer at multiple points on the wafer to adjust the next process of the inspected wafer ( such as etching process). In some embodiments of the present invention, CD, profile and thickness measurement, etch processing and post-etch cleaning are performed in a single module in a controlled environment, thereby increasing throughput and improving yield. The present invention provides a self-...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More