Test switching circuit for a high speed data interface

A high-speed data interface and switching circuit technology, applied in the direction of digital circuit testing, data exchange network, measuring electricity, etc., can solve the problems of increasing test costs, undetectable, programmable terminal resistance level errors, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

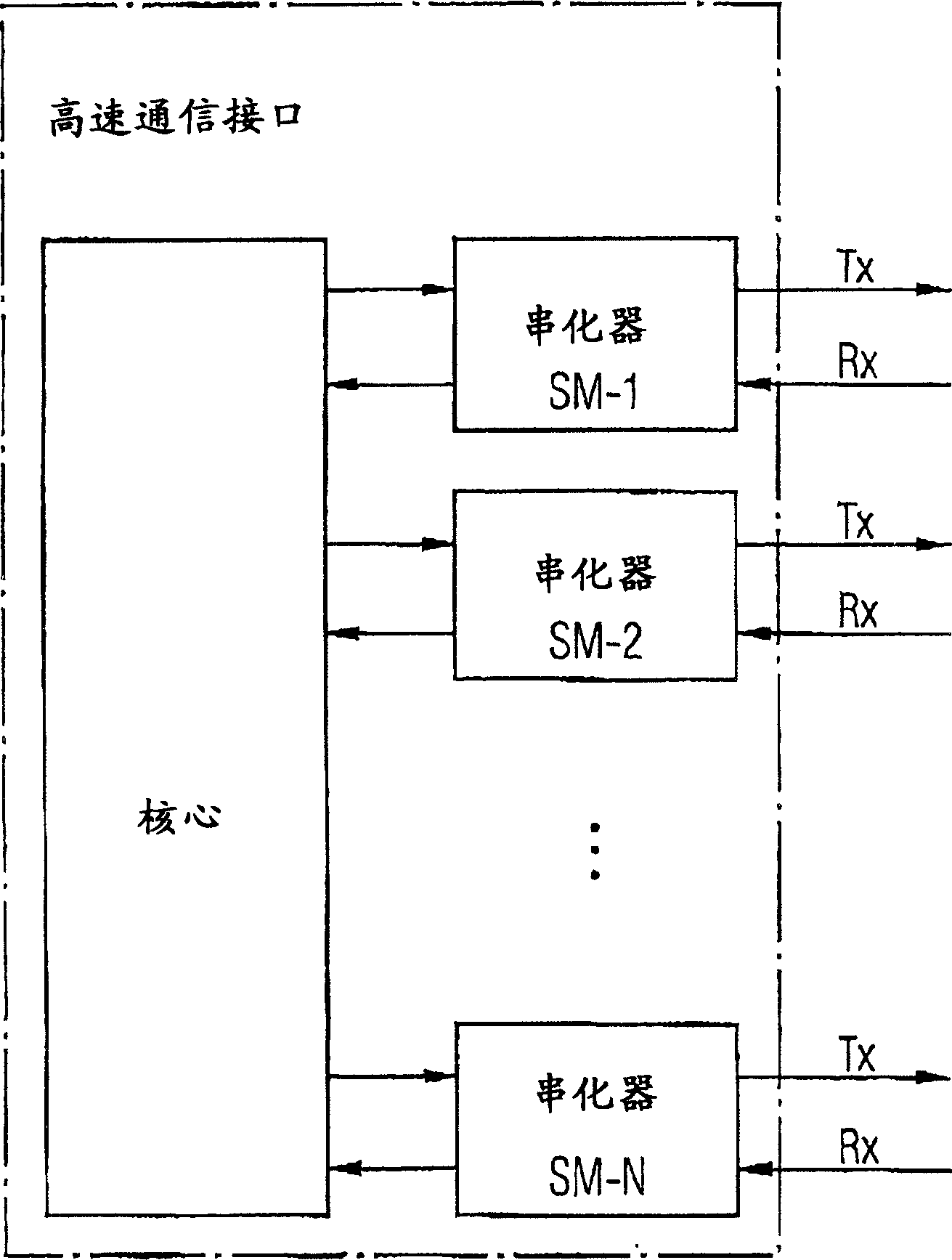

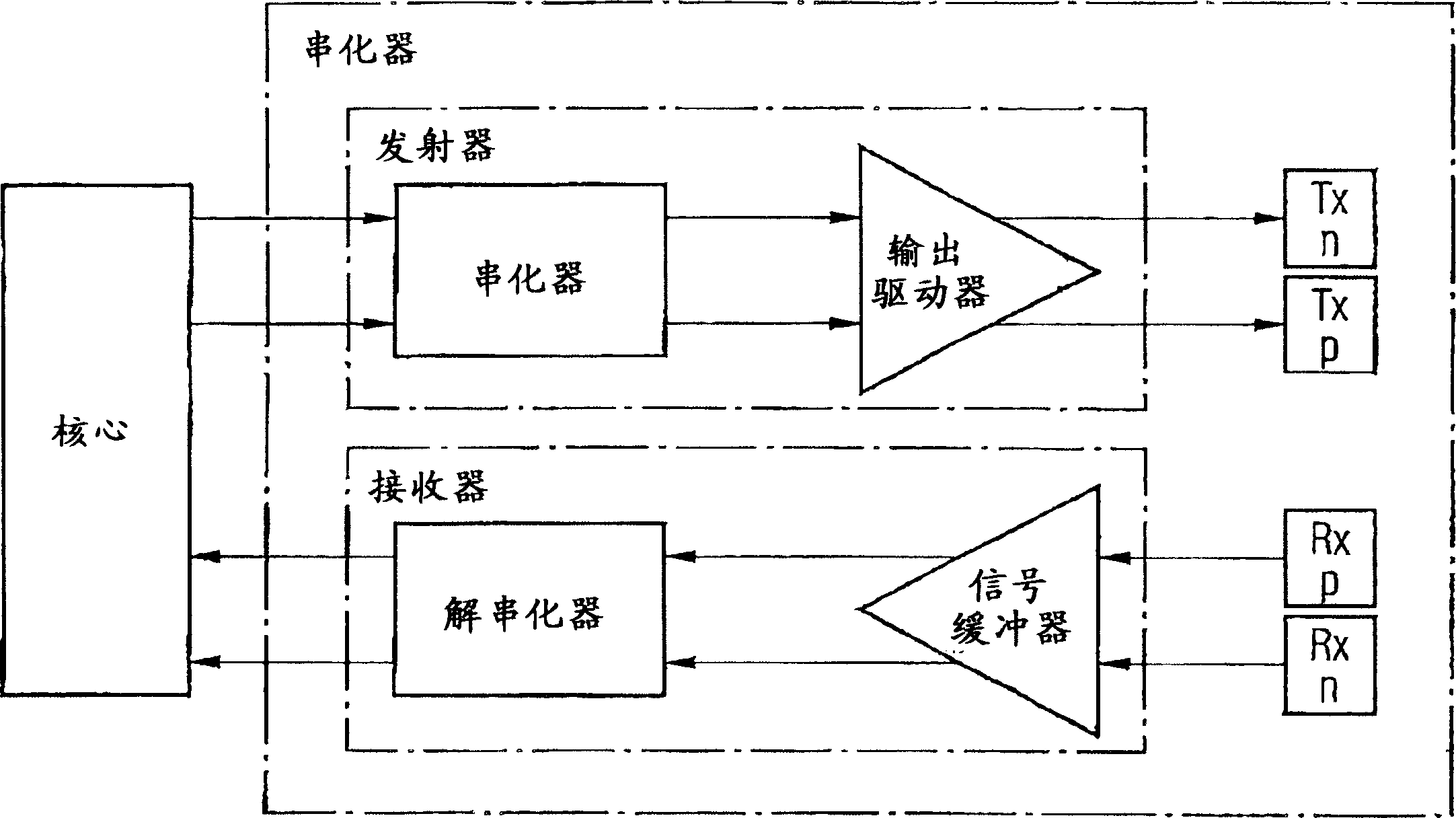

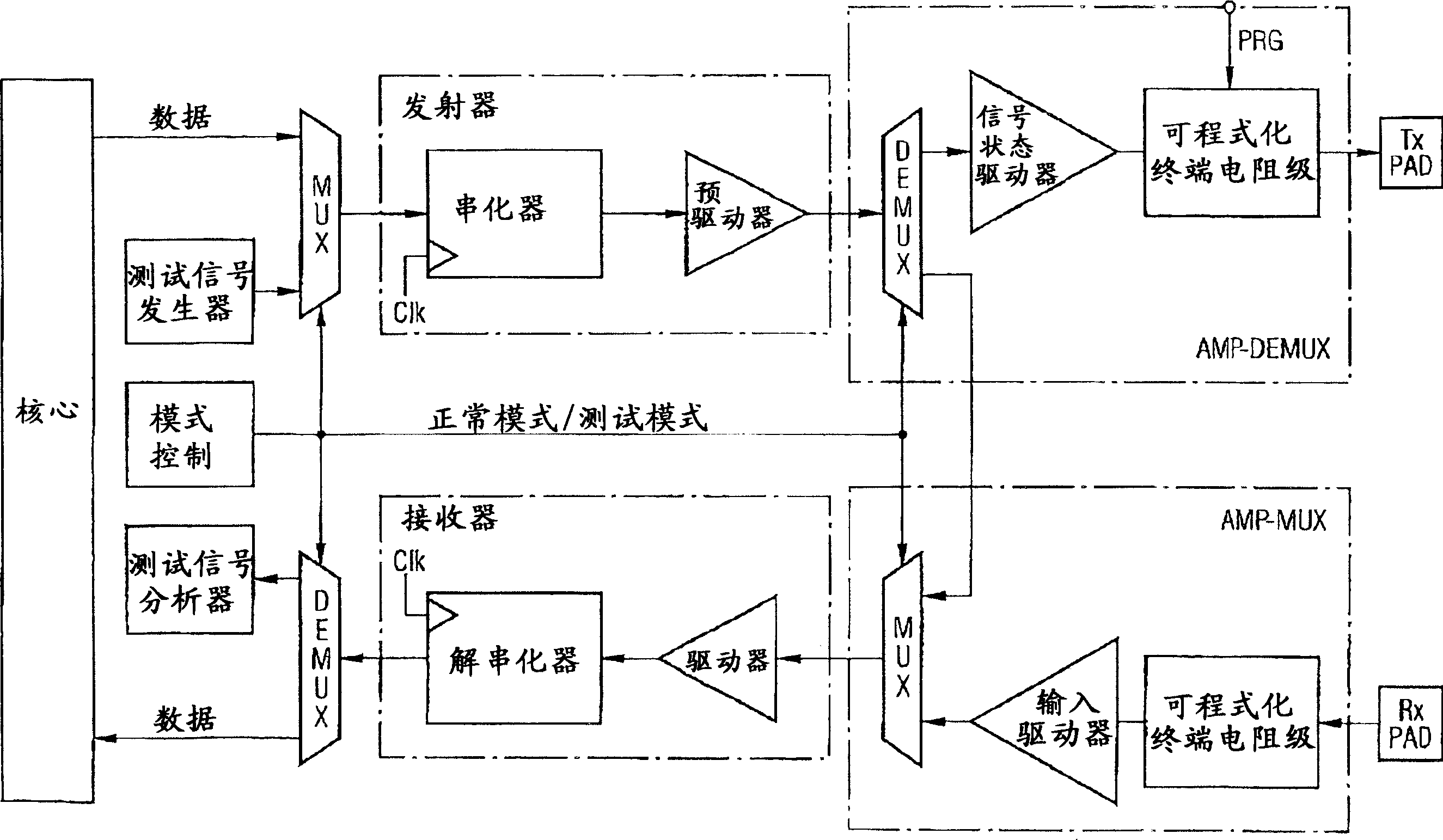

[0058] as Figure 6 Shown is a high-speed data interface 1 according to the present invention, which includes an internal data input 2 and an internal data output 3 to connect the high-speed data interface 1 to a data processing core 4 on an integrated circuit. The integrated circuit contains several high-speed data interfaces 1 . Each high-speed data interface has a transmit data output pin 4 and a receive data input pin 5 to connect the integrated circuit to an external circuit. A serial data stream is transmitted to the external circuit board through the output pin 4 , and a serial data receive stream is received through the receive data pin 5 . Such as Figure 6 In the preferred embodiment shown, the high-speed data interface includes a test signal generator 6 and a test signal analyzer 7 both of which can be controlled by a mode control unit 8 . In another alternative embodiment, the test signal generator 6, the test signal analyzer 7 and the mode control unit 8 are eq...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More